### Journal of the Arkansas Academy of Science

Volume 43 Article 20

1989

# Computer-Controlled Programmable Pulse Generator for a JEOL JNM-FT-1A Radio Frequency Amplifier Section of a Nuclear Magnetic Resonance Spectrometer

William H. Russell University of Arkansas at Little Rock

Roger M. Hawk University of Arkansas at Little Rock

Follow this and additional works at: https://scholarworks.uark.edu/jaas

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Russell, William H. and Hawk, Roger M. (1989) "Computer-Controlled Programmable Pulse Generator for a JEOL JNM-FT-1A Radio Frequency Amplifier Section of a Nuclear Magnetic Resonance Spectrometer," Journal of the Arkansas Academy of Science: Vol. 43, Article 20.

Available at: https://scholarworks.uark.edu/jaas/vol43/iss1/20

This article is available for use under the Creative Commons license: Attribution-NoDerivatives 4.0 International (CC BY-ND 4.0). Users are able to read, download, copy, print, distribute, search, link to the full texts of these articles, or use them for any other lawful purpose, without asking prior permission from the publisher or the author. This Article is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Journal of the Arkansas Academy of Science by an authorized editor of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

## COMPUTER-CONTROLLED PROGRAMMABLE PULSE GENERATOR FOR A JEOL JNM-FT-1A RADIO FREQUENCY AMPLIFIER SECTION OF A NUCLEAR MAGNETIC RESONANCE SPECTROMETER

#### WILLIAM H. RUSSELL and ROGER M. HAWK

University of Arkansas at Little Rock

College of Science and Engineering Technology

Department of Electronics & Instrumentation

2801 South University

Little Rock, AR 72204

#### **ABSTRACT**

A microprocessor controlled programmable pulse generator was specifically designed to interface with the JEOL JNM-FT-1A Radio Frequency (RF) section of a nuclear magnetic resonance (NMR) spectrometer. The programmable pulse generator was programmed and controlled by an IBM compatible computer. Statis rams were utilized as the programmable pulse generator's on board memory which were used to store the pulse sequences. Pulse widths can be programmed from 0.2 microseconds to 14.3 minutes. The JEOL RF section is unique in that it allows the pulse generator to control the phase of the RF transmitted to the NMR probe and whether the sample will be decoupled. These two items set this programmable pulse generator apart from other pulse generators described in the literature and those systems which are commercially available. This programmable pulse generator was constructed to replace the old JEOL thumb wheel controlled pulse generator. Typical 180 degree pulse lengths for the JEOL NMR are approximately 20 microseconds.

#### INTRODUCTION

A microprocessor controlled programmable pulse generator was specifically designed to interface with the JEOL JNM-FT-1A Radio Frequency (RF) section of a nuclear magnetic resonance (NMR) spectrometer. The programmable pulse generator was programmed and controlled by an IBM compatible computer. The programmable pulse generator was designed and constructed to replace the JEOL's thumb wheel controlled pulse generator. The programmable pulse generator had to meet the following requirements: (1) the length of any individual pulse could be varied from 0.2 microseconds to 14.3 minutes in increments of 0.2 microseconds. These times allow the programmable pulse generator to have high resolution and the long pulse widths allow the studying of relaxation times of various nuclei, (2) the pulse generator had to provide two phase shifting control lines that can be changed on every pulse which is an added feature on the JEOL RF section, (3) the pulse generator must provide the capability of running all the standard pulse sequences such as T1, Hahn Spin Echo, Carr-Purcell, and Meiboom-Gill (Becker, 1980), (4) an analog to digital converter (A/D) would have to be triggered by the pulse generator at varying times, (5) the pulse generator had to be computer controlled, (6) simple in design for a wide variety of user expertise, and (7) cost effective.

#### PROCEDURE

Numerous devices were reviewed which included: (1) state-memory machine devices (Sidky et al., 1988), (2) word programmer (Danese et al., 1986), (3) an emitter coupled logic (ELC) (Thomann and Dalton, 1984), and (4) dedicated counter chains. This was a varied list, but none fulfilled the needs of our JEOL RF section. After the review was completed, a decision was made to design and construct the programmable pulse generator in-house. Our design required control lines to: (1) change the phase of the RF generator, (2) control the gated decoupling provided by the JEOL instrument, and (3) a trigger for the A/D converter. The above list of programmable pulse generators did not satisfy these requirements. Thus, a dedicated counter chain pulse generator was chosen as the easiest and the most cost effective method of achieving the desired 0.2 microseconds to 14.3 minutes specified in the design criteria; also, with the aid of static rams and a variety of control logic, all the other requirements were met.

The pulse generator took three separate paths before completion: (1) interface to the IBM compatible computer, (2) interface to the JEOL RF section, and (3) actual pulse generation. The IBM interface consisted of an address decode, data buffers, and data latches. Interface between the generator and the RF section utilized static rams and line drivers. The main component pulse generation combined a dedicated counter chain, static rams, a crystal oscillator, and control logic to achieve the desired pulse sequence.

Simplicity was the goal during the designing stage. Since numerous people would have access to this instrument, training time must be minimized.

#### IBM INTERFACE

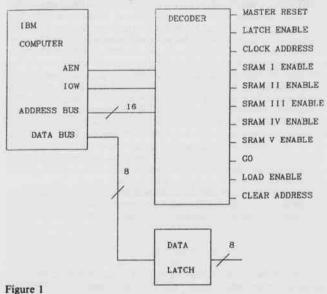

Pulse data were transferred from the computer to the pulse generator since the pulse generator was located in another enclosure a short distance from the computer and the superconducting magnet. An address decoder was constructed using ANDS, NOTS, TRI-STATE BUFFERS, and a FOUR to SIXTEEN BIT DECODER chip. Addresses A0 - A15, control lines I/O Write (IOW), and Address Enable (AEN) were used to decode hexadecimal addresses 380 - 38F. Sixteen control lines were used to latch onto the pulse data, clear the address counters of the static rams, increment the address counters, load the pulse data into the static rams, load pulse data into the counter chain, and to activate the pulse generator.

The first step in transferred data from the computer to the pulse generator was to decode the address bus of the computer (see Figure 1). Addresses hexadecimal 380 - 38F were chosen as valid user addresses for interfacing to the IBM computer (Eggebrecht, 1987). The IBM's computer architecture provides the user with two interfacing signal lines: I/O WRITE (IOW) and ADDRESS ENABLE (AEN). These two signals were used to validate the address and data on the bus. After the address was validated, it was decoded and then used as one of the control lines to control another activity listed above.

The user can write to any hexadecimal port address with the aid of software control. Only hexadecimal addresses 380 - 38F are decoded by the address decoder in Figure 1. The decoder functions only when both IOW and AEN are low, or simply, the decoder waits until the data and the address are valid on the bus before it decodes any address. The address then is decoded and the correct control line corresponding

to the address is switched low. When IOW goes from an active low to an active high, the control line goes high. This action also disables the decoder from functioning until the next address is written to the port.

The address decoder also contains a data latch or a TTL 74LS373 octal "D" transport latch with tri-state output. The data latch on the address board kept the data bus signal lines from becoming too long. The data and address bus was kept as short as possible to minimize any noise and signal timing problems. The data contained in the latch can be used at anytime not just at the computer's clock rate. The data contained in the data latch can be transferred from the IBM interface to any of the pulse generator's static rams. The IBM interface now has decoded the address hexADECIMAL 380 with concomitant control line switching. The data are now ready to be transferred to the pulse programmer.

#### PULSE GENERATOR TO JEOL RF SECTION

The JEOL RF section required a pulse line, two phase lines, a gated or no gated decoupling line, and an analog to digital converter trigger. One static ram was dedicated to provide the output information needed. Line drivers and impedance matching circumvented any problems in transferring short pulses over long distances.

#### **PULSE GENERATOR**

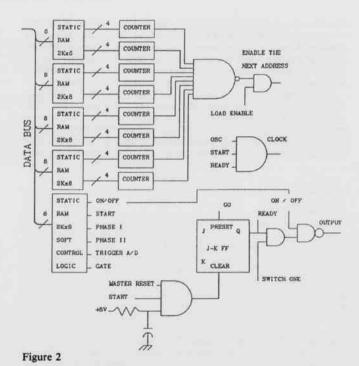

The question was raised, "How do you generate 0.2 microseconds to 14.3 minutes of pulse time in a sequence that also contains phase shifting, A/D triggering, and gated decoupling information?" The answer was to use five static rams (2Kx8) as memory and to dedicate one of the rams as soft control logic for phase shifting, A/D triggering, decoupling, on/off, and start/stop information (see Figure 2). The other four static rams were combined with eight four bit down counters and a 10MHz crystal controlled oscillator. The crystal controlled oscillator is then divided by two to give the user a clock rate of 5MHz or 0.2 microseconds per clock cycle, which allows the counter chain 4.295 X 10E9 counts to time the pulses from 0.2 microseconds to 14.3 minutes. As an added feature the user can change the time per cycle with dip switches, selecting the increment of time needed for a specific experimental resolution.

Two kilobytes were chosen so that the memory was deep enough not to limit the number of pulses that could be programmed by the pulse generator. The only problem with static rams is that they must be addressed to accept data. Three 74LS191 counters were used to generate the addresses for the static rams. Two control lines from the address decoder in the computer were dedicated to clear the address counters and to clock the address counters.

Four-bit presettable synchronous binary up/down counters, 74LS191, were chosen as the dedicated counters. These counters were chosen because they are programmable and they provide a signal line MAX/MIN (pin 12) that goes high when the counter has counted down to zero. The counter's ability to be presettable allows any value to be loaded. The counters were combined in a dedicated chain and the ripple through clock (pin 13) was used to complete the chain's clock requirements.

#### DESCRIPTION OF THE PULSE GENERATOR

Pulse or control data are loaded into the data latch in the computer after the address decoder strobes the address counter clear line thereby zeroing the address of the static rams. Data then are transferred form the computer into one of the corresponding static rams. The address decoder cycles the address clock control line which increments the address counters. The above process is repeated as needed.

The address decoder then toggles the load enable to allow transfer of the first bit of pulse data into the dedicated counter chain. At the end of loading the first bit of pulse data into the counter chain, the load enable control line also clocks the address counters and the next address is presented at the static rams to avoid signal timing problems. The next line pulsed is the "go" control line after which the pulse generator takes control. The go line sets the output on a JK flip-flop that remains high throughout the timing process. The high on the JK enables the master clock to start clocking the counter chain. The start control soft logic line also must be high for the master clock to clock the counter chain. The counter chain has been set in a count down mode.

When the counters count down to zero, the MAX/MIN signal pin goes high. The pulse generator now loads the next sequence of pulse data into the counter chain and clocks the address counters at the end of this cycle. The MAX/MIN lines fall low and the counter chain starts counting down the next sequence. This repeats until the start control soft logic line goes low. The start control soft logic line was programmed by the user as the ending of the pulse sequence. The pulse generator will reset itself and wait until a new pulse sequence is entered.

Three things control whether the pulse is on or off. The JK flip-flop output must be high, the switch SW1 must open, or a high at the AND gate. If any of these are low, the pulse generator's output is forced high or the pulse is "off". The ON/OFF control logic line has final control on if the pulse is on or off. A high forces the pulse generator's output low thereby signaling that the pulse is on; a low has the opposite effect.

#### RESULTS

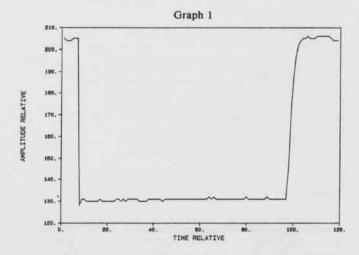

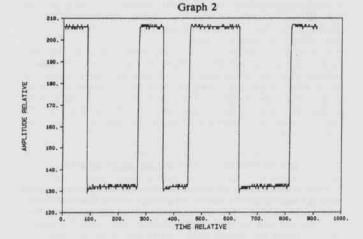

Several pulse sequences were entered and run in the pulse generator to verify that it would indeed satisfy the requirements listed above. The first pulse sequence was a simple one pulse of 10 microseconds. The results were plotted in graph 1 with the time and amplitude on the graph relative. The x-axis on the 10 microsecond pulse was plotted to show fall and rise times of the pulse. As can be seen, the edges are sharp and the slope very steep. The steep slope was a very desirble result. The next pulse sequence entered and run on the pulse generator was a triplet pulse sequence consisting of 20 on, 10 off, 10 on, 20 off, and 20 on (times were microseconds). The results were plotted in graph 2. The triplet sequence timings were accurate and the sequence demonstrated a multiple pulse sequence in the pulse generator. Several variations of the basic pulse sequences were entered into the pulse generator and run. All the sequences were verifying the requirements of the pulse generator. The pulse generator also was able to trigger the analog to digital converter chosen for the JEOL NMR Spectrometer. The triggering of the A/D will be verified in the software section.

Digitalization of the pulse sequences was accomplished with a LeCroy Digital Storage Oscilloscope then transferred via RS232C to a VAX computer and plotted on a Hewlett Packard plotter.

#### CONCLUSION

Soft and hard control logic were used in the timing of the pulse sequences. The counter chains and associated memory were used to control the amount of time until the next address was clocked. In other words, the static ram that contained the soft control logic actually controlled when the pulse was on or off and the counter chains provided the timing data for switching to the next address.

The programmable pulse generator can be modified for use with other NMR spectrometers by selecting the control lines that are unique.

#### LITERATURE CITED

- BECKER, E.D. 1980. High resolution NMR, theory and chemical applications, Academic Press, New York.

- DANESE, G., D. DOTTI, and H.G. JIAN. 1986. Word programmer for NMR, Review of Scientific Instruments 57,7.

- EGGEBRECHT, L.C. 1987. Interfacing to the IBM personal computer. Howard W. Sams & Co., Indianapolis, IN.

- SIDKY, E.Y., E.A. WACHTER, AND T.C. FARRAR. 1988. State-machine digital pulse generator, Review of Scientific Instruments 59,5.

- THOMANN, H., and L.R. DALTON. 1984. Digital pulse programmer for an electron-spin-resonance computer controlled pulsed spectrometer, Review of Scientific Instruments 55,3.