## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2016

# Hardware Trojan Detection via Golden Reference Library Matching

Lucas Weaver University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Hardware Systems Commons, and the Information Security Commons

#### Citation

Weaver, L. (2016). Hardware Trojan Detection via Golden Reference Library Matching. Graduate Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/1460

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

## Hardware Trojan Detection via Golden Reference Library Matching

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Engineering

by

Lucas Weaver John Brown University Bachelor of Science in Engineering, 2014

> May 2016 University of Arkansas

| This thesis is approved for recon | nmendation to the Graduate Council. |

|-----------------------------------|-------------------------------------|

|                                   |                                     |

| Dr. Jia Di                        |                                     |

| Thesis Director                   |                                     |

|                                   |                                     |

| Dr. James Parkerson               | Dr. Dale Thompson                   |

| Committee Member                  | Committee Member                    |

#### **ABSTRACT**

Due to the proliferation of hardware Trojans in third party Intellectual Property (IP) designs, the issue of hardware security has risen to the forefront of computer engineering. Because of the miniscule size yet devastating effects of hardware Trojans, few detection methods have been presented that adequately address this problem facing the hardware industry. One such method with the ability to detect hardware Trojans is *Structural Checking*. This methodology analyzes a soft IP at the register-transfer level to discover malicious inclusions. An extension of this methodology is presented that expands the list of signal functionalities, termed *assets*, in addition to introducing a methodology for matching soft IPs to a functionality category, termed *Golden Reference Library Matching*. Trojan detection methods are introduced that utilize the results of *Golden Reference Library Matching* as well as internal characteristics of the IP. This methodology is verified using benchmarks developed by a trusted third party.

## **ACKNOWLEDGEMENTS**

Many thanks to my advisor, Dr. Jia Di, for his advising on this research. Thanks to Dr. Di's entire lab for everyone's support and mentorship. Particular thanks to Thao Le for her guidance in this research. Thanks also to my remaining committee members, Dr. James Parkerson and Dr. Dale Thompson, for their support of this research.

## **DEDICATION**

To Dad, Mom, Syd, Eli and of course Dublin.

To Dad for giving me the heart and mind of an engineer and to Mom for everything else.

## TABLE OF CONTENTS

| 1. INTRODUCTION                                             | 1  |

|-------------------------------------------------------------|----|

| 1.1 MOTIVATION                                              | 1  |

| 1.2 Objective                                               | 2  |

| 1.3 APPROACH                                                | 2  |

| 1.4 Thesis Organization                                     | 3  |

| 2. BACKGROUND                                               | 4  |

| 2.1 Introduction                                            | 4  |

| 2.2 HARDWARE TROJAN CATEGORIZATION                          | 4  |

| 2.3 HARDWARE TROJAN DETECTION SURVEY                        | 5  |

| 3. METHODOLOGY                                              | 9  |

| 3.1 Introduction                                            | 9  |

| 3.2 ASSETS                                                  | 10 |

| 3.2.1 Internal Assets                                       | 10 |

| 3.2.2 EXTERNAL ASSETS                                       | 12 |

| 3.2.3 ASSET ASSIGNMENT                                      | 15 |

| 3.2.4 ASSET FILTERING                                       | 16 |

| 3.2.5 ASSET OPTIMIZATION                                    | 17 |

| 3.2.6 ASSET PATTERN                                         | 19 |

| 3.2.7. ASSET PATTERN FUNCTIONALITY                          | 21 |

| 3.3 GOLDEN REFERENCE LIBRARY                                | 22 |

| 3.3.1 GOLDEN REFERENCE LIBRARY CREATION AND CHARACTERISTICS | 22 |

| 3.3.2 GOLDEN REFERENCE LIBRARY MATCHING                     | 24 |

| 3.3.2.1 GRL MATCHING ALGORITHM                              | 25 |

| 3.3.2.2 GRL PARTIAL MATCHING ALGORITHM                      | 27 |

|    | 3.3.2.3 FUNCTIONALITY CONSIDERATIONS                           | 30 |

|----|----------------------------------------------------------------|----|

|    | 3.3.2.4 FINAL MATCHING                                         | 31 |

|    | 3.3.3 GOLDEN REFERENCE LIBRARY RESULTS                         | 32 |

|    | 3.4 Trojan Detection Algorithms                                | 33 |

|    | 3.4.1 ASSET PATTERN ALGORITHMS                                 | 34 |

|    | 3.4.2 FUNCTIONALITY ASSIGNMENT ALGORITHMS                      | 36 |

|    | 3.4.2.1 BLACKLISTED FUNCTIONALITIES                            | 37 |

|    | 3.4.2.2 Suspicious Connections                                 | 38 |

|    | 3.4.2.3 FUNCTIONALITY DETECTION WITH ASSET PATTERN RECOGNITION | 39 |

|    | 3.4.3 RTL CHARACTERISTICS                                      | 39 |

|    | 3.4.4 Trojan Detection Report                                  | 43 |

|    | 3.5 GUI IMPLEMENTATION                                         | 44 |

| 4. | RESULTS                                                        | 48 |

|    | 4.1 Introduction                                               |    |

|    | 4.2 GRL MATCHING                                               | 48 |

|    | 4.2.1 Asset Pattern Weighting                                  |    |

|    | 4.2.2 GRL MATCHING EXAMPLE                                     |    |

|    | 4.3 Trojan Detection                                           |    |

|    | 4.3.1 Trust-Hub Benchmarks                                     |    |

|    | 4.3.2 ADDITIONAL TROJAN EXAMPLES                               |    |

|    | 4.3.3 Trojan-Infested Crypto Core Example                      |    |

|    | 4.3.4 Trojan-Infested Microcontroller                          |    |

|    | 4.4 ANALYSIS                                                   |    |

|    |                                                                |    |

| 5. | . CONCLUSION                                                   |    |

|    | 5.1 Summary                                                    | 76 |

| 5.2 FUTURE WORK | 76 |

|-----------------|----|

| REFERENCES      | 78 |

## LIST OF FIGURES

| Figure 1: System Diagram                                       | 9  |

|----------------------------------------------------------------|----|

| Figure 2: Asset Optimization Diagram                           | 19 |

| Figure 3: SPI Module Asset Pattern                             | 21 |

| Figure 4: SPI Module Asset Pattern with Delimiters             | 24 |

| Figure 5: Golden Reference Library Matching High-Level Diagram | 25 |

| Figure 6: Golden Reference Library Match File                  | 33 |

| Figure 7: Trojan Detection High-Level Diagram                  | 34 |

| Figure 8: Trojan Detection Report                              | 43 |

| Figure 9: Trojan Detection Report with Driving Signals.        | 44 |

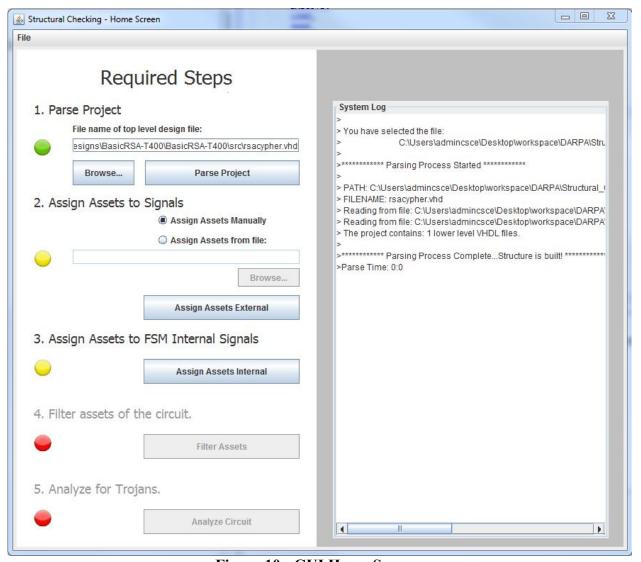

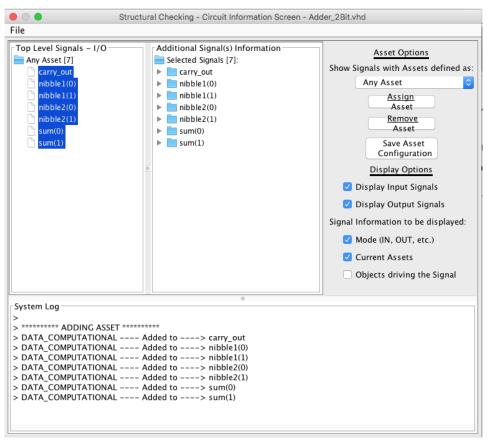

| Figure 10: GUI Home Screen                                     | 45 |

| Figure 11: External Asset Assignment Dialog Box                | 46 |

| Figure 12: First ALU Port Signals                              | 49 |

| Figure 13: Second ALU Port Signals                             | 49 |

| Figure 14: UART I/O Port Signals                               | 51 |

| Figure 15: UART Asset Pattern                                  | 52 |

| Figure 16: Encryption Unit Key Leak VHDL Example               | 54 |

| Figure 17: Encryption Unit Denial of Service VHDL Example      | 55 |

| Figure 18: Time Bomb Counter VHDL Example                      | 56 |

| Figure 19: Encryption Unit Denial of Service VHDL Example      | 56 |

| Figure 20: Counter Instance in Interrupt Unit                  | 61 |

| Figure 21: Interrupt Unit Denial of Service Attack             | 61 |

| Figure 22: Trigger Assignment Attack                           | 62 |

| Figure 23: | Crypto Core Port Signals.            | 64 |

|------------|--------------------------------------|----|

| Figure 24: | AES Time Bomb Trigger                | 64 |

| Figure 25: | AES Time Bomb Key Leakage            | 65 |

| Figure 26: | Microcontroller Primary Port Signals | 67 |

| Figure 27: | ALU Denial of Service                | 68 |

| Figure 28: | Trojan-free Memory FSM               | 69 |

| Figure 29: | Trojan-infested Memory FSM           | 69 |

| Figure 30: | UART Trojan Attack                   | 70 |

| Figure 31: | Trojan Shift Register Port Map       | 71 |

| Figure 32: | VHDL Concurrent Statements           | 73 |

## LIST OF TABLES

| TABLE 1: Internal Assets                         | 10 |

|--------------------------------------------------|----|

| TABLE 2: Data Assets                             | 12 |

| TABLE 3: Timing Assets                           | 12 |

| TABLE 4: System Control Assets                   | 13 |

| TABLE 5: Specific System Control Assets          | 13 |

| TABLE 6: Miscellaneous Assets                    | 14 |

| TABLE 7: Types of Asset Patterns                 | 20 |

| TABLE 8: Functionalities                         | 21 |

| TABLE 9: Asset Pattern Delimiters                | 23 |

| TABLE 10: General Asset Trace Matching Examples  | 26 |

| TABLE 11: Partial Matching Asset Categories      | 28 |

| TABLE 12: Partial Asset Trace Matching Examples  | 29 |

| TABLE 13: Asset Pattern Characteristic Weighting | 32 |

| TABLE 14: Blacklist Functionalities              | 37 |

| TABLE 15: UART Asset Assignment                  | 52 |

| TABLE 16: Microcontroller Asset Assignment       | 67 |

#### 1. INTRODUCTION

#### 1.1 Motivation

Many semiconductor manufacturers in today's world utilize the availability of third party IPs rather than create an entire system in-house. This scenario poses a threat to the system's security as third party IPs are vulnerable to the inclusion of hardware Trojans. Hardware Trojans take the form of unwanted or malicious logic included within a hardware design. The insertion of hardware Trojans allows the attacker to potentially gain possession of valuable information, such as encryption keys, or prevent the correct operation of the design by a denial of service attack. Hardware Trojans are often nearly impossible to detect during the testing and verification process, as they are triggered by a very specific set of circumstances that only the attacker knows.

The subject of hardware Trojan detection is an emerging field with few viable solutions currently in place. The methodologies that have proven to be more successful involve side-channel signal analysis in order to determine whether additional logic has been added to the design. However, a hardware Trojan inserted to a design has the potential to be as small as only a few logic gates and therefore cannot always be revealed through such analysis. Therefore, a more thorough examination of the design is required to reveal the inclusion of hardware Trojans.

Previous work published in [10] has been performed in the area of *Structural Checking*, and this research seeks to extend its capabilities. This method of analyzing soft IPs involves the parsing of a design at the register-transfer level in order to create a representation of the internal structure of the unknown IPs. Then, inclusions of malicious logic are identified by comparing the internal structure of the unknown design to trusted designs as well as examining the internal structure for suspicious connections. This strategy for detecting hardware Trojans has more

advantages than other methodologies currently in use for multiple reasons. First of all, by analyzing the design and detecting Trojans at the register-transfer level, the Trojan threats can be prevented early in the manufacture process. This allows the semiconductor companies to reduce the considerable amount of time and testing costs involved in the Trojan detection method using side-channel signal analysis. Additionally, by parsing the internal structure of a design, the *Structural Checking* methodology can detect smaller inclusions of malicious logic that the side-channel signal analysis cannot.

#### 1.2 Objective

The objective of this research is to significantly increase the number of assets used to represent the role of a signal to provide differences among designs, as well as to create a matching methodology where an unknown design matches to a trusted design from a *Golden Reference Library*. In addition, for scalability, a hardware Trojan detection methodology is developed by using the matching methodology and the characteristics of a soft IP as a specific set of benchmarks.

## 1.3 Approach

Hardware designs, written in VHDL, are represented in the form of a collection of assets used to describe the role of signals. External assets are manually assigned to primary port signals of the design while internal assets are automatically assigned to signals immediately after the parsing of the VHDL design. Following asset assignment, assets are filtered throughout the designs along connections between signals. The result of the filtering process is a collection of assets assigned to each signal, which combine to form an asset pattern. Asset patterns effectively describe the characteristics of those designs, thus they can be used to compare to similar types of designs.

The representations of designs in terms of an asset pattern are collected and utilized in the form of a Golden Reference Library (GRL). The GRL is composed of the asset patterns of trusted designs that have been assigned a functionality. The asset patterns of unknown designs are compared against the asset patterns of trusted designs in the GRL in order to determine the functionality for the unknown design. Following the functionality assignment to an unknown design, the unknown design is analyzed for hardware Trojans. The methodology of hardware Trojan detection leverages multiple aspects to determine whether a Trojan is included in the design. The asset pattern, the functionality matching and the characteristics of the register-transfer level (RTL) code are all utilized in the identification of hardware Trojans.

## 1.4 Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 discusses background information regarding hardware Trojans along with similar research performed in the area of hardware Trojan detection. Chapter 3 presents the unique methodology of hardware Trojan detection, which is the thrust of the thesis. Chapter 4 summarizes the results of this methodology of Trojan detection and provides analysis for the testing results. Finally, chapter 5 summarizes the entire thesis in the form of a conclusion as well as provides potential areas of future work.

#### 2. BACKGROUND

#### 2.1 Introduction

Hardware Trojans must first be evaluated prior to an in-depth analysis of hardware Trojan detection via the *Structural Checking* methodology. Specifically, an introduction to the concept and classification of hardware Trojans is presented in order to understand the threat model for the *Structural Checking* methodology. Additionally, existing Trojan detection methodologies are evaluated in addition to show how the *Structural Checking* methodology advances the capability of hardware Trojan detection.

## 2.2 Hardware Trojan Categorization

Before surveying strategies of hardware Trojan detection, the concept of hardware Trojans needs to be explained. As [1] notes, "hardware Trojans are modifications to original circuitry inserted by adversaries to exploit hardware or to use hardware mechanisms to gain access to data or software running on the chip." As noted previously, many semiconductor companies rely on untrusted third party IPs. Therefore, even if they can ensure the trust of circuitry developed in-house, the third party IPs included in the final design are susceptible to Trojan insertion.

Characteristics exhibited by hardware Trojans allow for clear organization of hardware Trojans. The three main categories of hardware Trojans as identified by [1] and [15] are *physical*, *activation*, and *action*. The first category, *physical*, is broken down into multiple subcategories, some of which are self-explanatory. The first subcategory describes the type of Trojan, whether it involved gates added to the design or if gates were modified. The remaining categories are self-explanatory and consist of the size, distribution and structure of the hardware Trojan [15].

The second major category, *activation*, is also described as the trigger for the hardware Trojan. This category is further divided into *externally-activated* and *internally-activated* Trojans. In the case of *externally-activated* Trojans, the adversary alone knows a very specific input sequence resulting in the Trojan activation. *Internally-activated* Trojans are manifested in multiple, self-explanatory forms, such as *always-on* and *condition-based* [15].

The final major category, *action*, is also described as the payload of the hardware Trojan [15]. The malicious characteristics exhibited by the payloads of Trojans are further divided into three categories—*modify-function*, *modify-specification*, and *transmit-information* [15]. The first subcategory, *modify-function*, consists of attacks focused on augmenting the logic of the circuit in order to change its intended behavior. The *modify-specification* subcategory describes attacks intended to adjust certain properties of the circuit, such as clock frequency. The final subcategory, *transmit-information*, involves attacks focused on leaking important information to an attacker.

The *Structural Checking* methodology analyzes designs at the RTL and therefore is limited to certain types of hardware Trojans. Specifically, detecting Trojans in the physical characteristics subcategory is outside the scope of the *Structural Checking* methodology. Therefore, the hardware Trojans detected by the *Structural Checking* methodology are Trojans found at the RTL within the action and activation categories.

### 2.3 Hardware Trojan Detection Survey

Many Trojan detection methods have been proposed in previous research. The methodologies proposed range from Trojan activation techniques to side-channel analysis. This section gives a brief overview of the major Trojan detection methods.

A major technique utilized in the detection of hardware Trojans involves the analysis of side-channel characteristics of the circuit. Two of the major side-channel characteristics of a circuit to be analyzed in the detection of hardware Trojans are power consumption and current. A foundational work in the development of power analysis for the purposes of hardware Trojan detection is presented in [17]. By establishing a power signature for a particular type of circuit, the researchers found that hardware Trojans could be detected by identifying significant deviations from the power signature. The research performed in [20] similarly focused on side-channel characteristics, but limited the analysis to the current in isolated portions of the circuit. An additional side-channel characteristic measured the register-to-register path delay. The research performed in [18] establishes a technique for using the path delay measurement to verify the absence of a hardware Trojan. All of these methodologies achieved success in identifying larger hardware Trojans, but found difficulty in detecting smaller Trojans.

Another prominent methodology of Trojan detection involves the integration of sensors to available space of a design layout. The research performed by [2] proposes the sensors measuring the delays as a form of "self-authentication" to ensure that a design is Trojan-free. This is very similar to the research performed by [3] using sensors to measure the variability of path delays, although this research does not explicitly discuss using the on-chip sensors to detect hardware Trojans. Measurements performed by a ring oscillator network measuring power consumption on-chip coupled with statistical analysis allow the researchers in [4] to identify malicious inclusions to hardware designs. The methodologies of using on-chip monitors yield positive results in identifying specific types of Trojans, such as Trojans described by their physical characteristics.

An additional strategy of Trojan detection involves the purposeful activation of hardware Trojans. By performing various activation techniques, one can find the designs with Trojan inclusions by observing the Trojan payload. The researchers in [12] employ a probabilistic approach to Trojan activation through applying randomized test sequences to activate hardware Trojans. Another strategy of Trojan activation, as presented in [21], analyzes the circuit to determine nets that are rarely activated and in turn using test vectors that activate those same nets. A final strategy of Trojan activation found in [14] involves narrowing down the area of potential Trojan inclusion to a specific region and testing that region thoroughly for Trojans. While each of these methodologies achieved reasonable success, the strategy of Trojan activation has limitations since Trojans often require a very unique and complex activation sequence.

Another category of Trojan detection involves providing greater trust to third party IPs. The first of these methodologies, presented in [5], utilize functional vectors to remove trusted signals from consideration in order to isolate Trojans to a specific region of the design. The researchers in [6] employ an assortment of methodologies to identify hardware Trojans in third party IPs, such as formal verification and sequential ATPG. Finally, the research performed in [7] proposes a Design-for-Trojan-Test methodology that reduces the likelihood of Trojan insertion by making potential Trojan trigger sequences difficult to implement. While the research presented in this category yielded positive results, there are limitations to the number and size of Trojans that they can detect.

Additional methodologies focus on the security of third party IPs from a software analysis perspective rather than from a testing and verification perspective. The research performed by [8] compares functionally similar IP blocks to determine if malicious logic is present. The procedure by which this methodology compares the two IP blocks borrows from

the concept of loop unrolling in order to represent the internal logic states of both designs.

Another methodology presented in [9] uses statistical analysis to assign values to signals based on their vulnerability to Trojan insertion. The vulnerability values are determined by the level of weight assigned to a statement as well as the observability of the statement. In doing so, a value for the level of trust of an entire IP block can be determined. While the research performed by both parties produce positive initial results, more advances must occur for these to be viable options for hardware Trojan detection.

As discussed previously, the methodology of hardware Trojan detection employed in this thesis is derived from the methodology of *Structural Checking* as originally presented in [19]. Previous work had been done in the area of modeling hardware threats in [16] and subsequently incorporated into the *Structural Checking* methodology presented in [19]. Research performed in [10] advanced the *Structural Checking* methodology through the creation of a software tool performing VHDL parsing and expression analysis as well as an initial conceptualization of hardware Trojan detection from a *Structural Checking* perspective. This research advances the *Structural Checking* methodology further to include a more robust collection of assets, a Golden Reference Library for functionality matching and hardware Trojan detection capability.

#### 3. METHODOLOGY

#### 3.1 Introduction

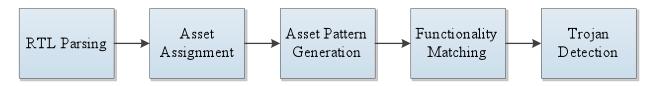

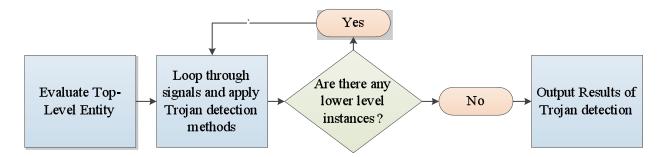

The Trojan detection methodology presented in this research is derived from the *Structural Checking* methodology developed in [10]. This methodology analyzes hardware designs at the register-transfer level (RTL) in order to determine the presence of hardware Trojans in the form of malicious logic. A high-level system diagram for this methodology can be found in Figure 1 below.

Figure 1: System Diagram

The design in question, written in VHDL, is first parsed in order to create a hierarchical structure of the data paths within the design. The VHDL parser was available as an open-source parser [22] and has been developed and implemented in a previous project as noted in [10]. Next, the primary port signals of the design are assigned assets, which denote the role of the signal within the design. The collection of assets assigned to primary port signals was greatly increased from the amount of assets found in the previous *Structural Checking* project. The assigned assets are filtered throughout the circuit through direct connections of the primary inputs and primary outputs determined by the VHDL parsing. Depending on the assets and their locations, the design is categorized based on its functionality by comparing it to trusted RTL designs in a Golden Reference Library (GRL). The GRL feature for categorizing designs was a completely new innovation added to the *Structural Checking* project. Finally, potential hardware Trojans within the design are identified by analyzing the results of the GRL categorization as well as characteristics of the RTL code. The Trojan detection process was also a new addition to

the project from the previous *Structural Checking* methodology. This entire methodology has been implemented and tested in the form of a graphical user interface that allows users to analyze a potentially malicious design for hardware Trojans. The tool produces output reports that present the results of hardware Trojan detection for user readability.

#### 3.2 Assets

The concept of an asset was previously introduced in [10]. As [10] explains, an asset describes the purpose of a signal within a design. This concept is a foundation of Trojan detection, as it allows for signals to be represented in terms of a collection of assets. A signal's collection of assets will become important in later sections when dealing with Trojan detection.

Assets can be divided into two broad categories. The first category is termed <u>internal</u> assets. Primary port signals and internal signals both receive internal assets via automatic assignments. These assets are termed internal due to the fact that they refer to the way the signals are internally used within a system. The other category of assets is termed <u>external</u> assets. External assets are manually assigned to the primary port signals of a design.

#### 3.2.1 Internal Assets

The first category of assets, internal assets, includes a set of assets that are automatically assigned to all signals within the designs. The assignment of internal assets occurs following the parsing of the RTL code by first looping through the code and searching for all logical expressions. The signals used in each logical expression are then identified and assigned an internal asset based on the role that it plays within the expression. Table 1 below shows a list of the 16 internal assets that have been developed along with a description of each asset.

**TABLE 1: Internal Assets**

| Asset             | Description                                     |

|-------------------|-------------------------------------------------|

| PROCESS_SENSITIVE | Assigned to a signal contained within a process |

|                   | sensitivity list.                               |

**TABLE 1: Internal Assets (Cont.)**

| Asset                       | Description                                          |

|-----------------------------|------------------------------------------------------|

| PROCESS_OPERATION_SENSITIVE | Assigned to a signal being modified within a process |

|                             | statement.                                           |

| CONDITIONAL_DRIVING         | Assigned to a signal contained within a conditional  |

|                             | statement.                                           |

| CONDITIONAL_DRIVEN          | Assigned to a signal being modified within a         |

|                             | conditional statement.                               |

| CONCURRENT_DRIVING          | Assigned to a signal driving another signal via a    |

|                             | concurrent statement.                                |

| CONCURRENT_DRIVEN           | Assigned to a signal being driven by another signal  |

|                             | via a concurrent statement.                          |

| CC_OPERATION_OR             | Assigned to a signal being driven by a concurrent    |

|                             | statement performing an OR operation.                |

| CC_OPERATION_AND            | Assigned to a signal being driven by a concurrent    |

|                             | statement performing an AND operation.               |

| CC_OPERATION_XOR            | Assigned to a signal being driven by a concurrent    |

|                             | statement performing an XOR operation.               |

| CC_OPERATION_NOR            | Assigned to a signal being driven by a concurrent    |

|                             | statement performing a NOR operation.                |

| CC_OPERATION_NAND           | Assigned to a signal being driven by a concurrent    |

|                             | statement performing a NAND operation.               |

| CC_OPERATION_XNOR           | Assigned to a signal being driven by a concurrent    |

|                             | statement performing an XNOR operation.              |

| CC_OPERATION_NOT            | Assigned to a signal being driven by a concurrent    |

|                             | statement performing a NOT operation.                |

| CC_OPERATION_A_ADD          | Assigned to a signal being driven by a concurrent    |

|                             | statement performing an addition operation.          |

| CC_OPERATION_MULT           | Assigned to a signal being driven by a concurrent    |

|                             | statement performing a multiplication operation.     |

| CC_OPERATION_SENSITIVE      | Assigned to a signal being driven by a concurrent    |

|                             | statement using another type of logic than the types |

|                             | previously listed.                                   |

The assets above can be broken down into three categories. The first category deals with assets assigned to signals used in process statements. Certain internal assets are assigned to signals based on whether the signal appears in a process sensitivity list or whether it is used inside the process itself. The second category deals with assets assigned to signals used in conditional statements. Similarly to the assets dealing with process statements, conditional assets can be assigned to signals found within a conditional statement or to signals being

modified within a conditional statement. Finally, numerous assets are assigned to signals being used within concurrent statements. These assets are assigned based on the logic used within the concurrent statement. As a signal can be used in multiple types of expressions in RTL code, multiple internal assets can be assigned to a signal.

#### 3.2.2 External Assets

The second category of assets is external assets, and these assets are manually assigned to primary port signals. As opposed to internal assets that describe how a signal is used internally in the RTL code, external assets describe how a primary port signal is used. There are a total of 51 external assets that are distributed among several broad categories.

The first category contains assets describing data signals. Table 2 below shows the assets within this category along with the definition of the specific asset.

**TABLE 2: Data Assets**

| Asset              | Description                                                      |

|--------------------|------------------------------------------------------------------|

| DATA_COMPUTATIONAL | Assigned to data signals within ALUs, adder, multipliers, etc.   |

| DATA MEMORY        | Assigned to data signals being stored in memory.                 |

| DATA_PERIPHERAL    | Assigned to data signals being used by peripheral units.         |

| DATA_COMMUNICATION | Assigned to data signals being used for communication            |

|                    | purposes by communication units.                                 |

| DATA_ENCRYPTION    | Assigned to data signals being used being encrypted by           |

|                    | encryption units.                                                |

| DATA_SENSITIVE     | This is the most general of the data assets and can be assigned  |

|                    | to signals containing data that does not fit any other category. |

The second category consists of assets related to the timing of a system. Table 3 below shows the assets within this category along with the definition of the specific asset.

**TABLE 3: Timing Assets**

| Asset            | Description                                                    |

|------------------|----------------------------------------------------------------|

| SYSTEM_TIMING    | Assigned to the primary clock signal.                          |

| SUBSYSTEM_TIMING | Assigned to a subsystem clock signal.                          |

| STATUS           | Assigned to a signal indicating the status of the system.      |

| DONE             | Assigned to a signal indicating that an operation is finished. |

| HOLD             | Assigned to a signal indicating to hold an operation.          |

| READY            | Assigned to a signal indicating that an operation is ready.    |

**TABLE 3: Timing Assets (Cont.)**

| Asset         | Description                                                      |

|---------------|------------------------------------------------------------------|

| BUSY          | Assigned to a signal indicating that an operation is busy.       |

| COUNT         | Assigned to a signal used as a counter.                          |

| WAIT          | Assigned to a signal indicating that an operation must wait.     |

| TIMER_CONTROL | Assigned to a signal controlling a timer.                        |

| CLOCK CONTROL | Assigned to a signal controlling the primary or subsystem clock. |

The next category involves assets assigned to signals used for system control. Table 4 below shows the assets within this category along with the definition of the specific asset.

**TABLE 4: System Control Assets**

| Asset          | Description                                                           |

|----------------|-----------------------------------------------------------------------|

| SET            | Assigned to a signal used to set a value.                             |

| RESET          | Assigned to a signal used to reset a value.                           |

| READ           | Assigned to a signal used to perform a read operation.                |

| WRITE          | Assigned to a signal used to perform a write operation.               |

| SELECT         | Assigned to a signal used to perform a select operation.              |

| EXECUTE        | Assigned to a signal indicating that an operation is to be executed.  |

| LOAD           | Assigned to a signal indicating that a value is to be loaded.         |

| MODE           | Assigned to a signal indicating the mode of an operation.             |

| ENABLE         | Assigned to a signal used to perform an enable operation.             |

| HANDSHAKING    | Assigned to a signal used in communication by way of a                |

|                | handshaking operation.                                                |

| SHIFT          | Assigned to a signal indicating that a shift operation is to occur.   |

| INSTRUCTION    | Assigned to a signal used as an instruction. This is the most general |

|                | form of this asset and should only be used when a more specific       |

|                | asset does not describe the signal.                                   |

| SYSTEM_CONTROL | Assigned to a signal that is used in system control. This is the most |

|                | general system control asset and should only be used when a more      |

|                | specific asset does not describe the signal.                          |

The next category of assets is a subset of the previous category of system control assets.

These assets are specific to a certain type of subsystem. Table 5 below shows the assets within this category along with the definition of the specific asset.

**TABLE 5: Specific System Control Assets**

| Tibble of Specific System Control 1255005 |                                                          |  |

|-------------------------------------------|----------------------------------------------------------|--|

| Asset                                     | Description                                              |  |

| MEMORY_OP                                 | Assigned to a signal used to perform an operation within |  |

|                                           | a memory subsystem.                                      |  |

| DATA_OP                                   | Assigned to a signal used to perform an operation within |  |

|                                           | a subsystem dealing with data.                           |  |

**TABLE 5: Specific System Control Assets (Cont.)**

| Asset                  | Description                                                |

|------------------------|------------------------------------------------------------|

| INTERRUPT_OP           | Assigned to a signal used to perform an operation within   |

|                        | an interrupt unit subsystem.                               |

| PROGRAM_COUNTER_OP     | Assigned to a signal used to perform an operation within   |

|                        | a program counter.                                         |

| INTERRUPT_CONTROL      | Assigned to a signal used as system control within an      |

|                        | interrupt unit subsystem.                                  |

| PERIPHERAL_CONTROL     | Assigned to a signal used as system control within a       |

|                        | peripheral subsystem.                                      |

| REGISTER_FILE_CONTROL  | Assigned to a signal used as system control within a       |

|                        | register file subsystem.                                   |

| COMMUNICATION_CONTROL  | Assigned to a signal used as system control within a       |

|                        | communication subsystem.                                   |

| COMMUNICATION_PROTOCOL | Assigned to a signal used to handle a protocol within a    |

|                        | communication subsystem.                                   |

| COMMUNICATION_STATUS   | Assigned to a signal indicating the status of an operation |

|                        | within a communication subsystem.                          |

| INTERRUPT              | Assigned to a signal used to handle an interrupt requests. |

The final category of assets is simply a miscellaneous category. These assets do not clearly fit into any one category and are therefore grouped together in the miscellaneous category. Table 6 below shows the assets within this category along with the definition of the specific asset.

**TABLE 6: Miscellaneous Assets**

| Asset              | Description                                                        |

|--------------------|--------------------------------------------------------------------|

| CRITICAL           | Assigned to an asset that could lead to harm if an attacker gained |

|                    | possession of it.                                                  |

| COMPONENT          | Assigned to an asset that refers to another component of a         |

|                    | system.                                                            |

| ADDRESS_SENSITIVE  | Assigned to an asset that describes the address used in a memory   |

|                    | subsystem.                                                         |

| CONSTANT           | Assigned to a signal that describes a value to be used as a        |

|                    | constant.                                                          |

| KEY                | Assigned to a signal used as an encryption key in an encryption    |

|                    | unit.                                                              |

| REGISTER           | Assigned to a signal used to handle data to be used in a register  |

|                    | file subsystem.                                                    |

| PROGRAM_COUNTER    | Assigned to a signal used as the value being manipulated within    |

|                    | a program counter.                                                 |

| ERROR_HANDLING     | Assigned to a signal that performs error handling.                 |

| EXCEPTION_HANDLING | Assigned to a signal that performs error handling.                 |

**TABLE 6: Miscellaneous Assets (Cont.)**

| Asset | Description                                           |

|-------|-------------------------------------------------------|

| STATE | Assigned to a signal that tracks the state of system. |

### 3.2.3 Asset Assignment

As mentioned in the previous section, users assign external assets to the primary port signals of a design. This requires the user to understand how the signal of a design is used in the system. Oftentimes, the choice of external asset is very simple, as there is a direct correlation between the external asset to be assigned and the signal it is assigned to. However, there are cases in which the user must deduce the external asset to be used based on the closest match to the functionality of the signal. Therefore, several rules should be considered when assigning assets.

First of all, the most important rule in assigning external assets is that the most specific asset appropriately describing the signal should be assigned. As the descriptions of the assets in the previous section show, there are certain assets that are general in nature, such as

DATA\_SENSITIVE and SYSTEM\_CONTROL. These assets should only be assigned in the case that no other assets best describe the functionality of a signal. For instance, when considering the assignment of an asset to a data signal in an ALU, the more specific external asset

DATA\_COMPUTATIONAL should be used rather than the general DATA\_SENSITIVE asset.

Additionally, if there is not an exact asset describing a signal's role within the system but there is an asset functionally similar to the signal under consideration, then that asset should be assigned.

For example, when considering the asset assignment of a clear signal, the functionally similar asset, RESET, should be assigned to the clear signal.

The second rule to consider when assigning assets involves the number of assets assigned to a signal. Primary port signals can have multiple assets assigned to the same signal in the case

the signal cannot be appropriately described by a single asset. For example, a signal may be used to perform *read/write* operations. In that case, both the *READ* and *WRITE* assets should be assigned to the signal in order to appropriately describe its functionality. However, the ideal scenario is that a single asset can be assigned that appropriately describes the functionality of that signal. This is especially important when considering the first rule above stating that the most specific asset to describe a signal should be used. For example, if a signal is a data signal within a communication unit, only the *DATA\_COMMUNICATION* asset should be assigned, rather than additionally assigning another data asset that may only partially describe the functionality of the signal.

The final rule to consider when assigning assets involves asset assignment for system specific assets. This rule is similar to the first in that it requires a user to assign the most specific asset possible to describe a signal. More specifically, this rule involves assigning assets specific to a type of system if the functionality of the system is known. For example, if an asset is used as an instruction within an ALU, the general *INSTRUCTION* asset should not be assigned. Instead, the more system-specific asset *DATA\_OP* should be assigned. Even in the case that an asset describes the functionality of the signal, the system specific asset should be used. For example, if a *read* signal is being analyzed in memory unit, the *MEMORY\_OP* asset should be chosen rather than the *READ* asset. The assignment of system-specific assets aids in the future step of functionality matching.

### 3.2.4 Asset Filtering

Following the VHDL parsing and assignment of assets, the next step in the process is to filter the assets throughout the circuit. This involves passing the assets previously assigned to the primary port signals to lower level signals based on the internal connections of the circuit.

For example, if a primary input port signal directly drives an internal signal via a concurrent statement, the internal signal would receive the assets assigned to the input signal. Filtering occurs both from input to output and vice versa, meaning that assets can be passed from input to output and from output to input. This process is repeated recursively until every connection within the circuit has been reached. At this point, every signal within the circuit has been populated with assets that describe all possible functionalities of the signal. The information necessary to filter the assets is collected during the VHDL parsing. The development of the methodology and implementation of asset filtering was previously described by [10].

## 3.2.5 Asset Optimization

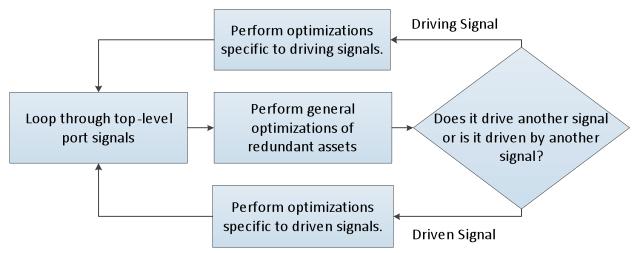

An additional step following the filtering of assets through the circuit, termed asset optimization, occurs in order to ensure a precise asset pattern. Asset optimization involves the analysis of each individual port signal's external and internal assets to ensure that there are no redundant assets. As past analysis of asset filtering has shown, asset patterns for large designs can be extremely large, resulting in every signal essentially having the exact same asset pattern. Asset optimization corrects this issue by removing filtered assets that do not actually contribute to the functionality of the circuit.

Asset optimization is only performed on the primary port signals of the circuit that have been assigned assets. The internal assets of these signals are then analyzed to determine if the signal in question is driving another signal or being driven by a signal. Certain assets are removed based on whether the signal is driving another signal or being driven by another signal. In the case of the signal being driven by another signal and the original signal contains a data asset, the system control assets relevant to data operations are removed. For example, if a data signal assigned a *DATA MEMORY* asset has received a *MEMORY OP* asset during the filtering

process, the *MEMORY\_OP* asset is removed from the collection of assets assigned to the data signal. Conversely, in the case that a signal is driving another signal and the original signal contains a system control asset, the data assets relevant to the system control operations are removed. For example, if a system control signal assigned a *MEMORY\_OP* asset has received a *DATA\_MEMORY* asset during the filtering process, the *DATA\_MEMORY* asset is removed from the collection of assets assigned to the system control signal. This process allows the true functionality of the signal to represented with assets rather than allowing the filtered assets to distort the functionality of the signal.

There are also certain optimizations that are performed regardless of whether the signal is driving or being driven by another signal. As mentioned previously there are certain assets that are very general in nature, such as *DATA\_SENSITIVE* and *SYSTEM\_CONTROL*. In the case where one of these assets is present and other more specific assets are present, the general assets are removed. For example, in the case that a signal is assigned a *DATA\_COMPUTATIONAL* asset and a *DATA\_SENSITIVE* asset is filtered to the signal, the *DATA\_SENSITIVE* asset will be removed from the signal's collection of assets. However, it is important to note that only filtered assets can be removed through optimization while the assigned assets are permanent. The entire process of asset optimization is illustrated in Figure 2 below.

Figure 2: Asset Optimization Diagram

#### 3.2.6 Asset Pattern

The results of the filtering and optimizing of assets is termed an asset pattern. Asset patterns describe the system in terms of a collection of internal and external assets that have been filtered throughout the circuit. This is accomplished by listing the internal and external assets that have been assigned to individual signals. The collection of assets assigned to a specific signal is termed an asset trace. The collection of asset traces forms an asset pattern for a system.

Asset traces originate from the external assets that are manually assigned to a signal and the internal assets that are automatically assigned to a signal. Once the assets have been filtered throughout the circuit, each individual signal contains a collection of assets that have been assigned initially as well as assets that have been filtered to the signal. Each asset within the asset trace is unique. This means that the asset traces do not repeat assets even in the case that an asset has been both assigned and filtered to the signal. Additionally, each signal has both an external asset trace as well as an internal asset trace. An example of an external asset trace found in a communication unit can be seen below:

[DATA COMMUNICATION, COMMUNICATION PROTOCOL]

An example of an internal asset trace can be seen below:

## [CONDITIONAL DRIVEN, PROCESS SENSITIVE, CONDITIONAL DRIVING]

Both of these examples show the list of external and internal assets that were both assigned and filtered to a signal.

Asset traces are grouped into six separate categories based on the type of assets being assigned and the type of signals the assets are being assigned to. The two types of assets are internal and external, while the types of signals that the assets are being assigned to are primary input/output signals and internal signals. Therefore, the categories can be seen in Table 7 below:

**TABLE 7: Types of Asset Patterns**

| Asset Pattern Type                        | Description                                         |

|-------------------------------------------|-----------------------------------------------------|

| input port signal external asset pattern  | Collection of external asset traces assigned to top |

|                                           | level input port signals                            |

| output port signal external asset pattern | Collection of external asset traces assigned to top |

|                                           | level output port signals                           |

| internal signal external asset pattern    | Collection of external asset traces assigned to     |

|                                           | internal signals                                    |

| input port signal internal asset pattern  | Collection of internal asset traces assigned to top |

|                                           | level input port signals                            |

| output port signal internal asset pattern | Collection of internal asset traces assigned to top |

|                                           | level output port signals                           |

| internal signal internal asset pattern    | Collection of internal asset traces assigned to     |

|                                           | internal port signals                               |

The combination of these six sets of asset traces forms the asset pattern of a single circuit. The asset pattern represents the unique combination of assets that are used to describe a circuit design. An example of an asset pattern of a SPI module can be seen below in Figure 3.

```

[SYSTEM TIMING]

[PROCESS SENSITIVE, CONDITIONAL DRIVING]

[RESET]

[COMMUNICATION CONTROL]

[CONDITIONAL DRIVING]

[READ, WRITE]

[ADDRESS SENSITIVE]

[DATA COMMUNICATION, COMMUNICATION PROTOCOL]

[DATA COMMUNICATION]

[CONDITIONAL DRIVEN]

[INTERRUPT]

[SUBSYSTEM TIMING]

[CONCURRENT DRIVEN]

[COMMUNICATION PROTOCOL, DATA COMMUNICATION]

[COMMUNICATION CONTROL]

[COMMUNICATION PROTOCOL]

[PROCESS SENSITIVE, CONDITIONAL DRIVING, CONDITIONAL DRIVEN]

[COMMUNICATION PROTOCOL, DATA COMMUNICATION]

```

Figure 3: SPI Module Asset Pattern

As is indicated in this asset pattern, many of the assets are related to communication. It could then be inferred that the circuit described by this asset pattern belongs to the category of communication without the previous knowledge that it is a SPI module. This fact will be used in future sections to match asset patterns to functionalities.

#### 3.2.7. Asset Pattern Functionality

Following the creation of an asset pattern for a system, a functionality is assigned to the design. As the name implies, the functionality assignment is intended to effectively describe the purpose of the design. Table 8 below lists the types of functionalities that the design could be assigned to.

**TABLE 8: Functionalities**

| Functionality   | Description                                                  |

|-----------------|--------------------------------------------------------------|

| SHIFT_REGISTER  | Assigned to a circuit being used to shift data in and out.   |

| INTERRUPT_UNIT  | Assigned to a circuit handling interrupt requests.           |

| COMMUNICATION   | Assigned to a circuit handling communication.                |

| ENCRYPTION_UNIT | Assigned to a circuit being used to encrypt or decrypt data. |

**TABLE 8: Functionalities (Cont.)**

| Functionality      | Description                                                       |

|--------------------|-------------------------------------------------------------------|

| COMPUTATIONAL      | Assigned to a circuit being used to manipulate data, such as an   |

|                    | ALU, adder or multiplier                                          |

| TIMING             | Assigned to a circuit responsible for controlling the timing of a |

|                    | system.                                                           |

| CONTROL_GENERATION | Assigned to a circuit used to handle system control.              |

| REGISTER FILE      | Assigned to a circuit used to store data                          |

| PERIPHERAL         | Assigned to a circuit handling peripherals other than             |

|                    | communication.                                                    |

| DECODER_ENCODER    | Assigned to a circuit used to encode or decode data.              |

As the list indicates, many functionalities have direct correlations to assets that were presented previously. This was intentional, as this aids in determining the functionality of a particular design.

## 3.3 Golden Reference Library

The asset patterns generated by asset assignment and filtering are essential in the analysis of unknown designs. A Golden Reference Library (GRL) is formed by obtaining asset patterns from trusted IPs that in turn can be used to compare against unknown IPs to determine their level of trust. The GRL contains files with characteristics of the individual designs that have been deemed to be trusted. The unknown design is then compared to the GRL designs and assigned a functionality based on the closest GRL design match. The resulting data is outputted in user-readable format.

### 3.3.1 Golden Reference Library Creation and Characteristics

The Golden Reference Library was created by first obtaining trusted designs for each type of functionality. The asset pattern for each of the trusted designs are generated and added to the GRL to be used as the golden references. Due to the fact that these are the basis of matching unknown designs, a sufficient amount of trusted designs for each category must be chosen in order to guarantee that an unknown design could match sufficiently to a trusted design or else be

deemed untrusted. Obtaining designs for the GRL is an ongoing process as more trusted designs can always be added to represent more types of designs. However, the designs currently present in the GRL are sufficient to match many unknown designs.

The trusted designs were obtained through numerous sources. The main source of designs was the website OpenCores [13], an open-source repository for hardware designs. Many of their trusted designs were incorporated into the GRL. The remaining trusted designs were either collected from additional online repositories or were simply created during the course of the project. One potential issue that arose when creating the GRL is that there are numerous ways to implement designs of a specific category, and it is impossible to find and implement all possible designs. However, this issue is addressed by the addition of assets specific to a functionality as well as allowing the GRL to be constantly updated with new designs. The specific assets allow designs to be matched with functionalities closely related to those assets.

GRL files contain several important characteristics used in the matching process. The main information used in this process is the complete asset pattern for that design. In order for the asset pattern to be parsed by the tool, certain delimiters were used to identify the specific portions of the asset pattern. The delimiters for each type of asset pattern can be seen in Table 9 below.

**TABLE 9: Asset Pattern Delimiters**

| Asset Pattern Type                        | Delimiter |

|-------------------------------------------|-----------|

| input port signal external asset pattern  | >         |

| output port signal external asset pattern | <         |

| internal signal external asset pattern    | /         |

| input port signal internal asset pattern  | >*        |

| output port signal internal asset pattern | <*        |

| internal signal internal asset pattern    | /*        |

As the table shows, the addition of the symbol '\*' indicates that an asset pattern is an internal asset pattern, while the absence of that symbol indicates that it is an external asset

pattern. An example asset pattern with delimiters inserted can be seen in Figure 4 below. This figure is the same asset pattern as the SPI module from before with delimiters.

```

>/SYSTEM TIMING]

>*[PROCESS SENSITIVE, CONDITIONAL DRIVING]

>/RESET1

>[COMMUNICATION CONTROL]

>*/CONDITIONAL DRIVING

>[READ, WRITE]

>[ADDRESS SENSITIVE]

>[DATA COMMUNICATION, COMMUNICATION PROTOCOL]

<[DATA COMMUNICATION]

<*[CONDITIONAL DRIVEN]

<[INTERRUPT]

</subsystem timing)</pre>

<*/CONCURRENT DRIVEN]

<[COMMUNICATION PROTOCOL, DATA COMMUNICATION]

<[COMMUNICATION CONTROL]

<[COMMUNICATION PROTOCOL]

/*[PROCESS SENSITIVE, CONDITIONAL DRIVING, CONDITIONAL DRIVEN]

/[COMMUNICATION PROTOCOL, DATA COMMUNICATION]

```

**Figure 4: SPI Module Asset Pattern with Delimiters**

The asset patterns generated by the asset filtering process are stored in files termed *GRL* files with a ".grl" extension. Each GRL file is stored under the Golden Reference Library directory. This directory is located such that it is easily found in order to be used later in the GRL matching process. If additional trusted designs were generated by the asset filtering process, the associated GRL file could simply be added to this directory.

### 3.3.2 Golden Reference Library Matching

The creation of the Golden Reference Library is used as the basis for matching unknown designs to a functionality. Functionality matching is necessary for determining the level of trust to be assigned to the unknown design. Therefore, a matching methodology was developed that allows the unknown design to be matched to a known design in the GRL. The asset patterns of the trusted designs found within GRL files provided a characteristic to be used for comparison

between the unknown designs and the trusted designs. However, many factors of the asset patterns must be analyzed in order to create an algorithm for matching. This section discusses the various characteristics of the GRL matching algorithm along with examples of how portions of unknown designs would be matched to trusted designs in the GRL.

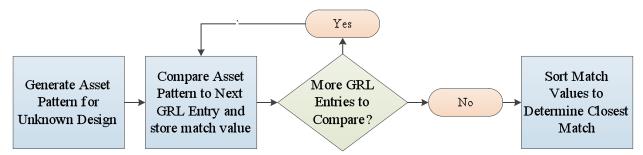

### 3.3.2.1 GRL Matching Algorithm

As discussed in previous sections, the asset pattern generated by asset filtering contains six separate characteristics based on the type of signal (input and output port signals and internal signals) and the type of asset (internal and external). Therefore, during the matching of asset patterns, each characteristic is analyzed and matched to a potential design. As Figure 5 below indicates, the beginning of the matching process is to loop through each entry of the GRL in order to compare the characteristics of each GRL entry to the unknown design. Each characteristic is analyzed individually and assigned a percentage match that is then used to determine the total match.

Figure 5: Golden Reference Library Matching High-Level Diagram

The match percentage of each individual characteristic is contained in a hash map using the name of the GRL entry as the key and the match percentage as the value. There are six hash maps as there are six characteristics used in the matching process. The values are obtained while looping through the GRL entries and comparing the individual asset pattern characteristics of the GRL entry to the unknown design. The matching of the individual characteristics is essentially

an intersection of sets in order to determine the percentage of assets contained within the unknown design with respect to each GRL entry.

While looping through the GRL entries, the individual asset traces of the asset pattern characteristics are taken individually and compared to the asset traces of the same asset pattern characteristics of the unknown design. For example, the first asset pattern characteristic of the GRL entry, the input port signal external asset pattern, is broken up into individual asset traces and compared to the input port signal external asset traces of the unknown designs. Each asset trace is looped through individually in order to find the largest match between asset traces. The largest match is found by finding the intersection of the two asset traces (many examples are given below for clarification). Once the largest match is assigned to the individual asset traces, they are added together and divided by the total number of asset traces in order to find the asset pattern percentage match. This is summarized in the Equation 1 below.

In order to clarify the matching process, several examples have been given in Table 10.

These examples show how each asset trace of an unknown design matches to an asset trace of a GRL entry.

**TABLE 10: General Asset Trace Matching Examples**

| Case | <b>Unknown Design Asset Traces</b> | GRL Entry Asset Traces                      | Match |

|------|------------------------------------|---------------------------------------------|-------|

| 1    | DATA_MEMORY, CRITICAL              | DATA_ MEMORY,<br>CRITICAL                   | 100%  |

| 2    | DATA_MEMORY, CRITICAL              | SYSTEM_CONTROL                              | 0%    |

| 3    | DATA_ MEMORY, CRITICAL             | DATA_MEMORY,<br>CRITICAL,<br>SYSTEM_CONTROL | 67%   |

| 4    | DATA_ MEMORY,<br>SYSTEM CONTROL    | DATA_ MEMORY,<br>SYSTEM_TIMING              | 50%   |

Case 1 in Table 10 gives the simple scenario that both asset traces are identical. In this case, the match is clearly 100%. Case 2 is also a simple example showing that the match will be 0% when the asset traces have no intersection. Case 3 shows the scenario in which the two asset traces intersect on two assets; however, the GRL entry contains a third asset not found in the unknown design asset trace, causing the final match to be 67%. Finally, Case 4 considers the scenario in which one asset is shared while the other asset is different. This case yields a 50% asset trace match. If these asset traces where combined to form an asset pattern for a specific asset pattern characteristic, the final match for that characteristic could be easily determined by averaging the percentages listed. Therefore, the asset pattern characteristic match would be 54 25%

In certain instances, one of the characteristics of a design may be empty. For example, if a design does not contain internal signals, then there will be no assets assigned to internal signals and those asset pattern characteristics will be empty. In the case that both the GRL entry and the unknown design both have the same characteristic as empty, the hash map containing the match percentages is marked with a -1 value indicating that this characteristic will be left out of the final matching.

### 3.3.2.2 GRL Partial Matching Algorithm

In order to gain a more precise indication of the match between asset traces, an algorithm for partially matching asset traces was developed. This algorithm takes into account the fact that there is occasional overlap among assets and therefore there must be a way to assign a percentage match to these assets greater than zero. For example, when matching the *DATA\_SENSITIVE* asset to the *DATA\_COMPUTATIONAL* asset using the normal intersection set matching, the result would be a 0% match. However, due to the fact that these assets are

similar in nature, the matching percentage should be greater than 0%. This is the problem addressed by the partial matching algorithm.

The partial matching algorithm is implemented during the matching of asset traces. Using general intersection set matching, the assets are analyzed and assigned a value by determining whether or not the assets found within one set matches the assets found in the other set. Instead, partial matching runs each individual asset through a method that analyzes the asset to determine if it is part of a subset of similar assets. The set of similar assets are then searched for within the asset trace intended for matching to determine whether or not any are found. In the case that another asset that is similar in nature to the asset in question is found in the other asset trace, a 50% match is assigned for that individual asset. This 50% match is then factored in with the remaining assets that are a part of the asset trace.

The partial matching algorithm uses certain subsets of assets to determine whether or not an asset should receive a partial match. These subsets of assets can be found in Table 11 below.

**TABLE 11: Partial Matching Asset Categories**

| SYSTEM_CONTROL | DATA_SENSITIVE  | INSTRUCTION  | STATUS |

|----------------|-----------------|--------------|--------|

| SELECT         | DATA_           | DATA_OP      | READY  |

|                | ENCRYPTION      |              |        |

| READ           | DATA_           | MEMORY_OP    | DONE   |

|                | COMMUNICATION   |              |        |

| WRITE          | DATA_           | PROGRAM_     | HOLD   |

|                | COMPUTATIONAL   | COUNTER_OP   |        |

| INSTRUCTION    | DATA_MEMORY     | INTERRUPT_OP | STATUS |

|                |                 |              |        |

| MODE           | DATA_PERIPHERAL |              | BUSY   |

| SET            |                 |              | WAIT   |

| RESET          |                 |              |        |

| ENABLE         |                 |              |        |

| EXECUTE        |                 |              |        |

| HANDSHAKING    |                 |              |        |

| LOAD           |                 |              |        |

**TABLE 11: Partial Matching Asset Categories (Cont.)**

| SYSTEM_CONTROL            | DATA_SENSITIVE | INSTRUCTION | STATUS |

|---------------------------|----------------|-------------|--------|

| SHIFT                     |                |             |        |

| INTERRUPT_<br>CONTROL     |                |             |        |

| PERIPHERAL_<br>CONTROL    |                |             |        |

| REGISTER_FILE_<br>CONTROL |                |             |        |

| COMMUNICATION_<br>CONTROL |                |             |        |

| CLOCK_CONTROL             |                |             |        |

| TIMER_CONTROL             |                |             |        |

As the table shows, there are four categories of assets that can be partially matched. The four categories are represented by the assets listed in the top row of each column. The partial matching algorithm consists of first identifying whether one of the assets listed in the top row is contained within either the GRL entry asset trace or the unknown design asset trace. If one of the assets is found in either asset trace, the other asset trace is parsed for one of the assets in the column of the original asset found. If one of those assets is found, a 50% match is assigned for this set of assets.

In order to clarify the partial matching algorithm, several examples are shown in Table 12 below, listing the two asset traces along with a partial match percentage.

**TABLE 12: Partial Asset Trace Matching Examples**

| Case | Unknown Design Asset Traces     | GRL Entry Asset Traces | Match |

|------|---------------------------------|------------------------|-------|

| 1    | DATA_MEMORY                     | DATA_ SENSITIVE        | 50%   |

| 2    | DATA_MEMORY, DATA_<br>SENSITIVE | DATA_ SENSITIVE        | 50%   |

| 3    | $DATA\_MEMORY$                  | DATA_COMPUTATIONAL     | 0%    |

| 4    | ENABLE, SET                     | SET, SYSTEM CONTROL    | 75%   |

| 5    | RESET                           | SET, SYSTEM_CONTROL    | 25%   |

Case 1 provides the simple example of two assets that can be partially matched at 50%. The matching scenario in Case 2 shows that the two *DATA\_SENSITIVE* assets are matched at

100%; however, since the unknown design contains an additional asset, *DATA\_MEMORY*, the final match is 50%. It is important to note with this example that since the *DATA\_SENSITIVE* asset in the GRL entry was matched with the *DATA\_SENSITIVE* asset in the unknown design, it could not be partially matched with the *DATA\_MEMORY* asset. Case 3 shows that even though the two assets are data assets, they are not partially matched. For a partial match to occur, one of the assets had to be a *DATA\_SENSITIVE* asset. Case 4 describes a scenario in which the *SET* assets are matched at 100% while the *ENABLE* and *SYSTEM\_CONTROL* assets are matched at 50%, resulting in a final match of 75%. Finally, Case 5 describes a scenario in which the *SYSTEM\_CONTROL* asset is partially matched to the *RESET* asset at 50%. Since the GRL entry has one additional asset, the final match is 25%.

# 3.3.2.3 Functionality Considerations

In addition to the partial asset matching, an algorithm that considers the functionality of the GRL entries was developed in order to take advantage of the precise nature of many of the assets. The external assets of the unknown design can give an indication as to what functionality that design may be. By searching for the functionality-specific assets assigned to the unknown design, the algorithm takes into consideration the GRL entries with that same functionality and weights them greater than the entries without that functionality assignment.

As mentioned, this aids in the final matching of the unknown design to a functionality. During the analysis of individual asset pattern characteristics, the algorithm recognizes whether or not one of these assets is contained within the asset pattern characteristic. In the case that a functionality-specific asset is present, all of the GRL entries with the corresponding functionality are given a weight of 1.5 in order to give these entries precedence. Therefore, the match percentage for only that characteristic will be multiplied by 1.5. For example, in the case that the

input port signal external asset pattern contains a *DATA\_ENCRYPTION* asset, the match percentage for the input port signal external asset pattern of all GRL entries of functionality type *encryption unit* are multiplied by 1.5. However, the other asset pattern characteristics do not necessarily receive the multiplier unless other functionality-specific assets are also contained in those characteristics.

## 3.3.2.4 Final Matching

Once each individual asset pattern characteristic hash map has been filled with values representing the individual asset pattern matches, the final asset pattern match for each GRL entry can be determined. Each individual asset pattern characteristic is taken into account during the final asset pattern match; however, not all of the asset pattern characteristics are weighted equally. There are several reasons for this. The most important reason is that certain designs can be implemented in several different ways. For example, the internal implementation of one ALU may be completely different from that of another ALU even though they accomplish the same purposes. However, both of the ALUs will have similar I/O port signal external assets. Therefore, the I/O port signal external assets should be weighted higher than the internal characteristics of the design, including the internal signal assets. An additional reason for having larger weight for I/O port signal external assets is that the internal assets of multiples designs are similar to each other even if the designs have different functionalities.

Now that it has been established that not all asset pattern characteristics should be weighted the same, the next question to address is the amount of weight that each characteristic should be given. After performing extensive testing in order to determine the proper weight, the values seen in Table 13 below were finalized.

**TABLE 13: Asset Pattern Characteristic Weighting**

| TITELE 101 IISSOUT WOOTH CHAILWOOTS TO THE STORY |        |

|--------------------------------------------------|--------|

| Asset Pattern Characteristic                     | Weight |

| input port signal external asset pattern         | 3×     |

| output port signal external asset pattern        | 3×     |

| internal signal external asset pattern           | 1×     |

| input port signal internal asset pattern         | 1×     |

| output port signal internal asset pattern        | 1×     |

| internal signal internal asset pattern           | 1×     |

As the table shows, the port signal external asset patterns receive the largest weight, three times larger than any other characteristic (the weighting of the asset pattern characteristics and the testing results will be discussed further in subsequent sections). Once each individual asset characteristic values have been determined, the above weighting is applied to each characteristic, producing the final match value for each GRL entry to the unknown design. As mentioned previously, certain designs do not contain every asset pattern characteristic. Therefore, during the final matching these characteristics are simply omitted and the remaining characteristics are used to match an unknown design to the GRL entry.

# 3.3.3 Golden Reference Library Results