University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

5-2017

# A Hybrid Partially Reconfigurable Overlay Supporting Just-In-Time Assembly of Custom Accelerators on FPGAs

Zeyad Tariq Aklah University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Hardware Systems Commons, and the Software Engineering Commons

## Citation

Aklah, Z. T. (2017). A Hybrid Partially Reconfigurable Overlay Supporting Just-In-Time Assembly of Custom Accelerators on FPGAs. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/1928

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact uarepos@uark.edu.

## A Hybrid Partially Reconfigurable Overlay Supporting Just-In-Time Assembly of Custom Accelerators on FPGAs

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

by

Zeyad Tariq Aklah University of Basrah Bachelor of Science in Computer Engineering, 2002 University of Basrah Master of Science in Computer Engineering, 2008

## May 2017 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council

Dr. David Andrews Dissertation Director

Dr. John Gauch Committee Member

Dr. Michael Gashler Committee Member Dr. Xuan Shi Committee Member

## Abstract

The state of the art in design and development flows for FPGAs are not sufficiently mature to allow programmers to implement their applications through traditional software development flows. The stipulation of synthesis as well as the requirement of background knowledge on the FPGAs' low-level physical hardware structure are major challenges that prevent programmers from using FPGAs. The reconfigurable computing community is seeking solutions to raise the level of design abstraction at which programmers must operate, and move the synthesis process out of the programmers' path through the use of overlays. A recent approach, Just-In-Time Assembly (JITA), was proposed that enables hardware accelerators to be assembled at runtime, all from within a traditional software compilation flow. The JITA approach presents a promising path to constructing hardware designs on FPGAs using pre-synthesized parallel programming patterns, but suffers from two major limitations. First, all variant programming patterns must be pre-synthesized. Second, conditional operations are not supported.

In this thesis, I present a new reconfigurable overlay, URUK, that overcomes the two limitations imposed by the JITA approach. Similar to the original JITA approach, the proposed URUK overlay allows hardware accelerators to be constructed on FPGAs through software compilation flows. To this basic capability, URUK adds additional support to enable the assembly of presynthesized fine-grained computational operators to be assembled within the FPGA.

This thesis provides analysis of URUK from three different perspectives; utilization, performance, and productivity. The analysis includes comparisons against High-Level Synthesis (HLS) and the state of the art approach to creating static overlays. The tradeoffs conclude that URUK can achieve approximately equivalent performance for algebra operations compared to HLS custom accelerators, which are designed with simple experience on FPGAs. Further, URUK shows a high degree of flexibility for runtime placement and routing of the primitive operations. The analysis shows how this flexibility can be leveraged to reduce communication overhead among tiles, compared to traditional static overlays. The results also show URUK can enable software programmers without any hardware skills to create hardware accelerators at productivity levels consistent with software development and compilation.

©2017 by Zeyad Tariq Aklah All Rights Reserved

## Acknowledgements

I would like to thank my academic advisor, Professor David Andrews, for his extraordinary care and support. His guidance helped me throughout the research and the writing of this thesis.

Beside my advisor, I would like to extend my thanks to my thesis committee: Professor John Gauch, Dr. Gashler, and Dr. Shi.

Additionally, I would like to thank the HCED-Iraq for providing me the opportunity to pursue my Ph.D.

My sincere thanks also goes to the staff of the Sponsored Students Program at the University of Arkansas, especially to the director of the program, Gloria Flores Passmore, and the program coordinator, Catherine Cunningham.

Last but not least, I would like to thank my family for their everlasting support.

## Contents

| 1 | Inte       | roduction 1                                                 |

|---|------------|-------------------------------------------------------------|

|   |            | 1.0.1 Compilation Challenges                                |

|   |            | 1.0.2 Technical Challenges                                  |

|   | 1.1        | Just-In-Time Assembly                                       |

|   | 1.2        | Thesis Statement                                            |

|   |            | 1.2.1Thesis Contributions and Organization                  |

| 2 | D1         | kground 9                                                   |

| 2 |            |                                                             |

|   | 2.1<br>2.2 |                                                             |

|   |            |                                                             |

|   | 2.3        | High Level Synthesis    13      Overlage    14              |

|   | 2.4        | Overlays                                                    |

|   |            | 2.4.1 JIT FPGA                                              |

|   |            | 2.4.2 Virtual FPGAs                                         |

|   |            | 2.4.3 ZUMA:                                                 |

|   |            | 2.4.4 Intermediate Fabrics                                  |

|   |            | 2.4.5 Synthesis-Free JIT Compilation:                       |

|   |            | 2.4.6 SCGRA                                                 |

|   |            | 2.4.7 QuickDough                                            |

|   |            | 2.4.8 QUKU:                                                 |

|   |            | 2.4.9 Soft Processors                                       |

|   | 2.5        | Domain Specific Languages                                   |

|   |            | 2.5.1 FSMLang:                                              |

|   |            | 2.5.2 Chisel:                                               |

|   |            | 2.5.3 Aspen:                                                |

|   |            | 2.5.4 Lime:                                                 |

|   |            | 2.5.5 Delite:                                               |

| 3 | Tuet       | -In-Time Assembly 23                                        |

| 5 | 3.1        | Introduction                                                |

|   | 3.2        | JITA Approach                                               |

|   | 3.2<br>3.3 | ••                                                          |

|   | 3.3<br>3.4 | 1                                                           |

|   | 5.4        |                                                             |

|   |            |                                                             |

|   |            | e                                                           |

|   | 25         | 3.4.3 Local Memory                                          |

|   | 3.5        | Run Time Interpreter         29           Summer         24 |

|   | 3.6        | Summary                                                     |

| 4 | Pror       | posed Solution 37                                           |

|   | 4.1        | Introduction                                                |

|   | 4.2        | Hardware Design Flow                                        |

|   |            | 5                                                           |

|   | 4.3               | URUK Architecture                                                                                                                                                                                       | 40                                |

|---|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|   |                   | 4.3.1 Tile Structure                                                                                                                                                                                    | 42                                |

|   |                   | 4.3.2 PR Regions                                                                                                                                                                                        | 42                                |

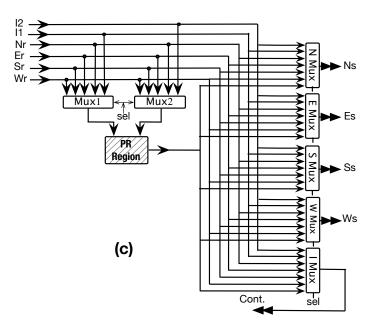

|   |                   | 4.3.3 Configurable Switches:                                                                                                                                                                            | 43                                |

|   |                   | 4.3.4 Memory Interface                                                                                                                                                                                  | 45                                |

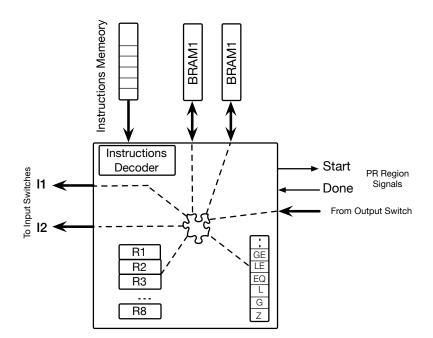

|   |                   | 4.3.5 Tile Controller                                                                                                                                                                                   | 45                                |

|   |                   | 4.3.6 Tile Instruction Sets                                                                                                                                                                             | 46                                |

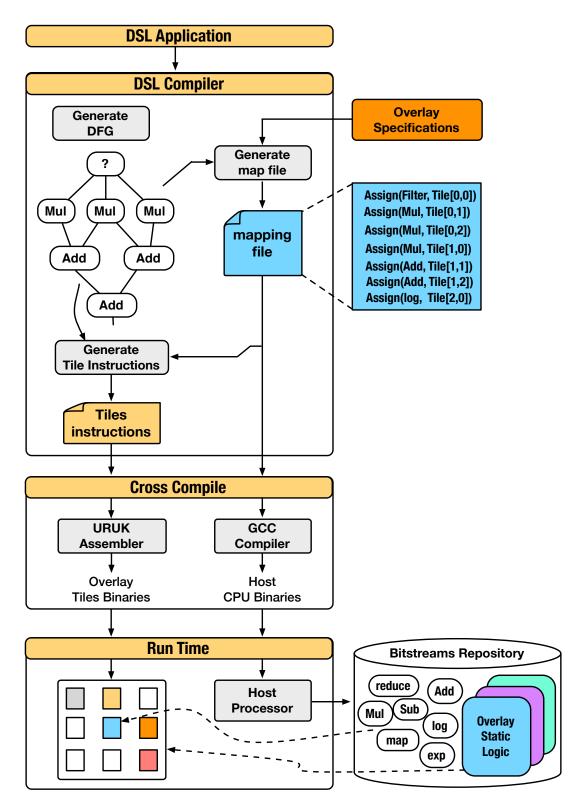

|   | 4.4               | Design Automation                                                                                                                                                                                       | 50                                |

| 5 | URI               | UK Compilation Flow                                                                                                                                                                                     | 51                                |

|   | 5.1               | •                                                                                                                                                                                                       | 51                                |

|   | 5.2               |                                                                                                                                                                                                         | 54                                |

|   | 5.3               |                                                                                                                                                                                                         | 54                                |

|   | 5.4               | 1                                                                                                                                                                                                       | 54                                |

|   | 5.5               |                                                                                                                                                                                                         | 55                                |

|   |                   | I                                                                                                                                                                                                       | 55                                |

|   |                   |                                                                                                                                                                                                         | 56                                |

|   | 5.6               | 1                                                                                                                                                                                                       | 57                                |

|   | 5.7               |                                                                                                                                                                                                         | 60                                |

| 6 | Eva               | luation                                                                                                                                                                                                 | 66                                |

| Ū | 6.1               |                                                                                                                                                                                                         | 66                                |

|   | 6.2               |                                                                                                                                                                                                         | 67                                |

|   | 6.3               | 1                                                                                                                                                                                                       | 68                                |

|   | 6.4               | 1                                                                                                                                                                                                       | 70                                |

|   | 6.5               |                                                                                                                                                                                                         | 74                                |

|   | 0.0               |                                                                                                                                                                                                         | 77                                |

|   |                   |                                                                                                                                                                                                         | 81                                |

|   |                   | 1                                                                                                                                                                                                       | 82                                |

|   | 6.6               | 1                                                                                                                                                                                                       | 84                                |

|   |                   | 5                                                                                                                                                                                                       |                                   |

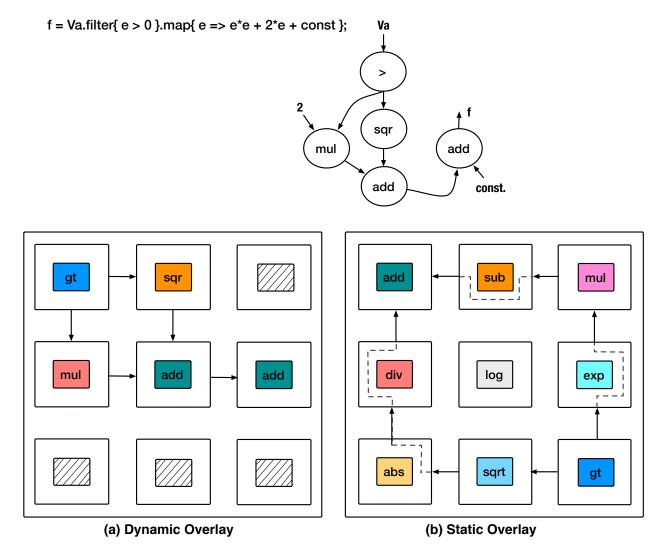

|   | 6.7               | Dynamic vs. Static                                                                                                                                                                                      | 85                                |

|   | 6.7               | 5                                                                                                                                                                                                       |                                   |

|   | 6.7               | 6.7.1 Area                                                                                                                                                                                              | 88                                |

|   | 6.7               | 6.7.1       Area       Area       Area         6.7.2       Routing Data       Area       Area                                                                                                           |                                   |

| 7 |                   | 6.7.1       Area       Area       Area         6.7.2       Routing Data       Area       Area         6.7.3       Parallelism       Area       Area                                                     | 88<br>88<br>89                    |

| 7 | Con               | 6.7.1       Area       Area       Area         6.7.2       Routing Data       Area       Area         6.7.3       Parallelism       Area       Area         clusion       Area       Area       Area    | 88<br>88<br>89<br><b>90</b>       |

| 7 |                   | 6.7.1       Area       Area       Area         6.7.2       Routing Data       Area       Area         6.7.3       Parallelism       Area       Area         clusion       Summary       Area       Area | 88<br>88<br>89<br><b>90</b><br>90 |

|   | <b>Con</b><br>7.1 | 6.7.1       Area                                                                                                                                                                                        | 88<br>88<br>89<br><b>90</b>       |

## List of Figures

| 1.1 | General Processors vs. FPGAs Compilation Flows.                              | 3  |

|-----|------------------------------------------------------------------------------|----|

| 2.1 | General FPGA Architecture.                                                   | 11 |

| 2.2 | General CGRA Architecture.                                                   | 12 |

| 3.1 | Design Approach.                                                             | 24 |

| 3.2 | Compiler Flow and VAM Call Generation.                                       | 26 |

| 3.3 | $3 \times 3$ Tile Array and Interconnect Network                             | 27 |

| 3.4 | Switch Routing.                                                              | 28 |

| 3.5 | VAM Run Time Interpreter Configuration Steps.                                | 30 |

| 3.6 | Design Portability with JIT                                                  | 31 |

| 3.7 | VAM Run Time Interpreter Configuration Steps For Inner Product.              | 33 |

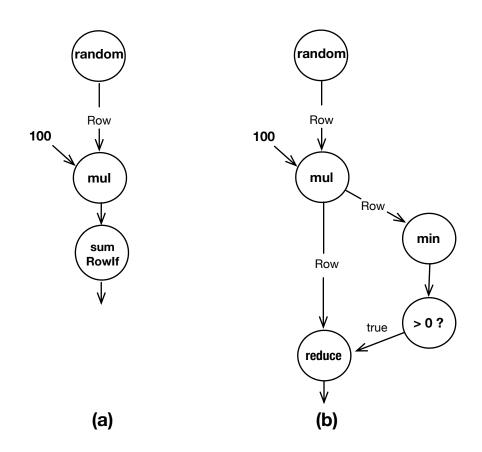

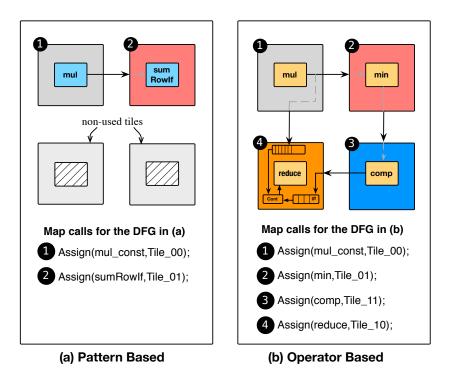

| 3.8 | All variant patterns must be pre-synthesized. Modfied source from OptiML[58] | 36 |

| 3.9 | Composing conditional operations problem. Modfied source from OptiML[58]     | 36 |

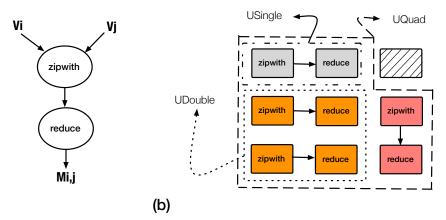

| 4.1 | DSL parallel programming patterns.                                           | 38 |

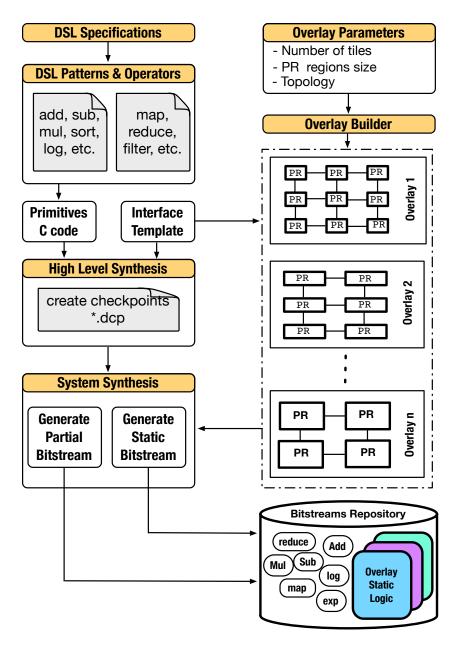

| 4.2 | Hardware design flow for the overlay static logic and partial bitstreams     | 39 |

| 4.3 | Patterns/Operators HLS template.                                             | 40 |

| 4.4 | 2D URUK Overlay Structure                                                    | 41 |

| 4.5 | Three tile interconnect types.                                               | 44 |

| 4.6 | Tile Controller.                                                             | 46 |

| 4.7 | URUK instructions set and operations code                                    | 47 |

| 5.1 | URUK compilation flow.                                                       | 52 |

| 5.2 | A DSL source code                                                            | 58 |

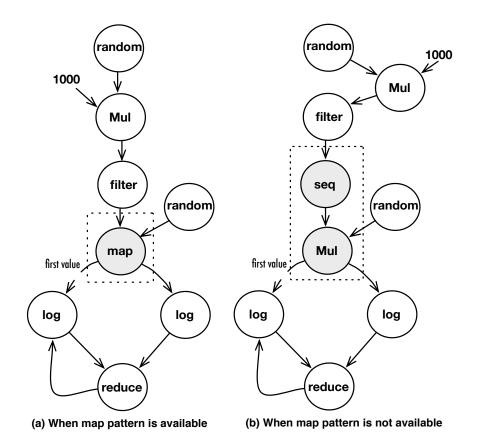

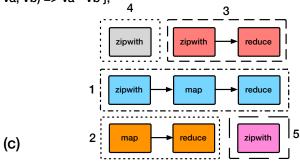

| 5.3 | Data Flow Graphs (DFGs) for the code in Figure 5.7                           | 58 |

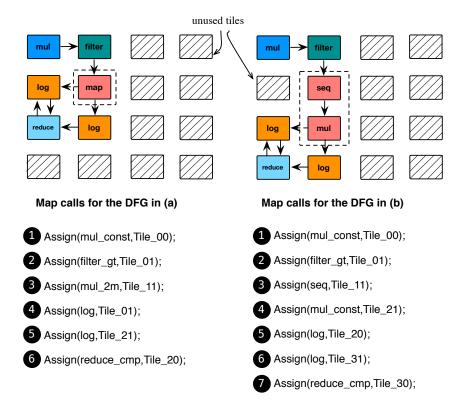

| 5.4 | Place&Route DFGs in Figure 5.8                                               | 59 |

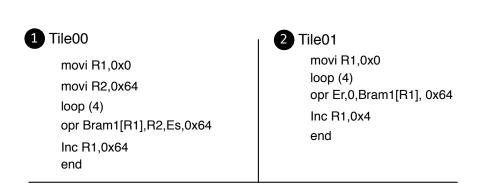

| 5.5  | Instructions and executable binaries for the two placement examples in Figure 5.9   | 59 |

|------|-------------------------------------------------------------------------------------|----|

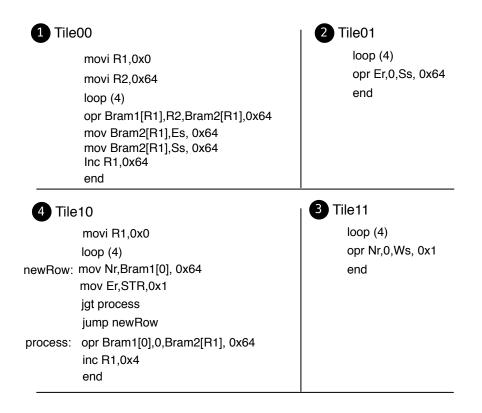

| 5.6  | Instructions and executable binaries for the two placement examples in Figure 5.9   | 60 |

| 5.7  | OptiML Example                                                                      | 61 |

| 5.8  | Data Flow Graph for the code in Figure 5.7                                          | 61 |

| 5.9  | Place&Route DFGs in Figure 5.8                                                      | 62 |

| 5.10 | Instructions and executable binaries for the pattern based placement in Figure 5.9  |    |

|      | (a)                                                                                 | 63 |

| 5.11 | Instructions and executable binaries for the operator based placement in Figure 5.9 |    |

|      | (b)                                                                                 | 64 |

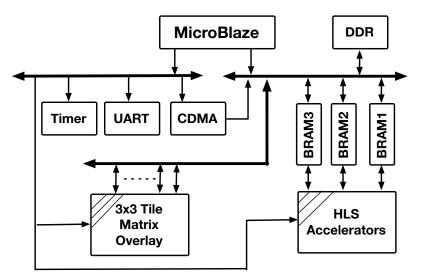

| 6.1  | Prototype System.                                                                   | 70 |

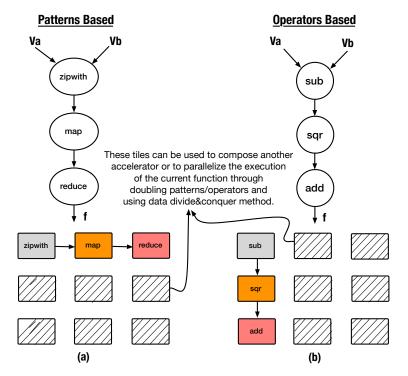

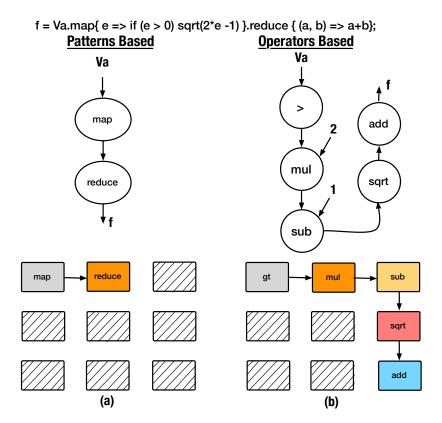

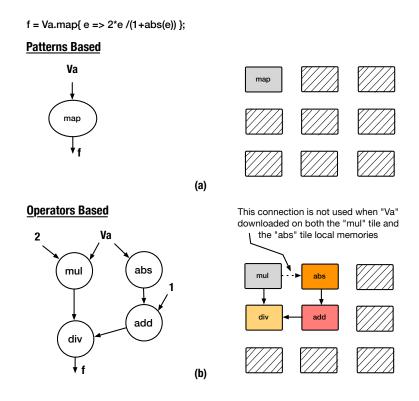

| 6.2  | The DFG of CP1 function based on pre-synthesized (a) Patterns and (b) Operators,    |    |

|      | and the placement on $3 \times 3$ overlay                                           | 72 |

| 6.3  | The DFG of CP2 function based on pre-synthesized (a) Patterns and (b) Operators,    |    |

|      | and the placement on $3 \times 3$ overlay                                           | 73 |

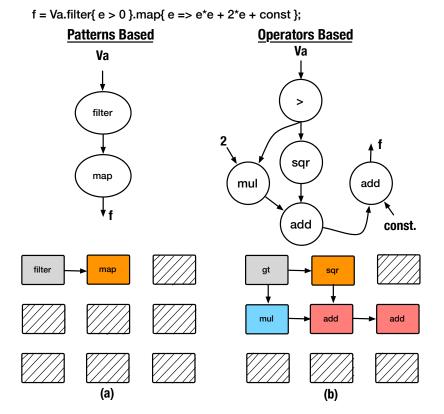

| 6.4  | The DFG of CP3 function based on pre-synthesized (a) Patterns and (b) Operators,    |    |

|      | and the placement on $3 \times 3$ overlay                                           | 74 |

| 6.5  | The DFG of CP1 function based on pre-synthesized (a) Patterns and (b) Operators,    |    |

|      | and the placement on $3 \times 3$ overlay                                           | 75 |

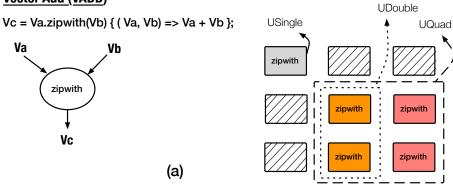

| 6.6  | Vector Addition and Matrix Multiplication DFGs, Pattern Based. Also, the three      |    |

|      | mapping methods, USingle, UDouble, and UQuad.                                       | 76 |

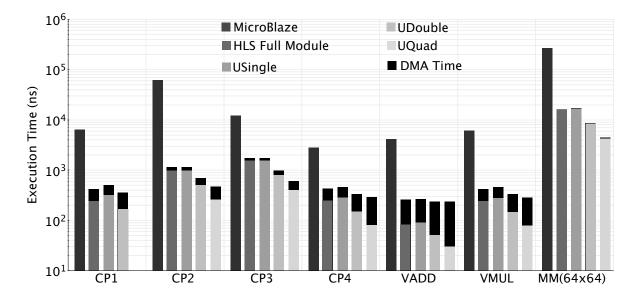

| 6.7  | The execution time of the 7 benchmark functions. Only CP1 function was not          |    |

|      | implemented in UQuad due to the limited number of tiles. The HLS accelerators       |    |

|      | were not optimized. 4K data elements(32-bit integers) are used                      | 79 |

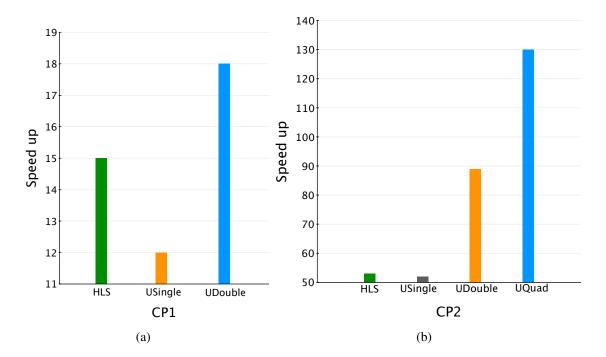

| 6.8  | The speed ups of the HLS and URUK (USingle, UDouble, and UQuad) implemen-           |    |

|      | tations over software versions of (a) CP1 and (b) CP2 functions.                    | 79 |

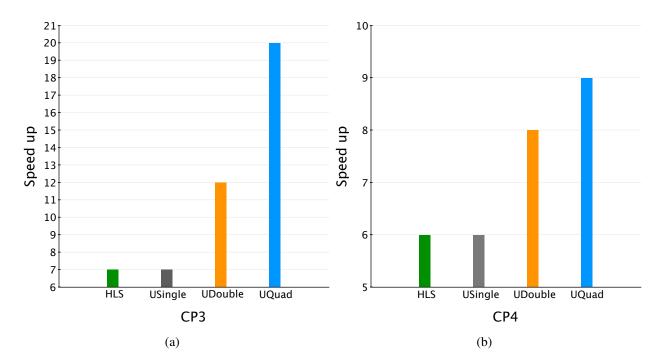

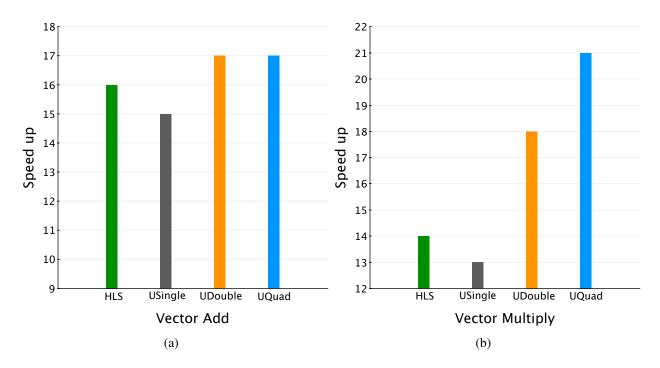

| 6.9  | The speed ups of the HLS and URUK (USingle, UDouble, and UQuad) implemen-           |    |

|      | tations over software versions of (a) CP3 and (b) CP4 functions.                    | 80 |

| 6.10 | The speed ups of the HLS and URUK (USingle, UDouble, and UQuad) implemen-          |    |

|------|------------------------------------------------------------------------------------|----|

|      | tations over software versions of (a) Vector add and (b) Vector multiply functions | 80 |

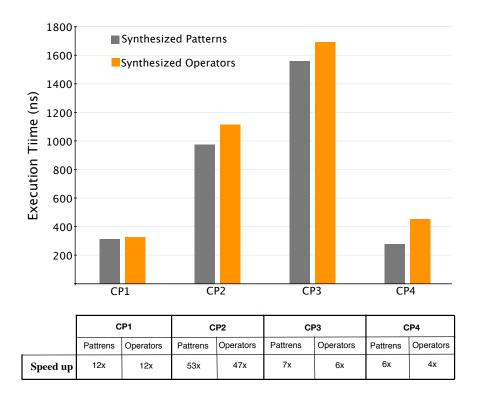

| 6.11 | Compares the execution time and speed up of UPB and UOB implementations            |    |

|      | using 4K data elements(32-bit integers)                                            | 82 |

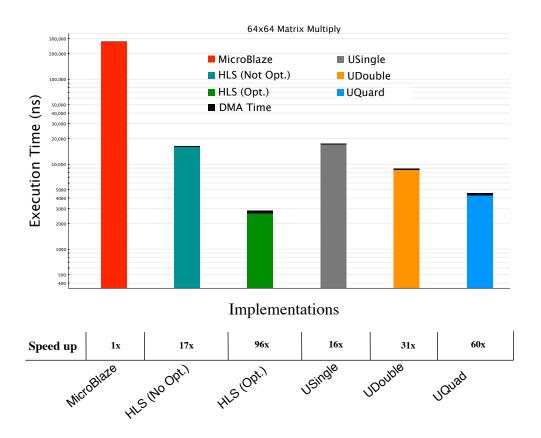

| 6.12 | The execution time of the optimized and non-optimized HLS of 64x64 matrix mul-     |    |

|      | tiply also the speed up compared to MicroBlaze and the three methods of URUK       |    |

|      | overlay implementations using 4K data elements(32-bit integers)                    | 83 |

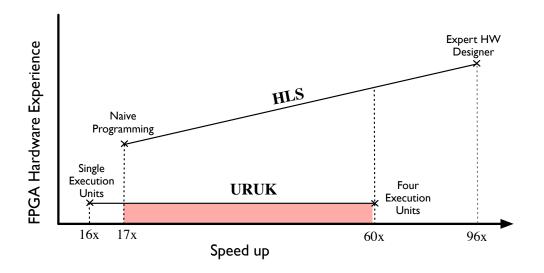

| 6.13 | The required design experience on FPGA to optimize the 64x64 matrix multiply,      |    |

|      | in Figure 6.12, on both HLS and URUK to gain speed up                              | 83 |

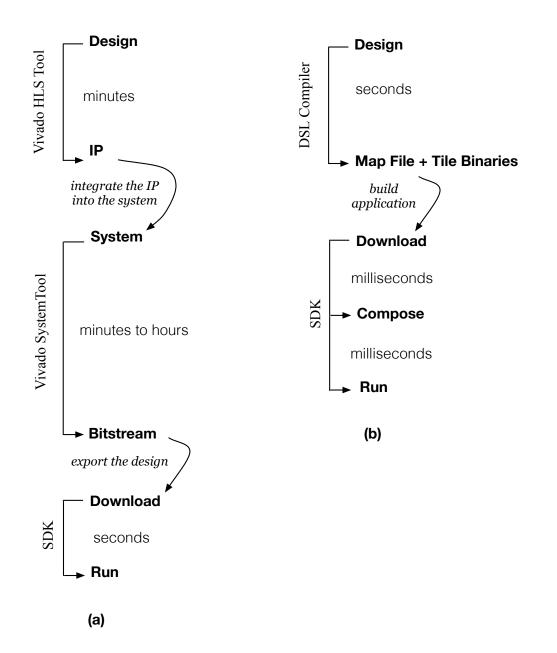

| 6.14 | (a) The HLS design steps including estimated time; (b) URUK compilation steps      |    |

|      | including estimated time                                                           | 86 |

| 6.15 | Dynamic vs. static overlays                                                        | 87 |

## List of Tables

| 2.1 | DSLs for design applications on FPGAs                       | 19 |

|-----|-------------------------------------------------------------|----|

| 3.1 | VAM Calls                                                   | 32 |

| 4.1 | Conditional branching instructions.                         | 49 |

| 6.1 | Synthetic Benchmark Functions                               | 67 |

| 6.2 | Resource Utilizations of HLS Full Accelerators on Vertix7   | 68 |

| 6.3 | Resource utilizations of Computational Operators on Virtex7 | 68 |

| 6.4 | Tile's Resource utilization on Virtex7                      | 69 |

| 6.5 | Resource utilizations of Programming Patterns on Virtex7    | 69 |

| 6.6 | Tile Utilizations of Benchmark Functions on URUK Overlay.   | 70 |

## **Terms and Definitions**

- **API** Application Programmer Interface. The defined interface of a piece of software, often times a library or operating system.

- **CP** Functions that include Compound Patterns.

- **CPU** Central Processing Unit. A programmable hardware component, often referred to as processor or core.

- **DMA** Direct Memory Access. Often referring to hardware devices that can perform memory-tomemory operations without processor assistance.

- **DFG** Data Flow Graph.

- **DSP** Digital Signal Processor. A processor specialized for signal processing, often featuring vector and multiply-accumulate operations.

- **FIFO** First-In, First-Out. A hardware component or data structure that exhibits First-In, First-Out behavior (e.g. a queue).

- **FPGA** Field Programmable Gate Array. A hardware chip whose functionality can be changed post-fabrication.

- GPU Graphics Processing Unit. A hardware component specialized for graphics processing.

- HDL Hardware Description Language (e.g. VHDL or Verilog).

- HLL High-Level Language.

- **HLS** High Level Synthesis. Synthesis the hardware design from hight level programming language. Or the abbreviation of the hight level synthesis tools named Vivado HLS.

- **HPC** High Performance Computing.

- HW Abbreviation for Hardware.

ICAP Internal Configuration Access Port

ISA Instruction Set Architecture. Also known as the instruction set of a particular processor.

JIT Just In Time. A compilation approach.

JITA Just-In-Time Assembly of hardware custom accelerators.

JVM Java Virtual Machine

LUTs Look up tables.

MM Matrix Multiply.

MPSoC Multiprocessor System-on-Chip.

NUMA Non-uniform Memory Access

**OS** Operating System.

P2P point to point

**PAR** place and routing

**PE** processing element

**PIIL** Platform Independent Interpreter Language. A language used in the run time interpreter, which is platform independent.

PRA Partial Reconfigurable Accelerator

**PR** Partial Reconfiguration

SMP Symmetric Multiprocessing

SW Abbreviation for Software.

**UDouble** mapping two copies of the DFG pattern(s) on the overlay tiles.

**UOB** URUK Operator Based.

**UPB** URUK Pattern Based.

**UQuad** mapping four copies of the DFG pattern(s) on the overlay tiles.

**URUK** An ancient city of Sumer in southern Mesopotamia, where the author of this work was born.

**USingle** mapping data flow graph's pattern(s) on the overlay tiles without doubling.

VADD Vector Addition.

VMUL Vector Multiplication.

VAM Virtual Accelerator Machine

**XDC** Xilinx Design Constraint

## **Chapter 1**

## Interoduction

Two trends are driving the pursuit of next generation computer architectures for data centers. The first trend is not new; the size, complexity, and diversity of the software applications running across distributed nodes as well as the data sets processed by these applications continues to increase. A little over a decade ago, our semiconductor industry switched our fundamental processing capabilities from scalar processors to manycores, or chips with multiple cores to meet these growing demands. Manycores can support scalable program concurrency through increasing the number of processor cores that can be fabricated within a chip.

The second trend is being driven by growing concerns over the relatively inefficient levels of energy efficiency achieved by todays computer systems. The CRA working group report entitled "Revitalizing Computer Architecture Research for Next Generation Systems" called this out as a grand challenge problem for their "System 2020 Vision". They put forth the challenge of creating a new featherweight supercomputer architecture that can achieve 0.001 nJ/op [22]. This is four orders of magnitude improvement over today's systems.

While the switch from scalar processors to manycores promised a more scalable solution for next generation data centers, it turned out to be no panacea when viewed through the lens of energy efficiency. Simply stated, Dennard scaling ended. Informally Dennard scaling states that as feature sizes of transistors are shrunk, the associated voltage and current scale down proportionally. Effectively under Dennard scaling the power would remain constant for a constant area of silicon. The ending of Dennard scaling posed immediate problems for the success of the newly evolving manycore era. The end of Dennard scaling resulted in a phenomena that became known as Dark Silicon [26], or the inability to turn on available cores due to energy limitations as well as lack of available concurrency within the program. To date, there has been no definitive answer on how to eliminate Dark Silicon, or field an architecture that can reach an energy efficiency of 0.001 nJ/op. What has occurred has been a fairly rapid evolutionary change to mixes and types of traditional processors that are built into the manycore chips. Providing systems with mixed types of processors can increase energy efficiency by increasing the use of the transistors that we can turn on. Manycores with mixes of processor types are referred to as heterogeneous manycores. By including heterogeneous components the data center can exploit a broader range of parallelism and at multiple levels of granularity. Modern heterogeneous systems include general purpose processors to exploit to support multithreading, as well as Graphics Processor Units (GPUs) to exploit data parallelism. This richer set of resources is an improvement compared to the initial manycore chips, which simply replicated a standard, or homogenous, general purpose processor.

However heterogeneous systems are limited in their ability to exploit all available types of parallelism and achieve new levels of energy efficiency. The problem is that modern workloads contain what can be referred to irregular types of parallelism that cannot be efficiently computed by fixed general purpose and data parallel types of processors. Custom hardware accelerators in the form of Application Specific Integrated Circuits (ASIC's) can be created to tailor transistors and wires to better match the data and control flow patterns of the irregular parallelism. This can result in better energy efficiency per a given set of transistor and wire resources. However, these circuits require long system development cycles and exhaustive pre and post silicon verification procedures. Moreover, the very fact that ASICs are tailored for specific applications limit their flexibility and reusability compared to more general-purpose processors. ASICs can cost upwards of \$ 50 M to design, and the development and test times are too long to attempt redesigns at anything close to the rate that the algorithms and application programs are modified.

The concept of custom accelerators is still being pursued by our semiconductor industry, but using Field Programmable Gate Arrays (FPGAs) in place of ASICs. FPGAs are not as dense or fast as an ASIC but they do provide acceptable levels of performance increases through customization,

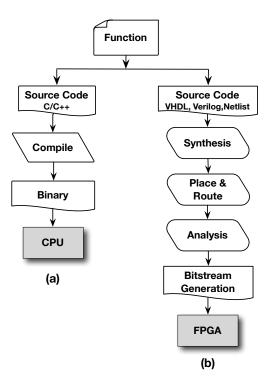

Figure 1.1: General Processors vs. FPGAs Compilation Flows.

while still providing higher flexibility and much shorter design times compared to ASICs. Our semiconductor industry is willing to trade some peak performance for design flexibility and increased developer productivity. This tradeoff was highlighted when Microsoft revealed Catapult, a prototype server with FPGAs to accelerate their Bing search engine [53]. Following the disclosure of Catapult, Intel announced acquisition of Altera, one of two major FPGA vendors, and created HARP, a new compute node that will integrate an FPGA. This trend is continuing. Recently, Amazon announced the EC2 F1 which is a compute instance with FPGAs that allow programmers to create custom hardware accelerators for their applications.

Unfortunately the state of the art in design and development tools for FPGAs are not sufficiently mature to allow application programmers that comprise the workforce in the data center to easily write, compile and run code on the FPGAs. Enabling FPGAs to be part of the solution for building energy efficient next generation systems will require successfully resolving two long standing research challenges that have so far prevented reconfigurable computing from becoming mainstream.

## **1.0.1** Compilation Challenges

The compilation flow for FPGAs is different from the traditional compilation for general processors as shown in the Figure 1.1. The design flow for FPGAs still require bit level manipulation during design time using synthesis, place and route which are time consuming processes. These processes need to be repeated again and again with every changes in the source code or design constraints. It may take from several minutes to several hours depends on the design size. This produces a large compilation gab between FPGAs and general processors. Despite the great enhancement in the CAD tools by using High Level Synthesis (HLS), the design has to go through the traditional FPGAs compilation phases, which are synthesis, place and route.

Thus a large productivity gap exists between programming gates within FPGAs and generating executables for general processors. This is true despite the great advancement provided by High Level Synthesis (HLS), tools. These tools allow functionality to be expressed in C like programming languages instead of traditional Hardware Description Languages (HDLs) such as Verilog or VHDL. While this allows programmers to express applications in a form closer in look and feel to the languages used to program processors, the designs still must still be created in hardware centric CAD tools, still require knowledge of digital design, and ultimately pass through the inefficient and time consuming steps of synthesis, place and route.

To bridge the compilation gab, other options has been suggested such as constructing an intermediate fabric (Overlay) on top of the FPGA resources to raise the level of abstractions and route in word level rather than in bit level. Theoretically, this is one of the viable solutions to redeem the gab and reduce the compilation time for FPGAs. However, overlays can be designed in many different ways to virtualize the original FPGAs resources. The costs and benefits can vary for each way. In this work, we are exploring the advantages and disadvantages of each way of design that is included in this study. Also, this study shows the tradeoffs among performance, resource utilization, and compilation complexity.

## **1.0.2** Technical Challenges

The current state-of-the-art programming languages, design abstractions and design flows used for programming FPGAs evolved from VLSI chip design and require hardware development skills. FPGA designers must still learn hardware programming models and digital design. This is a concern as the United States Bureau of Labor Statistics reported in 2015 that the United States employed approximately 85,000 hardware engineers compared to 1.3M software programmers [31]. The reconfigurable computing community put great effort to increase productivity and bring software developers to program FPGAs using High Level Synthesis(HLS). High Level Synthesis has been considered as a robust compilation technology to increase productivity. The HLS provides more familiar syntax to software programmers by using Clike languages such as SystemC, HandleC, CC++,... etc. However, it failed at getting programmers to use FPGAs because it, also, requires hardware background knowledge such as the type of interface between hardware components, timing analysis, physical constraints, resource utilization,... etc. Moreover, the design still has to go through synthesis and place and route.

If FPGAs are to become part of the infrastructure for data center and warehouse scale computers, the large cadre software programmers must be given access to these devices through their accepted practices and tools. This requires giving them a path to programming FPGAs that bypasses CAD tools, the need to understand hardware programming models, and synthesizing, placing and routing each new design. The next section briefly describes a recent proposed idea to move the synthesis process out of the way of programmers.

## 1.1 Just-In-Time Assembly

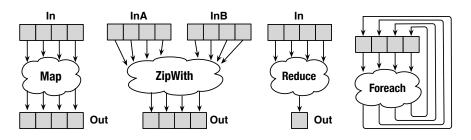

Recently Just-in-Time (JIT) techniques have been proposed for assembling pre-built circuits at runtime within FPGAs [43], [45], and [44]. The idea is that pre-synthesized parallel patterns such as map, reduce, foreach, filter..etc can be made available within libraries and then placed

into the FPGA by a runtime interpreter. JIT holds promise for effectively moving the synthesis process out of a programmers path and allowing hardware circuits to be compiled and interpreted. JIT techniques have been applied to programming predefined overlay components such as ALUs as well as moving bitstreams into and out of partial reconfiguration regions. While this approach allows programmers to compile accelerators it suffers from the following drawbacks:

- All Variants of Programming Patterns Must be Synthesized.

- Cannot Compose Simple Conditionals with Pre-synthesized Programming Patterns.

## **1.2** Thesis Statement

Enabling software developers to apply their skills over FPGAs continues to be an unreached research objective in the reconfigurable computing community. JIT Assembly holds promise for effectively moving the synthesis process out of a programmers path and allowing hardware circuits to be compiled and interpreted. To extend the JIT Assembly approach and support moving the synthesis process out of the way of programmers, I am proposing Reconfigurable Overlay,URUK, which composes fundamental computational operators instead of full patterns . This thesis evaluates the new JIT Assembly by considering the following questions:

- Can URUK eliminate the challenges that result from composing pre-synthesized parallel patterns while still preserving all the productivity benefits of the original JIT approach?

- Can URUK allow conditionals to be composed with the synthesized programming patterns without generating multiple bitstreams for each case?

- How much time does it take to construct an accelerator using the new compilation flow targeting URUK compared to Vivado HLS?

- How will performance and resource utilization be affected compared to full custom designed modules using Vivado HLS as well as the original JIT approach?

• What are the costs and benefits of considering Partial Reconfiguration techniques as part of the overlay dynamic system?

## **1.2.1** Thesis Contributions and Organization

Throughout the exploration of this work, I have made the following set of contributions and published them in top-tier conferences.

- A Dynamic Overlay to Support Just-In-Time Assembly: In this work, a dynamic overlay is designed to support Just-In-Time assembly by composing hardware operators to construct full accelerators. The hardware operators are pre-synthesized bitstreams and can be downloaded to Partially Reconfigurable(PR) regions at runtime [3].

- A Run-time Interpretation Approach For Creating Custom Accelerators: We provided a new approach in which hardware accelerators can be built and run using compilation and run time interpretation. Also, we demonstrated that our approach can enable software programmers without any hardware skills to create hardware accelerators at productivity levels consistent with software development and compilation [43].

- *Composing Pre-Synthesized Building Blocks at Run-Time:* We demonstrated a technique to move synthesis out of the programmers path by composing pre-synthesized building blocks using a domain-specific language that supports programming patterns tailored to FPGA accelerators. Our results show that the achieved performance of run time assembling accelerators is equivalent to synthesizing a custom block of hardware using automated HLS tools [44].

- *Just-In-Time Assembly of Custom Accelerators:* We demonstrated that Synthesis can be eliminated from the application programmers path by becoming part of the initial coding process when creating the programming patterns that define a Domain Specific Language. Programmers see no difference between creating software or hardware functionality when

using the DSL. A run time interpreter is introduced that assembles hardware accelerators within a configurable tile array of partially reconfigurable slots at run time [45].

• A Flexible Multilayer Perceptron Co-processor for FPGAs: We designed a Multilayer Perceptron Co-processor (MLPCP) targeting FPGAs that is configurable during design time and programmable during runtime. The MLPCP can be reprogrammed at run time to rapidly change network topologies and use different activation functions. It promotes design reusability and allows application developers to change parameters of a given network without the need to resynthesize [2].

The rest of this thesis is organized as follows. Chapter 2 gives background on fine-grind reconfigurable architectures, and Course-Grind Reconfigurable Accelerators as well as providing a survey on the start-of-the-art approaches on constructing intermediate fabrics, overlays, FPGA virtualizations and programming modules. Chapter 3 provides background on the original Just-In-Time Assembly (JITA) of custom accelerators. Next, Chapter 4 presents the proposed solution as well as the new overlay architecture including the overlay instruction sets. Chapter 5 provides a guideline for the compilation process when targeting URUK overlay. Chapter 6 describes the evaluation methods and dissusses the results. Finally, Chapter 7 gives answers to the thesis questions and potential future work.

## **Chapter 2**

#### Background

This chapter provides an overview of reconfigurable hardware architectures including Field Programmable Gate Arrays (FPGAs) and Coarse-Grained Reconfigurable Architectures(CGRAs). Additionally, the compilation flow and the productivity challenges of FPGAs are discussed. Then, it presents the effort of the reconfigurable computing community on raising the design abstraction level and increasing productivity. Moreover, the start-of-the-art approaches on constructing intermediate fabrics, overlays, and programming modules are presented.

#### 2.1 FPGAs Overview

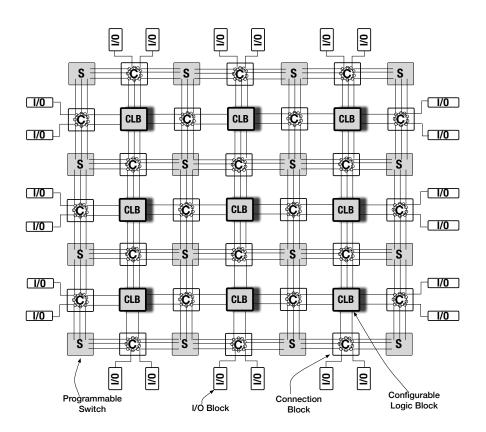

Field-Programmable Gate Arrays (FPGAs) are electrically programmable silicon devices that can be configured to implement almost any complex digital circuits or systems. An FPGA is a twodimensional array of logic units and electrically programmable routing interconnects [34]. Logic units comprise Configurable Logic Blocks(CLBs), Digital Signal Processors (DSPs), Block RAMs (BRAMs), Input-Output Buffers (IOBs), and Digital Clock Managers (DCMs). These logic units can be configured and connected to implement different combinations of sequential and combinational circuits to provide different functionalities ranging from one simple gate to a sophisticated microprocessor. CLBs include a number of Lookup Tables (LUTs) that can be programmed to implement any boolean expression. The routing interconnects consist of variant length wire segments and electrically programmable switches, which can switch on and off the connection between logic units in bit level. Figure 2.1 shows a general example of FPGAs which includes a two-dimensional grid of CLBs surrounded by I/O blocks. The grid is wired and connected by programmable switches. The "programmable/reconfigurable" term in FPGAs refers to the capability of forming a new digital circuit on a chip after fabrication by programming the interconnect switches and changing the behavior of the logic units [34].

Routing interconnect makes up 90 percent of the total area of FPGAs[60]. In consideration of that FPGAs architecture meant to be general and capable of implementing any digital circuit, the routing interconnect must be very flexible to adapt to a large variety of circuits. During the design phase, Computer Aided Design (CAD) tools search for an optimal solution to place specific logic into specific configurable units and wire them at bit level. With every possible place and route solution, the CAD tools evaluate design constraints to meet the specifications. For instance, the tools perform timing analysis for every place and route to meet the timing constraints, and if the design violates timing, the tools will seek for another possible solution for place and route. These processes consume a large amount of time, which ranges from several minutes to days depending on the design size.

Typically, FPGAs are programmed with Hardware Description Languages (HDLs) such as VHDL and Verilog. The traditional FPGAs' design flow includes four stages as follows. First, designers write their code in VHDL or Verilog and set timing and I/O constraints of the design. Second, CAD tools apply logic synthesis, which translates a source description code written in an HDL into a set of Boolean gates and Flip-Flops. Then, synthesized design is passed to the implementation stage which includes place and route processes. The place and route are the heaviest tasks in the whole design flow because tools are looking for the best solution in a large search space. After the implementation, bitstreams can be generated which will be downloaded to the target FPGA.

To enable programmers to access FPGAs and increase their productivity, we need to eliminate two major challenges: First, we need to allow programmers to write their applications in high level languages. Second, we should move the synthesis, place and route out of the programmers' way. The next sections present the effort of the reconfigurable computing community to phase out these challenges.

10

Figure 2.1: General FPGA Architecture.

## 2.2 CGRAs Overview

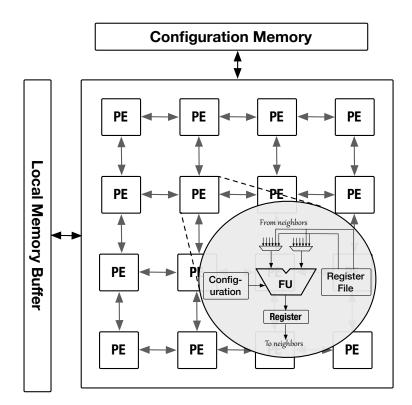

Coarse-Grained Reconfigurable Architectures(CGRAs) have been proposed as an alternative to the fine-grain architectures (FPGAs) to support faster compilation through raising the level of reconfigurability from bit-width to word-width granularity, which enables on-the-fly customization and reduces configuration overload. Particularly, CGRAs are designed to be customized on ASIC for specific applications that have inherent data-parallelism. CGRAs are mainly composed of Process-ing Elements(PEs), that include ALUs, multipliers, and shift registers connected by word width mesh-like interconnects and are controlled by resources managers and synchronization modules. Figure 2.2 shows a sample of a CGRA architecture. CGRAs can be either tightly coupled(e.g, Matrix[52], Chess[46], and DySER[30]), or loosely coupled (e.g. MorphoSys[56], CHARM[19], and PipeRench[29]). Loosely coupled CGRAs are more independent from the host CPU, and they have their own control flow.

Figure 2.2: General CGRA Architecture.

CGRAs can be connected in a linear array (1D)based architecture such as RaPid[25] and PipeRench[29] or in 2D mesh interconnect such as Matrix[52] and MorphoSys[56]; The 1D architecture is suitable for computations that can be linearly pipelined. In contrast, it is not efficient to support block-based applications [62]. On the other hand, the 2D mesh architectures have a better support to block-based processing such as in multimedia applications.

CGRAs are typically configured using opcodes instead of Hardware Description Languages (HDLs), which leads to reducing compilation time through eliminating the extensive place and route processes. CGRAs instructions can be stored in a centralized or distributed instructions memory(s) [39]. Each computation unit interprets the assigned instructions and selects the right hardware operator for the specified operation. ALUs within CGRAs should have the hardware components for all supported operators on fabrics. Only selected components will be used while others occupy area while staying idle. CGRAs, in general, are limited to simple operations such as add, sub, mul, and logical operations. In order to support more computational operations, PEs will

become larger and may reach to the complexity of a processor.

Furthermore, CGRAs are limited to accelerating simple operations in nested loops. Most CGRAs do not support conditional operations and branching. Additionally, they lack the flexibility that FPGAs provide regarding user control over low-resource definition and allocation.

## 2.3 High Level Synthesis

The increase in silicon capacity and System-On-Chip (SOC) complexity has shifted interest toward a higher level of abstraction which is considered on of the powerful ways of regulating complexity and enhancing design productivity [18]. The reconfigurable computing community has addressed the productivity challenges within FPGAs design flow and tried to raise the abstraction level beyond Register Transaction Level (RTL) by using High Level Synthesis (HLS). The HLS tools translate untimed or partially timed functional specifications written in one of the high level languages such as C, C++, SystemC, Haskell, ..etc into low level fully timed RTL specifications. That leads to not only providing more familiar syntax to software programmers but also reducing the code density. For example, the conducted study from NEC[68] shows that large designs within around 300k lines of RTL code can be reduced by 7X-10X when using high abstractions. Further, the HLS flow reduces the required time for creating hardware as well as reducing verification time and facilitates resource utilizations and power analysis. Currently, several commercial HLS tools are available such as Vivado HLS, LegUp[14], and ROCCC[61].

In general, HLS has faced many challenges in translating source codes written in sequential languages into hardware description specifications. For instance, bit accuracy, timing, concurrency, and synchronization are not supported explicitly in Standard C/C++; while they are essential in hardware design [18]. On the other hand, pointers, recursion, polymorphism, and memory management are complex C/C++ constructs, which cannot be transformed easily into hardware. To overcome these challenges, several solutions have been applied, such as disallowing the use of dynamic constructs, using compiler directives and pragmas to explicitly specify concurrency, and

introducing hardware-oriented language extensions and libraries. HardwareC[33], SpecC[27], and HandelC are examples for hardware language extensions, and SystemC is an instance for hardware libraries.

Despite the great accomplishments in High Level Synthesis, software programmers still obligated to gain knowledge in hardware low level details to create efficient designs. In order to create an optimized design, programmers/designers should explicitly specify pragmas and directives (Vivado HLS), clock boundaries(Handel-C), and clock edges/events (SpecC, SystemC) in their source code. For example, in Vivado HLS, the user is required to understand which loop to unroll, when to pipeline operations, what suitable interfaces for the inputs and the outputs, and the tradeoffs among power, performance, and resources utilization. Furthermore, even through the HLS has reduced the hardware design time, the compilation time is still significant. In fact, the design still has to go through the extensive processes, which are synthesis, place and route.

The FPGAs research community has taken another path to reduce compilation time and increase productivity by using overlays, which are discussed in the next section.

#### 2.4 Overlays

Intermediate Fabrics, or overlays, have been proposed to allow higher level computational components such as soft processors, and vector processors [67, 66], as well as Course Grained Reconfigurable Arrays(CGRAs) type structures [20, 21, 16], to be embedded within FPGAs. The potential advantage of such overlays is that circuits and hardware acceleration can be achieved through compilation instead of synthesis on existing FPGAs. Conventional approaches for enabling CGRAs on an FPGA are to replace LUTs and Flip Flops with small programmable computational units like ALUs as the compilation target. The ALUs are embedded within a network of switch boxes and channels. The computational units can be populated with programmable functions at a rough equivalence in circuit density to Medium Scale Integrated (MSI) components. Arithmetic and logical operations, as well as shift registers, and multipliers have been proposed. These units then serve as the target for compilers to exploit loop level parallelism. The interconnect structures are defined to support wider word widths instead of bit level interconnections. Typically, overlays introduces some overhead inefficiencies due to the additional resources, routing delays between computational units, and limitations on the granularity of parallelism. Over the past years, several approaches for virtualizing FPGA resources and building overlays have been published. The next sections present some overlay projects proposed by the reconfigurable computing community.

## 2.4.1 JIT FPGA

The JIT FPGA approach presents a virtual FPGA, a synthesizable firm-core described in structural VHDL. It enables the development of standard hardware binaries, which provide portability among different FPGAs. The virtual FPGA is a fine-grained fabric with virtualized LUTs. The structure of one virtual LUT requires 100 physical FPGA LUTs. The JIT compiler for FPGAs begins with the standard hardware binary and performs mapping to place the hardware logic onto the virtual LUTs, then implements place and route. The virtual FPGA can achieve portability and programmability at the cost of area and performance, around 100x area overhead and 6x slow down in speed respectively [9, 40, 41, 42].

## 2.4.2 Virtual FPGAs

FPGAs' virtualization can be accomplished by constructing a coarse-grained architecture, which utilizes the low level hardware of FPGAs and provides high level of programmability. Metzner [51] presented a coarse-grained architecture that enables run-time dynamic hardware multithreading. The architecture includes computational elements connected in a 2D mesh network, which can route data among them. Virtualization also can be achieved through partial reconfiguration techniques as in OpenStack [13], which allows users to "boot" pre-designed custom hardware accelerators in a similar way of Virtual Machines.

## 2.4.3 ZUMA:

An open source embedded FPGA architecture constructs an overlay on top of existing FPGA resources and intends to achieve portability of designs and bitstreams among different vendors (Xilinx, Altera) and parts. It follows the philosophy of virtual machines in computing environments. The ZUMA architecture attains virtualization by taking advantage of reprogrammability of LUTRAMs provided in modern Xilinx and Altera FPGAs also forming a new programmable LUTs and routing MUXs. It requires a bout 40 physical FPGA LUTs to create one virtual ZUMA LUT. That puts around 40x area overhead and consumes more resources which basically increases power consumption [10, 63].

## 2.4.4 Intermediate Fabrics

Intermediate Fabrics(IF) provides a virtual intermediate layer between the underlying physical FPGA resources and user designs. The IF structure is nearly identical to conventional FPGAs structures; this is represented by distributed computational unites in a grid across the fabric, with switch boxes, connection boxes, and tracks. Similarly to FPGAs, IF is programmed using a configurable bitstream. On the contrary, the IF resources are not as general as the FPGA resources. In fact, computational unites and routing resources are specialized for a particular domains or applications. The specialization of the IF approach makes it effective when the application is matching an already pre-built fabric. A new fabric should be implemented if there is no match between the application and the current available fabrics. Additionally, the area overhead incurred by virtual fabrics is significant [20, 21].

## 2.4.5 Synthesis-Free JIT Compilation:

Synthesis-Free JIT Compilation [15] is another project that explored the feasibility of translating hot straight lines of code into Virtual Dynamically Reconfigurable(VDR) overlay, which consists

of an array of functional units that are interconnected by a set of programmable switches. The approach uses traces to capture the line of codes that are going to be executed frequently, and transforms them into Data Flow Graphs(DFG), which are then mapped to the VDR overlay. Functional units in the VDR are also limited to basic operations (e.g. addition, subtraction, and multiplication).

## 2.4.6 SCGRA

An FPGA based CGRA called Soft Coarse-Grained Reconfigurable Array(SCGRA) [38] is an intermediate compilation step that replaces compiling high-level applications directly to circuits into scheduling operational tasks targeting SCGRA overlay. The approach aims to promote design productivity. SCGRA focused on the hardware resource constrains, IO bandwidth constrains and the loop parallelism partition, whereas processing architectural design supports only simple logical and arithmetic operations, which limits the capability of processing complicated functions. Additionally, it does not support conditional branchings within loops.

## 2.4.7 QuickDough

Presents a design framework for constructing loop accelerators targeting an FPGA-based Soft Coarse-Grain Reconfigurable Array (SCGRA) overlay. During compilation, QuickDough framework transforms a high level loop into a Data Flow Graph(DFG), schedules the DFG nodes to the SCGRA and estimates the communication cost, and then selects an accelerator from a pre-built bitstream library. By taking the advantage of pre-built bitstreams, the framework aims to translate C-nested loops into hardware circuits supporting quick compilation for a hybrid CPU-FPGA system. In the same way, the work focuses on the automatic customization of the overlay hardware parameters, loop unrollment factors, and buffer sizing as well as hardware-software communication. Their results show that with the cost of 10 to 20 minutes in compilation overhead spent in customization, the performance was improved by 5x [37].

## 2.4.8 QUKU:

QUKU is a coarse-grained reconfigurable PE array (CGRA) overlaid on an FPGA. The main goal of this overlay is to reduce the reconfiguration time and increase the accessibility of FPGAs. By applying the model at an architectural level in QUKU, better hardware efficiency can be achieved for a wide domain of applications. A few widely used DSP algorithms have been presented to demonstrate the application of process network models to architectural template generation in QUKU [54, 55].

## 2.4.9 Soft Processors

Soft processors are considered one of the overlay forms that support fast application compilation. In addition to the commercial cores such as MicroBlaze form Xilinx [65] and Nios II from Altera [4], some other soft processors are provided by different research groups. For instance, an open source soft processor [32] is provided with RISC-V instruction set. It is a 4-stage pipeline, tightly-coupled architecture with FPGA accelerators. The processor is portable between FPGA platforms and can be synthesized to run at maximum frequency, 268.67 MHz.

Another tightly-coupled VLIW processor with a course-grind reconfigurable matrix called Architecture for Dynamically Reconfigurable Embedded Systems (ADERS) [49] was designed to simplify hardware-software programming models, scale down communication overhead, and essentially gain sharing resources. The same research group developed a framework [48], to compile C-source code, targeting the architecture along with a scheduling algorithm to exploit loop level parallelism [47]. The integration between the processor and the reconfigurable array as well as the overall system performance was the main concern in the ADERS project.

Several other soft processors published in the academia briefed as follows: DSP Extension Architecture (iDEA), a lightweight soft processor which takes advantage of DSP48E1 primitive in Xilinx FPGAs [17]; Octavo, a highly parametrized multi-threaded processor with ten pipeline

| DSL     | Language Syntax | Output                     | Reference |

|---------|-----------------|----------------------------|-----------|

| FSMLang | C-style         | VHDL, Verilog, C (drivers) | [1]       |

| Chisel  | Scala           | Verilog, C++ (simulation)  | [7]       |

| Kiwi    | C# .Net         | RTL netlist                | [64]      |

| Lime    | Jave            | VHDL, Verilog              | [6]       |

| Delite  | Scala           | C, C++, Scala, OpenCL      | [12]      |

Table 2.1: DSLs for design applications on FPGAs.

stages implemented on Stratix IV FPGA [35]; CUSTARD, a customizable multi-threaded soft processor supporting hardware threads to be implemented in dedicated hardware [23]; Anjam and others [5] also presented a VLIW soft processor with dynamically adjustable issue width and cores through utilizing the partial reconfiguration feature in Xilinx FPGAs. In general, soft processors allow software developers to directly compile their source code into FPGAs and provide reusable overlay. However, soft processors are considered mostly suitable for embedded systems due to their low frequency and sequential execution.

## 2.5 Domain Specific Languages

Domain Specific Languages(DSLs) (e.g. Python, Snort, HTML) are common within software development. DSLs promote the use of languages tuned for the needs of specific application domains. Once created and tuned, the language promotes increased programmer productivity through appropriate abstractions and heavy reuse. DSLs are also being considered to generate accelerators within FPGAs. Table 2.1 summarizes the currently used DSLs for building accelerators on FPGAs.

#### 2.5.1 FSMLang:

FSMLanguage is a domain-specific language (DSL) for describing finite-state machines. The language was developed in order to create a way for programmers to develop reusable representations of FSMs. The FSMLanguage compiler is capable of producing both software and hardware implementations of FSMLanguage programs. Both implementation types remain compatible with one another as the communication abstractions that are built in to FSMLanguage are able to cross the hardware/software boundary [1]. The language structure allows one to easily describe FSMs in a way that eliminates many of the common errors that occur when describing FSMs in typical HDLs. The FSMLanugage compiler automatically generates correct code for FSM reset, sensitivity lists, memory access schemes, FSM flip-flops, and state transitions. The abstractions for memories and channels allow programmers to use familiar, software-like constructs for describing timing and synchronization sensitive operations. Additionally, these abstractions are reusable and can be used in both software or hardware implementations of FSMLanguage programs.

## 2.5.2 Chisel:

To design more flexible hardware units, Chisel, a new hardware construction language that supports advanced hardware design, has been created. The goal of Chisel is to allow a designer to provide a procedural description of how the hardware should be instantiated, given a set of parameters that are fixed at the prototyping phase of the design. By embedding with the Scala programming language, Chisel can raise the level of hardware design abstraction by providing concepts including object orientation, function programming, parameterized types, and type inference[7]. Chisel can reduce the programming challenges through a high-speed C++ based cycle-accurate software simulator as well as low-level Verilog, which is designed to be mapped either to FPGAs or to standard ASIC flow for synthesis.

#### 2.5.3 Aspen:

Abstract Scalable Performance Engineering Notation (Aspen) fills a gap between existing performance modeling techniques and rapid exploration of new algorithms and architectures [57]. In particular, both formal specification of application and an abstract machine model are need to analysis the performance behavior. In Aspen language, the modularity of performance can be achieved by balancing the workload with the overall performance characteristics of main kernels [50]. However, only the control flow and data flow are expressed at a function or module level and the behavior is input-dependent and implementation-specific. Thus, Aspen is not able to analyze auto-tuning and projecting expected performance.

#### 2.5.4 Lime:

Lime, developed at IBM Research, is a Java-compatible object-oriented language which targets heterogeneous systems with general purpose processors, FPGAs, and GPUs. Java bytecode can be generated by the Lime compiler, which allows a programmer to design a suitable Java program into a pattern amenable for heterogeneous parallel devices, and the program can run on any platform that supports a Java virtual machine. The compiler can also synthesize and then generate hardware designs for FPGAs. The Lime language exposes parallelism and computation explicitly with high-level abstractions. Streaming computation as well as vector operators are virtualized using some extra abstractions. Although the paradigms provide a very high-level abstraction, optimizations are limited due to the initiative point is focus on lower-level byte-code [24].

## 2.5.5 Delite:

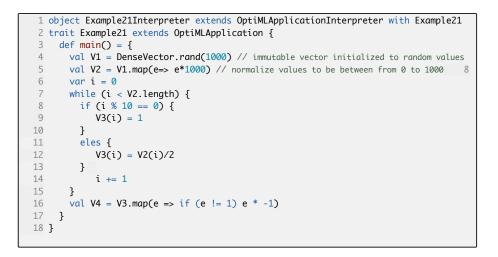

Delite was essentially created as an open source compiler framework to build substantial concurrency languages for use on heterogeneous multiprocessor systems. Delite simplifies the definition and construction of a DSL language and includes the generation of the compiler for the new language. OptiML-a DSL for machine learning applications, OptiQL –a DSL for data querying, and OptiGraph –a DSL for graphic analytics have been created using Delite and are publicly available. Delite is built in a modular fashion to allow the insertion of unique domain specific optimizations to be included into the compiler flow. All DSLs then take advantage of the built in traditional lower level instruction optimizations, such as common subexpression elimination, loop fusion, etc. Delite's modular structure allows new backends to be easily added [12]. Current backends produce Scala, C++, and CUDA. Delite can be downloaded at http://stanford-ppl.github.io/Delite/index.html.

Chapter 3

#### **Just-In-Time Assembly**

### 3.1 Introduction

The earlier work by Sen Ma, Just-In-Time Assembly (JITA) [43, 45, 44], aims to move the synthesis process out of the programmers' path, increase application developers productivity, and support design portability between different FPGA vendors and parts. JITA approach takes advantage of partial reconfiguration technology to compose custom accelerators on the fly by using pre-built bitstreams. Since this work is extending the JITA approach, this chapter is dedicated to provide background description about the JITA.

#### **3.2 JITA Approach**

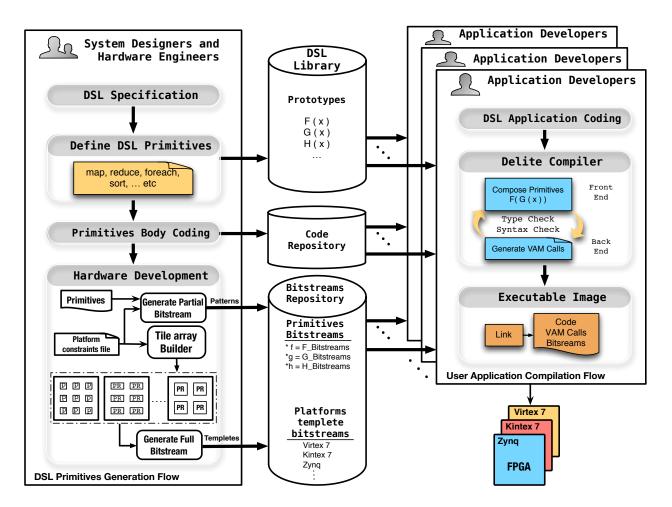

The JITA approach aims to increase the FPGAs' programmers productivity by moving the synthesis, place and route processes out of their path through composing pre-synthesized small bitstreams to form full custom accelerators. Under traditional FPGA design flows the programming patterns are combined into a single object, and then object is synthesized. Each time the functionality in the source code is changed to create a new object, it must be re-synthesized. This keeps synthesis, place and route in the development path of the programmer. The JITA approach differs in that individual programming patterns are synthesized at the same time they are coded as part of creating a Domain Specific Language (DSL). Software prototypes for each programming patterns are placed in a library and made available to the application programmers. This allows programmers to work with the software prototypes within a DSL without having to repeat synthesis.

To achieve the goal, the JITA approach provides a prototype system that includes an overlay to virtualize the FPGA resources, a new compilation flow, and a runtime interpretation.

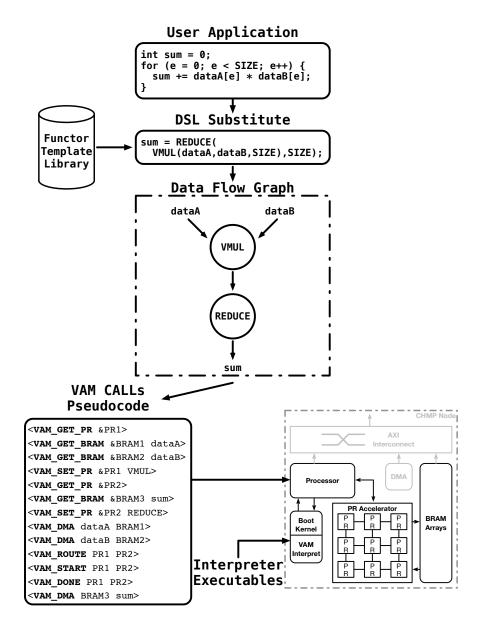

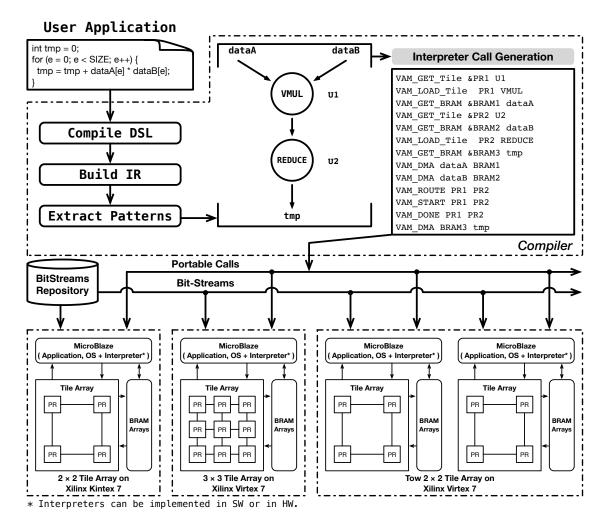

Figure 3.1: Design Approach.

# **3.3** Compilation Flow

The JITA uses the Delite Framework to create a new DSL. This is then compiled into for the overlay. Figure 3.1 shows how Delite supports two classes of users; system programmers and hardware engineers that create the DSL use the flow on the left, and application programmers use the flow on the right. Creating a standard DSL on the left involves defining and coding the programming patterns. The body of each primitive defined for the DSL is passed through an HLS generator to produce bitstreams. The modularity of the flow allows any HLS generator to be plugged in. The Vivado HLS tools were used for this step. Prototypes for the DSL primitives as well as their bitstream representations are placed in a library. Application programmers pull

prototypes from the library just as if the DSL was created for traditional software implementation.

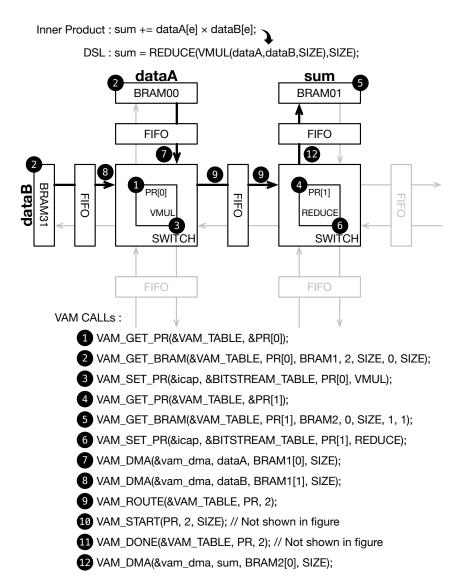

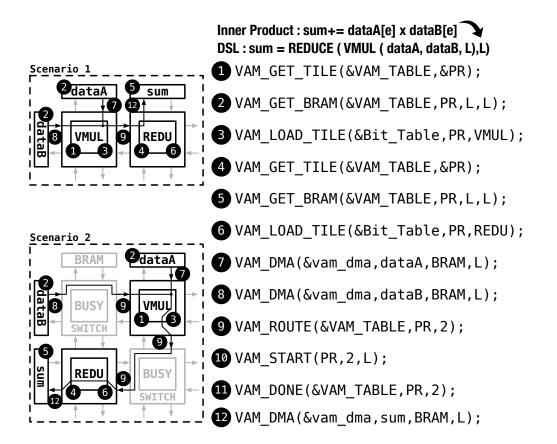

After the application programmer forms the complete accelerator functionality, they invoke the Delite compiler with the "-vam\_calls" flag set. This invokes the JITA backend generator to produce a series of interpreter instructions that represent data and control flow information that will be used by a run time interpreter to build and control the accelerator at run time. These instructions, called Virtual Accelerator Machine (VAM) language are shown in Table 3.1. Figure 3.2 shows the interpreter instructions (pseudo code) output by the compiler for creating an accelerator to compute an inner product. The inner product was created by composing the REDUCE and VMUL primitives defined within the DSL. The compiler can also be run without the "-vam\_calls" flag to generate standard software executables for running on a standard processor and during debugging.

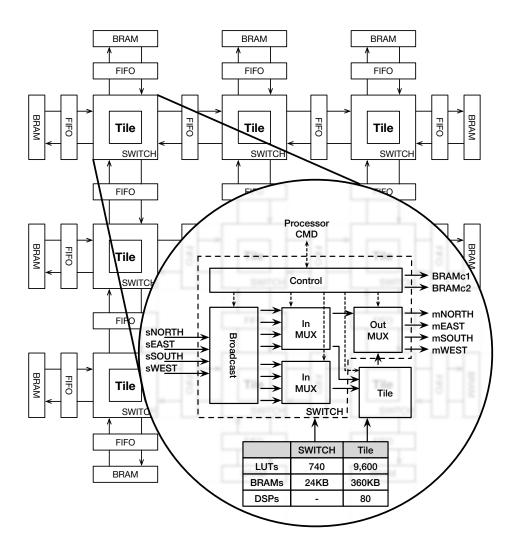

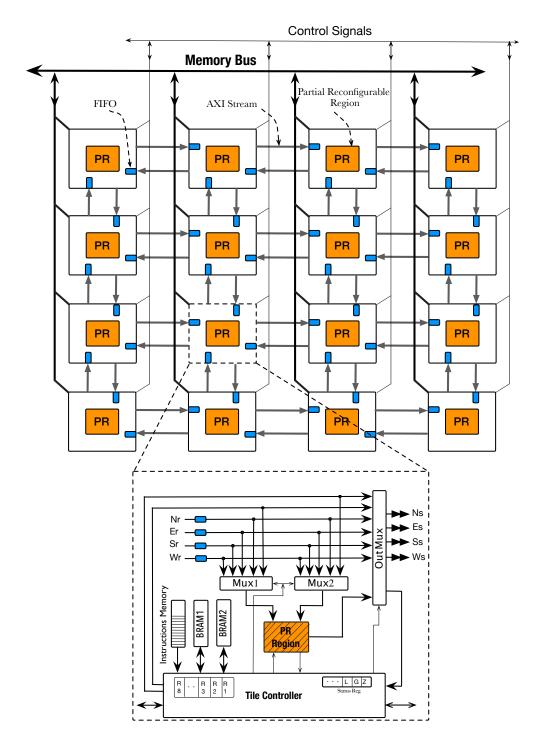

# 3.4 JITA Overlay

The JITA overlay was pre-formed programmable components built on top of an FPGAs lookup tables and flip-flops. The overlay was occupied with tile array and Black RAMs. The overlay includes a nearest neighbor programmable word width interconnect similar to traditional CGRA type overlays. Different from traditional CGRA overlays, the JITA overlay exposes the lookup tables and flip flops of the FPGA as partially reconfigurable tiles instead of abstracting them into programmable computational units. This combination of pre-formed interconnects and partial reconfiguration regions allows the bitstreams for the programming patterns to be downloaded at run time into the intermediate fabric. Figure 3.3 shows the structure of the hybrid overlay. The basic structure is a 2D array of partial reconfiguration tiles and programmable switches that are connected as a nearest neighbor interconnect network.

Figure 3.2: Compiler Flow and VAM Call Generation.

Figure 3.3:  $3 \times 3$  Tile Array and Interconnect Network.

### 3.4.1 PR Tiles

The configurable  $3 \times 3$  array, shown in Figure 3.3, was constructed of partial reconfiguration tiles sized at 9,600 LUTS, 360KB BRAM, and 80 DSPs. This PR regions was sized to hold the largest bitstream generated from the test DSL. The exact size of tiles is variable and can be set when the DSL is created. The number of the tiles is derived based on the size of the tiles and the number of resources available on a target FPGA logic family. At runtime, the PR tiles will be populated with functors' partial bitstreams which behave as computational units. By swapping different functors in the PR regions, a new accelerator will be formed. The input and output data for each PR region are controlled by tiles' programmable switches.

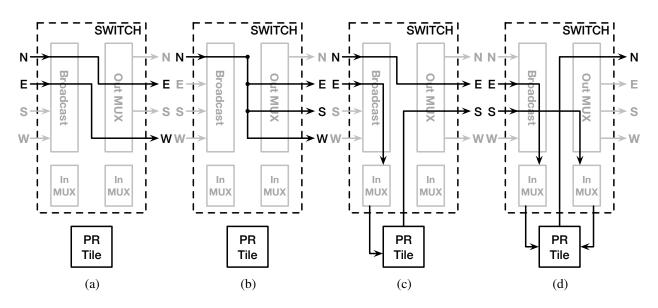

Figure 3.4: Switch Routing.

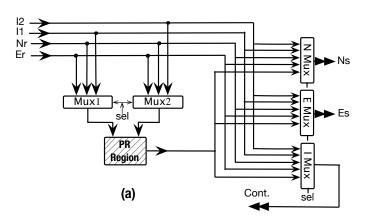

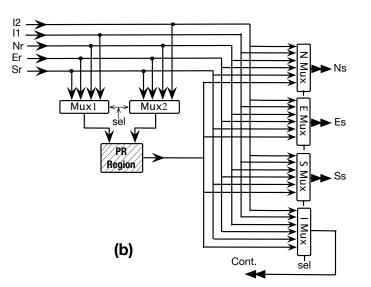

### 3.4.2 Programmable Switch

Figure 3.4 provides an exploded view of a switch. Figure 3.4 shows the types of routing patterns that can be programmed into switch. The routing patterns were defined to enable each switch to direct inputs and outputs through the tile, as well as serving as a pass through for routes between distant tiles.

Routes can be set statically or dynamically. Dynamic settings used for allowing the switch to support different time varying routing needs when multiple accelerators are resident within the overlay. Each switch serves as a pass through for one accelerator, and then source and synch data for a tile that is part of a different accelerator.

#### 3.4.3 Local Memory

The boundary cells in the overlay include connections to blocks of local memories (BRAMs). These BRAMS can be used as addressable local memories or as FIFO data buffers for streaming data. Block data transfers use DMA (not shown) between the BRAMs and Global DRAM memory. The BRAMs are placed within the global address map of the system, allowing any processor or bus master device to transfer data into and out of a local memory. The BRAMS have buffer full/empty handshaking signals that are connected through the switches to enable processing to be dynamically triggered.

### 3.5 Run Time Interpreter

The JITA has a run time mechanism to interpret the function calls generated by the compiler to compose accelerators. Using the interpreter allows the data flow graph information generated by the back end of the DSL compiler to remain portable, similar to portable Java Byte Code. Table 3.1 shows the instructions the compiler produces to represent the data and control flow graphs. The output of the backend generator called Virtual Accelerator Machine (VAM) language. Just as a Java Virtual Machine (JVM) provides the run time mechanisms needed to implement the policies defined by the Java Byte Code, the VAM run time interpreter provides the run time executables specific to a particular organization of partially reconfigurable slots.

The interpreter allows the same output from the compiler to remain portable and used over different configurations of reconfigurable slots, and logic families. The run time interpreter, also,

provides the separation between policy and mechanism to enable the same data flow graph to be mapped and run on any configuration of reconfigurable.

Figure 3.5: VAM Run Time Interpreter Configuration Steps.

The interpreter calls listed in Table 3.1 and shown in the example in Figure 3.2 make no commitment on how partially reconfigurable regions should be sized, configured or organized within a programmable interconnect network. As an example the *VAM\_GET\_PR* instruction in Figure 3.2 is a request to the run time system to get a free partially reconfigurable slot. The *VAM\_SET\_PR* instruction directs the run time system to load a slot with a particular bitstream, and

the *VAM\_ROUTE* instruction requests the run time system to connect a data path between slots. How these commands are implemented are clearly dependent on how each FPGA is configured. The approach defines a run time interpreter to perform these platform specific operations. In this fashion the run time interpreter provides the same operation as a Java Virtual Machine with the platform independent VAM calls produced by the compiler taking the place of portable Java Byte Codes.

For example, Figure 3.7 shows how the run time interpreter constructs the accelerator shown in Figure 3.2 into the  $3 \times 3$  tile array of partially reconfigurable slots shown in Figure 3.3.

Figure 3.6: Design Portability with JIT.

| Table 3.1: VAM Calls    |              |                                                                                                                             |                                                                                                   |  |  |

|-------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| Туре                    | Name         | Semantics                                                                                                                   | Description                                                                                       |  |  |

| PR Region<br>Operations | VAM_GET_PR   | <pre>bool VAM_GET_PR (     vam_table_t *VAM_TABLE,     int *nPR);</pre>                                                     | Requesting a free<br>PR slot.                                                                     |  |  |