University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

5-2017

# Exploiting Hardware Abstraction for Parallel Programming Framework: Platform and Multitasking

Hongyuan Ding University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Hardware Systems Commons

## Citation

Ding, H. (2017). Exploiting Hardware Abstraction for Parallel Programming Framework: Platform and Multitasking. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/1985

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact uarepos@uark.edu.

## Exploiting Hardware Abstraction for Parallel Programming Framework: Platform and Multitasking

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a Concentration in Computer Engineering

by

Hongyuan Ding Shandong University Bachelor of Engineering in Electrical Engineering, 2012 University of Arkansas Master of Science in Computer Engineering, 2015

> May 2017 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council

Dr. Miaoqing Huang Dissertation Director

Dr. David Andrews Committee Member

Dr. Wing Ning Li Committee Member

Dr. Zhong Chen Committee Member

#### Abstract

With the help of the parallelism provided by the fine-grained architecture, hardware accelerators on Field Programmable Gate Arrays (FPGAs) can significantly improve the performance of many applications. However, designers are required to have excellent hardware programming skills and unique optimization techniques to explore the potential of FPGA resources fully. Intermediate frameworks above hardware circuits are proposed to improve either performance or productivity by leveraging parallel programming models beyond the multi-core era.

In this work, we propose the PolyPC (**Poly**morphic **P**arallel **C**omputing) framework, which targets enhancing productivity without losing performance. It helps designers develop parallelized applications and implement them on FPGAs. The PolyPC framework implements a custom hardware platform, on which programs written in an OpenCL-like programming model can launch. Additionally, the PolyPC framework extends vendor-provided tools to provide a complete development environment including intermediate software framework, and automatic system builders. Designers' programs can be either synthesized as hardware processing elements (PEs) or compiled to executable files running on software PEs. Benefiting from nontrivial features of re-loadable PEs, and independent group-level schedulers, the multitasking is enabled for both software and hardware PEs to improve the efficiency of utilizing hardware resources.

The PolyPC framework is evaluated regarding performance, area efficiency, and multitasking. The results show a maximum  $66 \times$  speedup over a dual-core ARM processor and  $1043 \times$  speedup over a high-performance MicroBlaze with  $125 \times$  of area efficiency. It delivers a significant improvement in response time to high-priority tasks with the priority-aware scheduling. Overheads of multitasking are evaluated to analyze trade-offs. With the help of the design flow, the OpenCL application programs are converted into executables through the front-end source-to-source transformation and back-end synthesis/compilation to run on PEs, and the framework is generated from users' specifications.

©2017 by Hongyuan Ding All Rights Reserved

## Acknowledgements

I would like to thank my committee members, especially my advisor Dr. Miaoqing Huang for providing constructive advice and necessary facilities for my research.

I would like to thank my best friends in the US, China, and Europe. I'm thankful that we could be together to explore this wonderful world by supporting each other and sharing our happiness and sadness.

I would like to thank my beloved parents and relatives for their love, continued support, and understanding. I never expect a more important relationship other than that between family members.

I would like to believe that the algorithm is science; while the framework is art, which reflects designer's understanding of aesthetics.

## Contents

| 1 | Intr | oductio                                                      | n                                    | 1    |  |  |  |  |  |

|---|------|--------------------------------------------------------------|--------------------------------------|------|--|--|--|--|--|

|   | 1.1  | Multi-                                                       | core Era and Beyond                  | . 1  |  |  |  |  |  |

|   | 1.2  | Hetero                                                       | geneous Computing                    | . 3  |  |  |  |  |  |

|   | 1.3  |                                                              | as a Candidate                       |      |  |  |  |  |  |

|   | 1.4  | Statem                                                       | nents and Contributions              | . 6  |  |  |  |  |  |

|   | 1.5  |                                                              | tation Organization                  |      |  |  |  |  |  |

| 2 | Bac  | kground                                                      | ds                                   | 8    |  |  |  |  |  |

| - | 2.1  | -                                                            | el Programming Models                |      |  |  |  |  |  |

|   | 2.2  |                                                              | penCL Standard Overview              |      |  |  |  |  |  |

|   | 2.2  | 2.2.1                                                        | Platform Model                       |      |  |  |  |  |  |

|   |      | 2.2.1                                                        | Execution Model                      |      |  |  |  |  |  |

|   |      | 2.2.2                                                        | Memory Model                         |      |  |  |  |  |  |

| • |      |                                                              | -                                    |      |  |  |  |  |  |

| 3 |      |                                                              | Architecture of the PolyPC Framework | 20   |  |  |  |  |  |

|   | 3.1  |                                                              | ntroduction of Zynq Architecture     |      |  |  |  |  |  |

|   | 3.2  | -                                                            | C Architecture Overview              |      |  |  |  |  |  |

|   | 3.3  |                                                              | ry Hierarchy                         |      |  |  |  |  |  |

|   | 3.4  |                                                              | ierarchy                             |      |  |  |  |  |  |

|   | 3.5  | -                                                            | ute Device Architecture              |      |  |  |  |  |  |

|   |      | 3.5.1                                                        | PolyTask Table Queue                 |      |  |  |  |  |  |

|   |      | 3.5.2                                                        | Mutex Manager                        |      |  |  |  |  |  |

|   |      | 3.5.3                                                        | Partial Reconfiguration Controller   |      |  |  |  |  |  |

|   | 3.6  | Group                                                        | Architecture                         |      |  |  |  |  |  |

|   |      | 3.6.1                                                        | Group Interface                      |      |  |  |  |  |  |

|   |      | 3.6.2                                                        | Processing Elements                  | . 35 |  |  |  |  |  |

|   |      | 3.6.3                                                        | Execution Sequence                   | . 36 |  |  |  |  |  |

|   | 3.7  | Trace S                                                      | Subsystem                            | . 37 |  |  |  |  |  |

|   | 3.8  | Evalua                                                       | tion and Results                     | . 38 |  |  |  |  |  |

|   |      | 3.8.1                                                        | Benchmarks                           | . 39 |  |  |  |  |  |

|   |      | 3.8.2                                                        | Experimental Setup                   | . 40 |  |  |  |  |  |

|   |      | 3.8.3                                                        | Resource Utilization                 | . 43 |  |  |  |  |  |

|   |      | 3.8.4                                                        | Performance Analysis                 |      |  |  |  |  |  |

|   | 3.9  | Relate                                                       | d Work                               |      |  |  |  |  |  |

|   |      | 3.9.1                                                        | HLS-based Systems                    |      |  |  |  |  |  |

|   |      | 3.9.2                                                        | Processor Substrate                  |      |  |  |  |  |  |

| 4 | Palv | mornhi                                                       | ie Multitasking                      | 55   |  |  |  |  |  |

| 7 | 4.1  | Polymorphic Multitasking         4.1       Polymorphic Tasks |                                      |      |  |  |  |  |  |

|   | 7.1  | 4.1.1                                                        | Hardware Threads                     |      |  |  |  |  |  |

|   |      |                                                              | Software Threads                     |      |  |  |  |  |  |

|   |      | <b>T</b> . I.4                                               |                                      |      |  |  |  |  |  |

|     | 4.2    | Polym    | orphic Scheduling                       |

|-----|--------|----------|-----------------------------------------|

|     |        | 4.2.1    | Architectural Supports for Multitasking |

|     |        | 4.2.2    | Priority-aware Scheduling Policy 61     |

|     | 4.3    | Evalua   | ation and Results                       |

|     |        | 4.3.1    | Experimental Setup                      |

|     |        | 4.3.2    | Result Analysis                         |

|     |        | 4.3.3    | Resource Utilization                    |

|     | 4.4    | Relate   | d Work                                  |

|     |        | 4.4.1    | Reconfigurable Systems                  |

|     |        | 4.4.2    | Task Scheduling and Placement    76     |

| 5   | Desi   | ign Flov | v 79                                    |

|     | 5.1    | 0        | rm Generation                           |

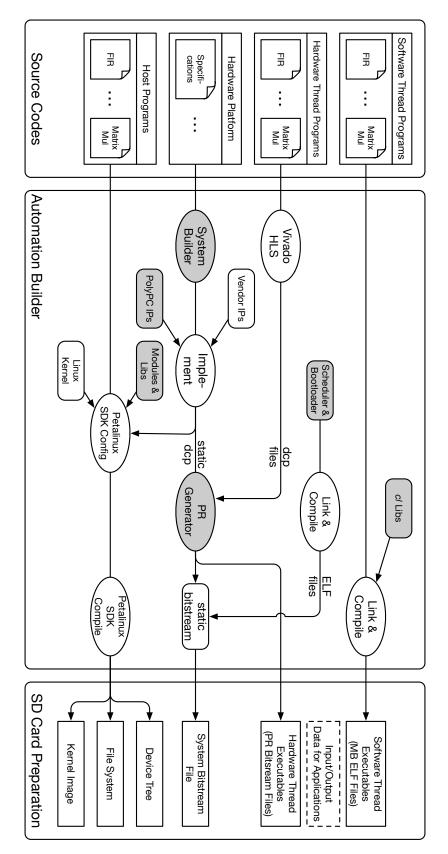

|     |        | 5.1.1    | Automation Building Flow                |

|     | 5.2    | Interm   | ediate Libraries                        |

|     |        | 5.2.1    | Memory Management                       |

|     |        | 5.2.2    | Dynamic Executable Loader               |

|     | 5.3    | Progra   | mming OpenCL Applications               |

|     |        | 5.3.1    | Execution Model                         |

|     |        | 5.3.2    | Host Programs                           |

|     |        | 5.3.3    | Kernel Programs                         |

|     | 5.4    | Relate   | d Work                                  |

|     |        | 5.4.1    | Executables for PolyTasks               |

|     |        | 5.4.2    | High-level Synthesis Approaches         |

|     |        | 5.4.3    | Automatic System Builder                |

| 6   | Con    | clusion  | s 104                                   |

| Ū   | 6.1    |          | e Work                                  |

|     | 011    | 6.1.1    | Adoption of More OpenCL Features        |

|     |        | 6.1.2    | Intelligent Scheduling                  |

| D   | eferen | 005      | 108                                     |

| 170 |        | 1003     | 108                                     |

## List of Figures

| 1.1                                                          | Heterogeneity Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                                                                        |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3                                            | OpenCL Platform Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13<br>15<br>18                                                                                           |

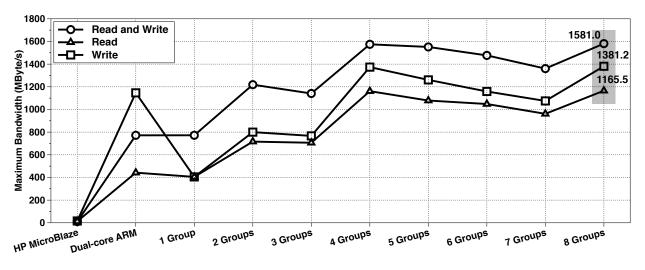

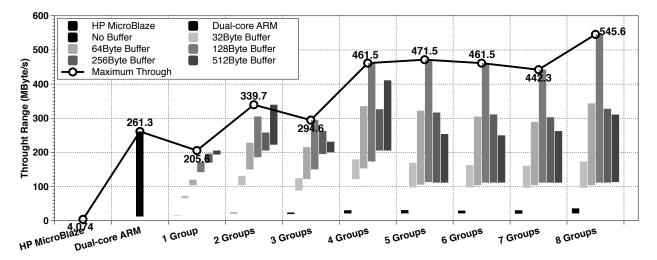

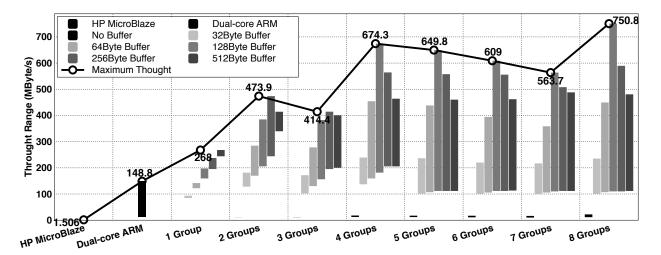

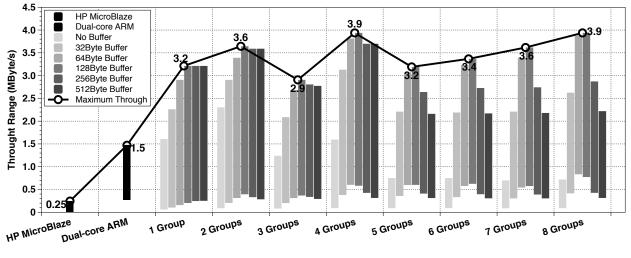

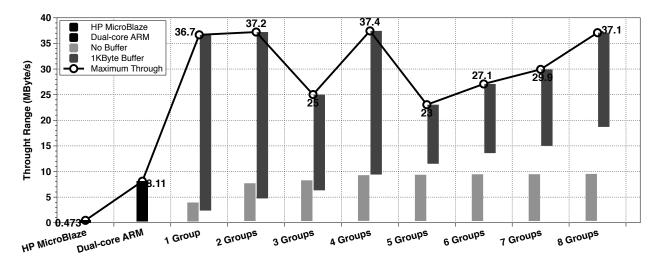

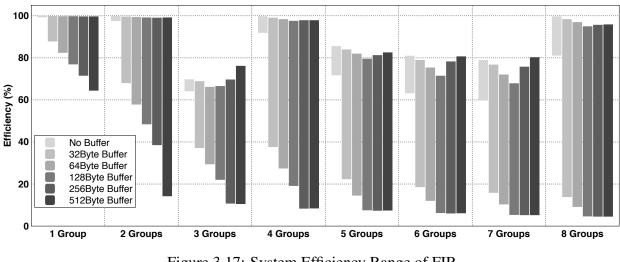

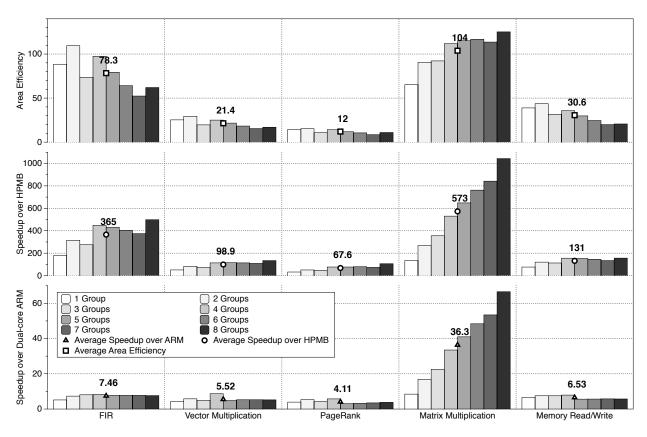

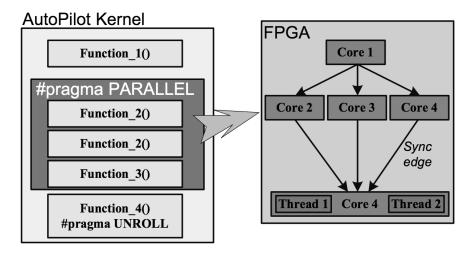

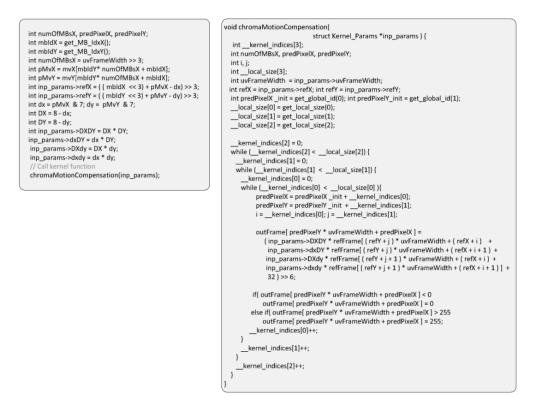

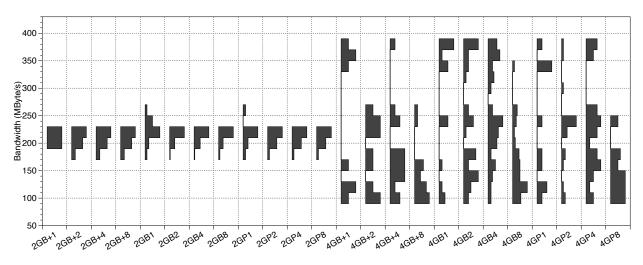

| 3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18 | Zynq SoC ArchitecturePolyPC Platform ArchitecturePolyPC Memory HierarchyBus Hierarchy of the Compute DeviceStructure of PolyTask Table RAMMutex Manager Algorithm for One Mutex LockPolyTask Context Switching DemonstrationGroup ArchitectureID Generator and DispatcherMicroBlaze Subsystem ArchitectureGroup Execution SequenceMemory BandwidthPerformance Range of FIRPerformance Range of Matrix MultiplicationSystem Efficiency Range of FIRSpeedup and Area Efficiency over ARM and HP MicroBlaze | 21<br>22<br>24<br>25<br>27<br>30<br>30<br>32<br>34<br>36<br>37<br>44<br>45<br>46<br>46<br>47<br>47<br>49 |

|                                                              | AutoPilot C Programming Model from [85]SOpenCL Front-end Code Transformation from [83]                                                                                                                                                                                                                                                                                                                                                                                                                   | 50<br>51                                                                                                 |

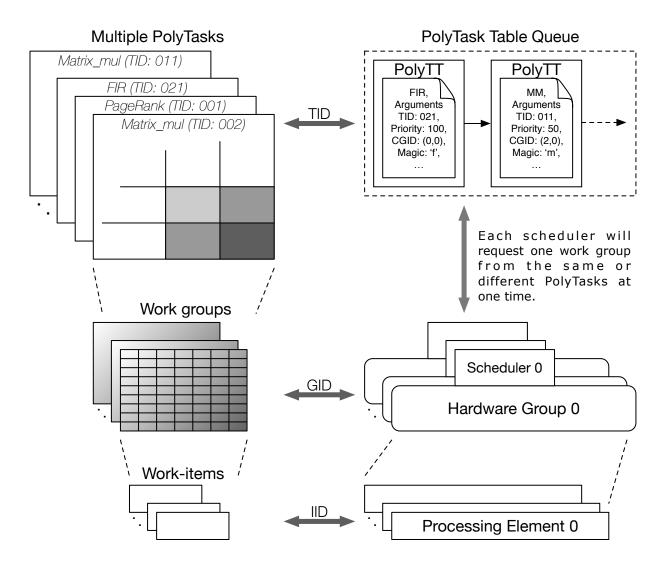

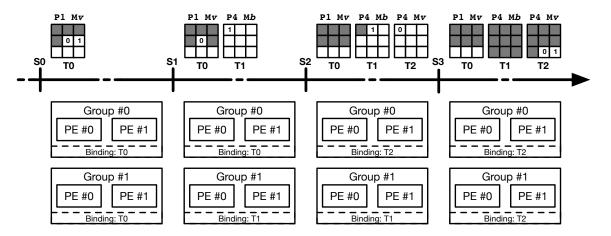

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9  | PolyTask Mapping with Hardware Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56<br>58<br>60<br>62<br>67<br>68<br>70<br>71<br>73                                                       |

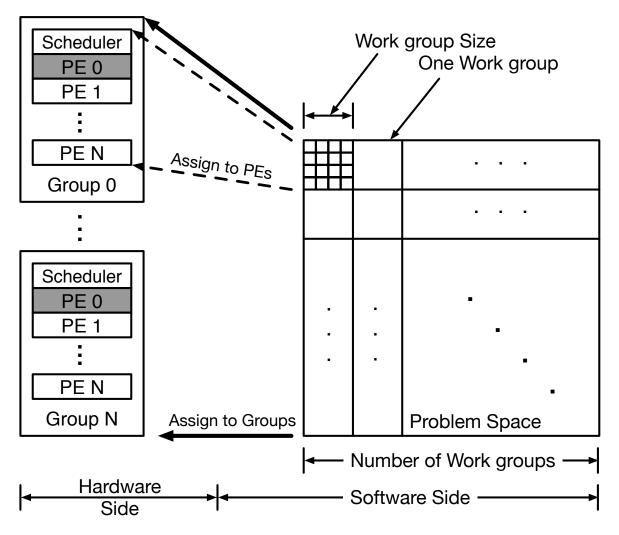

| 5.1<br>5.2                                                   | Platform Generation FlowProblem Space Mapping in Hardware Side                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80<br>89                                                                                                 |

## List of Tables

| 2.1 | Allocation and Accessibility to Memory Objects within Memory Hierarchy | 19  |

|-----|------------------------------------------------------------------------|-----|

| 3.1 | Accessibility of Registers on the Mutex Manager for a Mutex Lock       | 28  |

| 3.2 | Hardware Platform Configurations                                       | 41  |

| 3.3 | Benchmark Configurations                                               | 42  |

| 3.4 | System Resource Utilization                                            | 43  |

| 3.5 | hPEs Resource Utilization                                              |     |

| 4.1 | Experiment Configurations                                              | 64  |

| 4.2 | Partial Reconfiguration Bandwidth (unit: MB/s)                         | 67  |

| 4.3 | Numbers of Work Groups that Hardware Groups Execute                    | 71  |

| 4.4 | Overhead Breakdown of Each Hardware Group (unit: ms)                   | 72  |

| 4.5 | Reconfigurable System Resource Utilization                             | 74  |

| 5.1 | Intermediate Libraries of PolyPC Framework                             | 84  |

| 5.2 | Program Header within an ELF File                                      | 87  |

| 5.3 | Sections within an ELF File                                            | 87  |

| 5.4 | Overview of Selected High-level Synthesis Tools                        | 100 |

#### **Glossary and Definitions**

- CU Compute Unit. A compute device in the OpenCL may consist of CUs.

- **PE** Processing Element. Multiple PEs in both OpenCL standard and PolyPC framework comprise a CU. Work-items execute on PEs.

- **hPE** Each PE can be either a dedicated hardware accelerator or a general-purpose processor. The accelerator PE is called an hPE, and the processor PE is called an sPE.

sPE See hPE.

- **Group** A CU is called a group in the PolyPC framework. Sometimes it is called as hardware groups.

- **PS** Processing System. A complete Zynq device consists of the PS, and the programmable logic (PL). The PS part is a hard-copy dual-core ARM processor. The PL part is fabricated as traditional FPGAs.

- PL Programmable Logic. See PS.

- **PR** Partial Reconfiguration. PR techniques enable reprogramming part of FPGA fabrics without affecting others.

- **Module** It usually refers to a hardware component that can be either from vendors or users. It can be embedded into FPGA EAD tools to comprise a system.

- **PolyTask** Polymorphic Task. A PolyTask is associated with a kernel program and consists of multiple threads. It can only run on compute device.

- **PolyTT** PolyTask Table. It records execution information to run a PolyTask and to switch between them.

- Hardware Thread A thread associated with a work-item within the kernel program is executed

on a PE. As a PE can be either an sPE or an hPE, a thread is called as a software thread or a hardware thread when it is executed on an sPE or an hPE, respectively.

## Software Thread See Hardware Thread.

- **VSM** Virtual Socket Manager. The PR controller works with multiple VSMs), each of which is associated with a PR region.

- **ICAP** Internal Configuration Access Port.

- **PCAP** Processor Configuration Access Port.

- **API** Application Programming Interface. The defined interface of a piece of software, often a library or operating system.

- **CPU** Central Processing Unit. A programmable hardware component often referred to as processor or core.

- **DMA** Direct Memory Access. Often referring to hardware devices that can perform memory-tomemory operations without processor assistance.

- **DSP** Digital Signal Processor. A processor specialized for signal processing, often featuring vector and multiply-accumulate operations.

- **FIFO** First-In, First-Out. A hardware component or data structure that exhibits First-In, First-Out behavior (e.g. a queue).

- **FPGA** Field Programmable Gate Array. A hardware chip whose functionality can be changed post-fabrication.

- **GPGPU** General-purpose Graphics Processing Unit. A hardware device specialized for data parallelism computation.

- ACC Hardware Accelerator. Dedicated hardware logics that are designed to finish a particular task.

#### Chapter 1

#### Introduction

#### 1.1 Multi-core Era and Beyond

Before the general-purpose computing community decided to shift to multi-core systems, general-purpose processors within the computer system kept pushing to their limits in terms of processing technology, and advanced microarchitecture. Benefiting from the periodic device feature size scaling predicted by Moore's law (Dennard scaling [24]), general-purpose processors were improving the performance accordingly for decades. Besides, with the help of multiple abstractions of software programming such as operating systems, compilers and programming models, general-purpose computer systems provide designers significant productivity, flexibility and additional performance improvement.

However, the transistor cannot shrink forever [63]. By 2004, the general-purpose computing community began to increase the number of cores to extend Moore's law instead of squeezing more performance out of a single-core processor [39]. This mainly resulted from the failure of Dennard scaling. The slowed processor clock frequency scaling that did not scale along with the feature size anymore, which thereby limits the increasing performance of a single-core processor. The overall performance is improved by parallelizing workloads on multi-core processors. Besides the processor clock frequency, the supply voltage fails to scale along with the feature size as well [37], and thus power density is increasing. As the number of cores increases, the incapability of heat dissipation system may prevent fully powering of all cores at the same time, requiring some cores to run at low speed not to exceed the processor thermal design power (TDP) [36, 90]. This phenomenon is called *dark silicon*: transistors that can be used on a chip are far less than the economic manufacturability sweet-spot [10, 38, 46].

Another constraint contributing to the shift to multi-core systems is the nearly-stalled

improvement of processors' microarchitecture. Advanced techniques applied in the general-purpose single-core processor, such as superscalar execution, deeper pipelines, and efficient cache design, have exploited its potential. Efforts to perfect the processors' microarchitecture design obtain fewer gains over generations.

The transition to multi-core era seemed to be inevitable at first but was forced indeed. This raises the following two questions:

#### 1. How much more performance left in multi-core processors in the future? In the

multi-core era key questions that need to answer are if the performance gain is worth scaling down or if we can scale down in the future after the failure of Moore's law. But one thing for sure is without breakthroughs of processing technologies multi-core systems (e.g., CPU and GPU) cannot benefit from performance gains that they used to have in the single-core era. Even considering parallel programming optimization along with processing scaling, the average annual performance gain is about 16% to 23% before 8 nm emerging in the short future [36, 37]. Besides power constraints, the community can find alternative solutions in realms such as multi-core microarchitecture, specific acceleration, and programming methods.

2. How much speedup we can get from parallelism on multi-core processors? For decades, the single-core processor and sequential programming models dominated the general-purpose computing and gave its way in the multi-core era. However multi-core systems bring new challenges for software programming, and it takes time for programmers and software techniques to catch up with new trends. Amdahl's law provides a method to estimate how much speedup obtained through parallelism. But what matters is how to parallelize applications. Programming models are evolving to meet new demands. In those symmetric multiprocessor (SMP) systems, standards interfaces, such as Posix threads (PThreads) or OpenMP, are used by software programmers [48, 82]. In distributed systems where there are fundamental differences from multi-core systems, programmers are able to

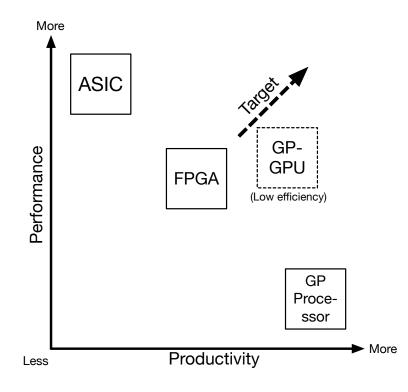

Figure 1.1: Heterogeneity Considerations

use to various standards such as message passing interface (MPI) and CORBA [101]. In recent years, domain-specific models such as MapReduce [23] and Spark [97] are used to handle big data analysis. However, speedup of small fractions of an application may be negligible due to overheads of these programming models. For heterogeneous multi-core systems, the standard SMP programming models may be unsuitable. Furthermore, some applications, such as non-computation intensive applications, run well on single-core processors; while computation intensive applications are able to have much speedup on SIMD systems such as emerging general-purpose graphic processing units (GPGPUs).

## **1.2 Heterogeneous Computing**

In the multi-core era, one computing resource cannot meet all requirements in terms of performance, power efficiency, and productivity. The community is seeking solutions through heterogeneity. One of the most promising approaches is to leverage specification.

For a particular task, custom logic via application-specific integrated circuits (ASICs) can achieve up to three orders of magnitude differences in both power efficiency and performance over general-purpose processors [17, 29, 32, 44]. But the heavy use of ASICs on general applications remains many challenges. This is reflected in productivity and flexibility. Designing ASICs requires much more efforts than on general-purpose processors and implementing frequently-changed applications is infeasible. Programmable accelerators (i.e., FPGAs and GPGPUs) provide the trade-off between the performance of ASICs and the productivity of general-purpose processors (see Figure 1.1). GPGPUs leverage SIMD to accelerate data-intensive applications; while FPGAs accelerate applications through programmable logics. GPGPUs are still based on massive simple general-purpose processors. By using parallel programming models (i.e., CUDA and OpenCL), they can achieve noticeable productivity even compared to general-purpose processors. But recent research work and industrial trends reveal that FPGAs are better at web services requiring low-latency and high-frequency requests than GPGPUs in data centers [15, 66, 88].

## **1.3 FPGA as a Candidate**

With the help of hardware accelerators, FPGAs are able to significantly improve the performance of many applications due to the parallelism provided by the fine-grained architecture. However, the dearth of flexibility and programmability affects their widespread adoption. In order to fully explore the computing potential of FPGA resources, designers are required to have excellent hardware programming skills and special optimization techniques. Usually, on a single computer system, software programs can be compiled to binaries running on processors and software programmers do not need to design application-specific hardware architectures. On the contrary, programming hardware circuits by using hardware description languages (HDLs) on FPGAs requires comprehensive hardware-oriented knowledge including pipelining, clock domains, data flows, and memory managements. Therefore, designing hardware accelerators usually results in

particular hardware architecture per application.

FPGA devices have grown to a point where advanced processing technology is adopted to achieve high capacity. State-of-the-art FPGAs can accommodate complicated heterogeneous systems. Thus, hardware designers are willing to utilize extra resources to trade for flexible architectures and productive design flows [3]. One of the most promising approaches is parallel computing platforms with multiple processing elements such as Graphic Processing Units (GPUs) and Multiprocessor System-on-Chip (MPSoC). Parallel programming languages such as OpenCL are used to program these platforms efficiently and productively. OpenCL is an open standard for parallel computing frameworks across GPUs, CPUs, and even FPGAs. OpenCL introduces several models including execution, platform, memory, and programming models. These models provide the unified hardware and software abstractions for programmers. Designers are released from the burden of designing hardware architectures, and productivities and efficiency are improved significantly.

One way to address the programmability of hardware logics within FPGAs is to use High-level Synthesis (HLS) techniques. In [85], applications' parallelism is expressed in a kernel program that is directly synthesized into FPGA logics. This technique is very efficient in terms of performance and power consumptions. Productivity is satisfying since designers do not have to dig into the hardware details. But when multiple kernels are launched, they have to be synthesized multiple times, which is significantly time-consuming. Besides, when one kernel is changed, the whole platform has to be synthesized again. Other approaches target using soft processors. They can be configured as many-core systems or overlays by using customized processors [65, 91] or multiprocessor systems with vendor-provided processors [27, 28, 31]. Recent works also focus on dedicated soft-GPU cores on FPAGs [3]. These approaches increase productivity by leveraging general-purpose processors on a pre-defined hardware architecture. Comparing to HLS techniques that every application has their logics, soft-processor-based solutions change different kernels by compiling, which is usually much faster than synthesizing the same functionality. However, the

trade-off is that they lose performance and area efficiency compared to dedicated logics.

However, heterogeneous systems on FPGAs still face the following challenges:

- Can platform specification details be removed from users' codes and be encapsulated within an automatic system builder?

- Can the complexity of designing parallel applications be reduced by applying standard parallel programming models on FPGAs?

- What are the benefits when heterogeneous computing resources are used on FPGAs?

- Can the system efficiency be increased by introducing the priority-aware multitasking?

#### 1.4 Statements and Contributions

In this work, we want to answer the questions raised in the previous section by proposing the PolyPC (**Poly**morphic **P**arallel Computing) framework. The PolyPC framework targets improving productivity without losing performance when designers want to implement their parallelized applications on FPGAs. The PolyPC framework implements a custom hardware platform, along with software intermediate framework and automatic system builders. On the one hand, designers can write their programs by using the easy-to-use OpenCL-like programming model to optimize their applications. Firstly, the automatic system builder takes the specifications to generate the hardware platform. Then the software programs are either synthesized into hardware accelerators or compiled to executable files running on general-purpose processors. On the other hand, different from previous work that the whole hardware system is generated per application, the PolyPC framework enables partially reloaded processing elements (PEs) for both sPEs and hPEs. Therefore, PEs can be generated off-line without changing the static system and loaded into the system during runtime environment. Benefiting from the flexibility of re-loadable PEs, the context switching feature is enabled for PEs to improve the efficiency to utilize hardware resources. The priority-aware scheduling policy is used to provide fast responses to tasks with high priorities.

## **1.5** Dissertation Organization

In the next chapter, we discuss the background in terms of parallel programming models and detailed illustration of the OpenCL standard working on the PolyPC framework. Chapter 3, Chapter 4 and Chapter 5 provide discussions of approaches for the PolyPC framework to address questions raised in this chapter.

The hardware architecture of the PolyPC framework, as well as the evaluation of pure performance part, is talked about in Chapter 3. Chapter 4 discusses the polymorphic multitasking feature. Besides, experiments and results related to this feature are addressed as well. Chapter 5 demonstrates how to improve the productivity to implement parallel applications on the PolyPC framework by using the design flow. Finally, Chapter 6 concludes this work and discusses the future work. **Chapter 2**

#### **Backgrounds**

#### 2.1 Parallel Programming Models

A parallel programming model is an abstraction of the computer architecture [25]. There are many programming models for parallel computing because how to put several processors or computing units together to form a complete system is different from one programming models to another. Besides, it is difficult to separate one particular programming model to its hardware implementation. In other words, the same programming model may have different software compilation flows and hardware architectures.

**POSIX Threads** In this model, several concurrent execution paths (threads) can be controlled independently. A thread is a lightweight process having its own program counter (PC) and execution stack [7]. The model is very flexible, but it usually associated with shared memory and operating systems.

The Pthreads, or Portable Operating System Interface (POSIX) Threads, is a set of C programming language types and procedure calls [11, 55, 60]. Pthreads is implemented as a header (pthread.h) and a library for creating and manipulating each thread. The Pthreads library provides functions for creating and destroying threads and for coordinating thread activities via constructs designed to ensure exclusive access to selected memory locations (locks and condition variables). This model is especially appropriate for the fork/join parallel programming pattern [75].

In general, Pthreads is not recommended as a parallel program development technology. While it has its place in specific situations, and in the hands of expert programmers, the

unstructured nature of Pthreads makes the development of correct and maintainable programs difficult. Also, recall that the number of threads is not related to the number of processors available. These characteristics make Pthreads programs not scalable to a large number of processors [93].

**OpenMP** OpenMP [16] is a shared memory application programming interface (API) whose aim is to ease shared memory parallel programming. The OpenMP multithreading interface [82] is specifically designed to support high-performance computing (HPC) programs. It is also portable across shared memory architectures. OpenMP differs from Pthreads in several significant ways. While Pthreads is purely implemented as a library, OpenMP is implemented as a combination of a set of compiler directives, pragmas, and a runtime providing both management of the thread pool and a set of library routines. These directives instruct the compiler to create threads, perform synchronization operations, and manage shared memory. Therefore, OpenMP does require specialized compiler support to understand and process these directives.

In OpenMP, the use of threads is highly structured because it was designed specifically for parallel applications. In particular, the switch between sequential and parallel sections of code follows the fork/join model [7]. This is a block-structured approach for introducing concurrency. A single thread of control splits into some number of independent threads (the fork). When all the threads have completed the execution of their specified tasks, they resume the sequential execution (the join). A fork/join block corresponds to a parallel region, which is defined using the *PARALLEL* and *END PARALLEL* directives.

The characteristics of OpenMP allow for a high abstraction level, making it well suited for developing HPC applications in shared memory systems. The pragma directives make it easy to obtain the concurrent code from serial codes. In addition, the existence of specific directives eases parallelizing loop-based code.

**MPI** Message Passing is a parallel programming model where communication between processes is done by interchanging messages. This is a natural model for a distributed memory system, where communication cannot be achieved by sharing variables. Over time, a standard has evolved and dominated for this model: the Message Passing Interface (MPI). MPI is a specification for message passing operations [42, 42, 84, 93]. MPI is a library, not a language. It specifies the names, calling sequences, and results of the subroutines or functions to be called from Fortran, C or C++ programs. Thus, the programs can be compiled with ordinary compilers but must be linked with the MPI library.

In this model, the processes executed in parallel have separate memory address spaces. Communication occurs when part of the address space of one process is copied into the address space of another process. This operation is cooperative and occurs only when the first process executes a send operation and the second process executes a receive operation. In MPI, the workload partitioning and task mapping have to be done by the programmer, similarly to Pthreads. Programmers have to manage what tasks are to be computed by each process.

In summary, MPI is well suited for applications where portability, both in space (across different systems existing now) and in time (across generations of computers), is important. MPI is also an excellent choice for task-parallel computations and for applications where the data structures are dynamic, such as unstructured mesh computations.

**CUDA** CUDA is a parallel programming model developed by NVIDIA [52]. The CUDA model is designed to develop applications scaling transparently with the increasing number of processor cores provided by the GPUs [49, 62]. CUDA provides a software environment that allows developers to use C as a high-level programming language. For CUDA, a parallel system consists of a host (i.e., CPU) and a computation resource or device (i.e., GPU). The computation of tasks is done in the GPU by a set of threads running in parallel. The GPU threads architecture consists of a two-level hierarchy, namely the block and the grid.

The block is a set of tightly coupled threads, each identified by a thread ID. On the other hand, the grid is a set of loosely coupled blocks with similar size and dimension. There is no synchronization between the blocks, and a single GPU handles an entire grid. The GPU is organized as a collection of multiprocessors, with each multiprocessor responsible for managing one or more blocks in a grid. A block is never divided across multiple multiprocessors. Threads within a block can cooperate by sharing data through some shared memory, and by synchronizing their execution to coordinate memory accesses.

Worker management in CUDA is done implicitly. That is, programmers do not manage thread creations and destructions. They just need to specify the dimension of the grid and block required to process an individual task. Workload partitioning and worker mapping in CUDA is done explicitly. Programmers have to define the workload to run in parallel by using the function *Global Function* and specifying the dimension and size of the grid and of each block.

A recent initiative by Intel is called Knights Ferry [95, 103], and is being developed under the Intel Many Integrated Core (MIC) architecture. Knight Ferry is implemented on a PCI card with 32 x86 cores. The MIC supports a more classical coherent shared memory parallel programming paradigm than CUDA. Moreover, it will be programmed using native C/C++ compilers from Intel.

**OpenCL** OpenCL [43] is an open royalty-free standard for general purpose parallel programming across CPUs, GPUs, and other processors. Primarily, OpenCL distinguishes between the devices (usually GPUs or CPUs) and the host (CPU). The idea behind OpenCL is to write kernels (functions that execute on OpenCL devices) and APIs for creating and managing these kernels. The kernels are compiled for the targeted device at runtime, during the application execution. This enables the host application to take advantage of all the computing devices in the system.

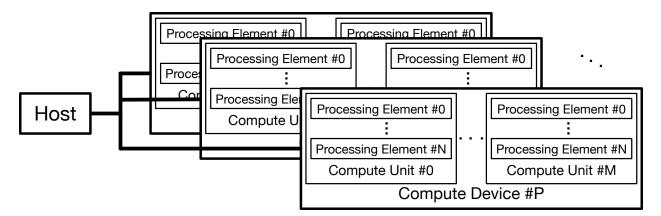

The OpenCL operational model can be described as four interrelated models: the platform,

execution, memory, and programming models. The platform model is viewed from a hierarchical and abstract perspective. In this model, a host coordinates execution, transferring data to and from an array of Compute Devices. Each Compute Device is composed of an array of Compute Units. Each Compute Unit is comprised of an array of Processing Elements.

Execution of an OpenCL program involves simultaneous execution of multiple instances of a kernel on one or more OpenCL devices. A kernel is the primary executable code unit. It is called work-item and has a unique ID. Work-items can be organized into work groups for synchronization and communication purposes. The different executions of a program are queued and controlled by the host application. This last sets up the context in which the kernels run, including memory allocation, data transfer among memory objects, and the creation of command queues used to control the sequence in which commands are executed. However, the programmer is responsible for synchronizing any necessary execution order.

OpenCL has been designed to be used not only in GPUs but also in other platforms like multi-core CPUs. Thus, it can support both data parallel [47], and task parallel [76] programming patterns [75], which are well suited for GPUs and CPUs architectures, respectively.

**DirectCompute** DirectCompute is Microsofts approach to GPU programming. DirectCompute is a part of the Microsoft DirectX APIs collection [50]. In fact, it is also known as DirectX11 Compute Shader. It was initially released with the DirectX 11 API but runs on both DirectX 10 and DirectX 11 graphics processing units. In particular, it was introduced thanks to the new Shader Model 5 [51] provided in DirectX 11, which allows computation independently of the graphic pipeline, therefore suitable for GPGPUs. The main drawback of DirectCompute is that it only works on Windows platforms.

Array Building Blocks Intels Array Building Blocks (ArBB) provides a generalized

vector-parallel-programming solution for data-intensive mathematical computation [40, 56, 61].

Users express computations as operations on arrays and vectors. ArBB comprises a standard C++

Figure 2.1: OpenCL Platform Model

library interface and a powerful runtime. A just-in-time (JIT) compiler supplied with the library translates the operations into the target-dependent code, where a target could be the host CPU or an attached GPU. As for runtime, ArBB uses Intels Threading Building Blocks [57], which contributes to abstract platform details and threading mechanisms for scalability and performance. Intels ArBB can run data-parallel vector computations on a possibly heterogeneous system. By design, Intel ArBB prevents parallel programming bugs such as data races and deadlocks.

## 2.2 The OpenCL Standard Overview

OpenCL is an open industrial standard providing the low-level hardware abstraction plus a framework to support programming on heterogeneous hardware platforms [43]. The OpenCL framework can be described by using several models:

- Platform model.

- Memory model.

- Execution model.

#### 2.2.1 Platform Model

The platform model is an abstraction describing how OpenCL views the hardware. As shown in Figure 2.1, the OpenCL platform model consists of one host processor and one or more compute devices, each of which contains multiple compute units (CUs). A single compute unit is comprised of multiple processing elements (PEs), within which the computation occurs. The OpenCL framework can be deployed on heterogeneous compute devices, such as graphics processing units (GPUs), field-programmable gate arrays (FPGAs), and even central processing units (CPUs). The specific hardware implementation of the platform model is different per vendor even for the same compute device [99]. Four major commercial solutions are listed as following:

- NVIDIA GPUs [21]. In a NVIDIA GPU, the compute unit is called as a streaming multiprocessor (SM). A streaming multiprocessor consists multiple stream processor (SP) cores. In modern GPU architecture, each SP core is highly multithreaded. SMs employ the NVIDIA-called SIMT (single-instruction, multiple-thread) architecture. Threads are divided into groups of 32 threads, which are called warps. Warps are executing on SMs, and further on SIMD units in lockstep. To improve throughputs, warps are scheduled and interleave their execution through the pipeline of SIMT units.

- AMD GPUs [5]. AMD GPU devices vary in architectures through generations. For devices in Evergreen and Northern Islands families, a compute unit is called a SIMD (single-instruction, multiple-data) engine that consists of multiple stream cores (SCs). SCs execute VLIW (very long instruction word) 4 (for Northern Islands) or 5 (for Evergreen) wide instructions from one wavefront (similar to warps in NVIDIA devices) in lockstep. For devices in Southern Islands family, which is also known as GCN (Graphic Core Next), each compute unit has one scalar unit and four vector unit. Each vector unit contains an array of 16 PEs and works as the SIMD architecture.

Figure 2.2: OpenCL Execution Model

- Intel FPGAs [94]. Different from how parallelism is revealed in GPUs, Intel FPGAs use the concept of pipeline parallelism. OpenCL programs are transformed into dedicated and pipelined hardware circuits on FPGAs by using their SDK tools. A PE is called a kernel pipeline, which is the dedicated and pipelined circuit module. Kernel pipelines duplicate themselves and group into multiple compute unit.

- Xilinx FPGAs [105]. SDAccel is the SDK tool that Xilinx launched for designers to implement the OpenCL framework on Xilinx FPGAs. OpenCL programs compatible with SDAccel are converted into the form that is acceptable to the Xilinx high-level synthesis (HLS) tool. One compute unit is generated from an OpenCL kernel program and can duplicate itself. PEs within the compute unit are revealed by unrolling the for loop in the kernel program. Same with Intel's solution, the dedicated hardware module can be pipelined.

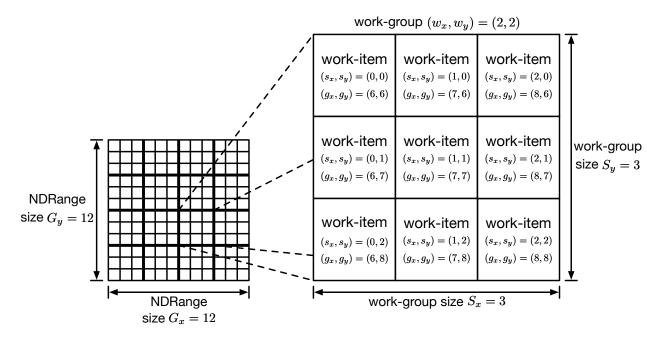

#### 2.2.2 Execution Model

An OpenCL application is combined with two programs: a set of kernel programs and a host program. A kernel program that executes on one or more OpenCL devices is defined as a unit of execution: kernel.

Kernel programs execute across a global domain of work-items, where an index space is defined. The work-items in a grid are broken up into work-groups. A work-item has a global ID according to the coordinate within the index space; while the local ID is defined based on the position within its work-group. The index space is called an NDRange in OpenCL. The NDRange is an N-dimensional index space, where N is up to three. The NDRange is defined by the size of the index space (global size) in each dimension, the size of a work-group (local size), and the offset F indicating the initial value of the indices. Each work-item's global ID is an N-dimensional tuple, as well as the local ID. Work-groups are also assigned IDs that indicating positions of the work-groups as blocks within the NDRange. Therefore, a work-item is calculated by using two ways: (1) a global index; (2) the size and index of work-group and local index.

As the example is shown in Figure 2.2, a 2-dimensional NDRange is demonstrated. The NDRange is defined by the NDRange size  $(G_x, G_y)$ , the work-group size  $(S_x, S_y)$ , and the global ID offset  $(F_x, F_y)$ . Each work-item is identified by either its global ID  $(g_x, g_y)$  or the calculation of work-group ID  $(w_x, w_y)$ , the work-group size  $(S_x, S_y)$ , and the local ID  $(s_x, s_y)$  within its work-group such that

$$(g_x, g_y) = (w_x * S_x + s_x + F_x, w_y * S_y + s_y + F_y)$$

The number of work-groups are computed as <sup>1</sup>

$$(W_x, W_y) = (ceil(\frac{G_x}{S_x}), ceil(\frac{G_y}{S_y}))$$

<sup>&</sup>lt;sup>1</sup>Beginning from OpenCL 2.0, work-group sizes could be non-uniform in multiple dimensions when the global size is not divisible by the work-group size in each dimension.

The real-world example of dot product is shown below. We want to calculate the dot product of two vectors  $\mathbf{a} = [a_0, a_1, ..., a_{15}]$ , and  $\mathbf{b} = [b_0, b_1, ..., b_{15}]$ , which is defined as  $\mathbf{a} \cdot \mathbf{b} = \sum_{i=0}^{15} a_i b_i$ . The intermediate result  $\mathbf{c} = [c_0, c_1, ..., c_{15}]$  is denoted as  $c_i = a_i b_i$ , where  $0 \le i \le 15$ . To calculate vector  $\mathbf{c}$  by using OpenCL, the 1-dimensioned global index space is defined as  $1 \times 16$ , and the local index space (the size of workgroup) is as  $1 \times 4$ . Therefore, there are totally 4 workgroups, each of which contains 4 work-items, i.e.,  $c_0...c_3, c_4...c_7, c_8...c_{11}$ , and  $c_{12}...c_{15}$ .

A host program that executes on the host uses the OpenCL API to create and manage the context through command queues. A context contains several hardware and software resources including compute devices, kernel objects, program objects, and memory objects. Each single compute device within the context is associated with a command queue. The command queue is categorized into three types: (1) kernel-enqueue commands that enqueue a kernel program on a device; (2) memory commands that manage memory mappings and transfer data between memories; (3) synchronization commands that control the command execution order explicitly. Commands within its command queue execute in either in-order execution mode or out-of-order execution mode.

In OpenCL, there are different domains of synchronization, i.e., command synchronization and work-group synchronization. Command synchronization can constrain the execution order of commands within a command queue in an out-of-order execution mode. Work-items within a single work-group can be synchronized by using the work-group synchronization.

The work-group is scheduled to execute on a compute unit. Every work-item is physically executed on a processing element within its corresponding compute unit. Through this mapping of compute device  $\leftrightarrow$  kernel, compute unit  $\leftrightarrow$  work-group, processing element  $\leftrightarrow$  work-item, the data parallelism in an application is expressed.

Figure 2.3: OpenCL Memory Model

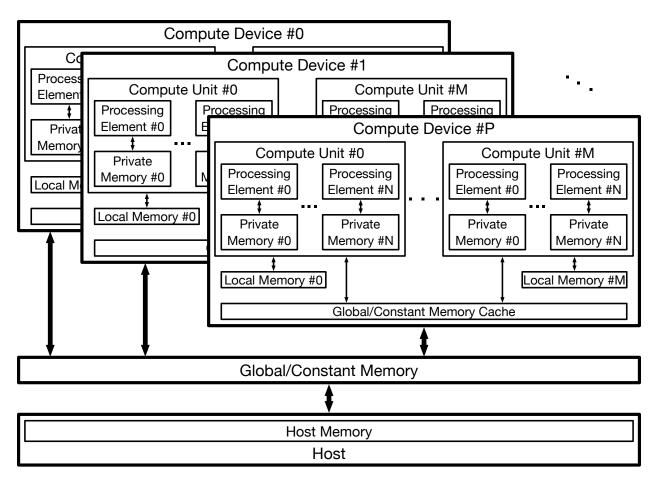

## 2.2.3 Memory Model

Memory model showing in Figure 2.3 defines how memory resources are seen by multiple compute resources, and managed by the OpenCL applications. Memories in OpenCL are divided into two parts: host memory and device memory. Host memory is only accessible by the host, and device memory is only for the compute devices<sup>2</sup>.

The device memory is further decomposed into a three-level memory hierarchy.

• **Global/Constant Memory.** The global memory is accessible by all work-items within all work-groups for reading and writing. The constant memory is also accessible by all

<sup>&</sup>lt;sup>2</sup>OpenCL 2.0 brings the new feature of shared virtual memory (SVM), by using which the host and compute devices can share the same virtual memory space without moving data explicitly.

|        |               | Global Memory | Constant Memory | Local Memory | Private Memory |

|--------|---------------|---------------|-----------------|--------------|----------------|

| Host   | Allocation    | Dynamic       | Dynamic         | Dynamic      | -              |

| 1105t  | Accessibility | Read/Write    | Read/Write      | -            | -              |

| Kernel | Allocation    | Static        | Static          | Static       | Static         |

| KUIIUI | Accessibility | Read/Write    | Read            | Read/Write   | Read/Write     |

Table 2.1: Allocation and Accessibility to Memory Objects within Memory Hierarchy

work-items but remains constant during the execution of kernels.

- Local Memory. The local memory is located in a work-group and is shared by all work-items within the work-group.

- **Private Memory.** The private memory is exclusively accessible by the work-item, and cannot be visible to other work-items.

The memory hierarchy guarantees the memory isolation among them referring to the logic concept. In host programs, the OpenCL API is used to create and manage memory objects to move data between host and device memories. A memory object is a handle pointing to a space within the memory. Table 2.1 summarizes the allocation and accessibility to memory objects for different memory hierarchies. Dynamic allocation means the memory space is managed at runtime while static allocation is at compile time.

## **Chapter 3**

## Hardware Architecture of the PolyPC Framework

#### 3.1 Brief Introduction of Zynq Architecture

The PolyPC framework is built on top of the Xilinx Zynq-7000 series (i.e., Z7045 device on the ZC706 development kit in this work). A complete Zynq device consists of the processing system (PS) and the programmable logic (PL). The PS part is a hard-copy dual-core ARM processor. The PL part is fabricated as traditional Kintex-7 FPGAs.

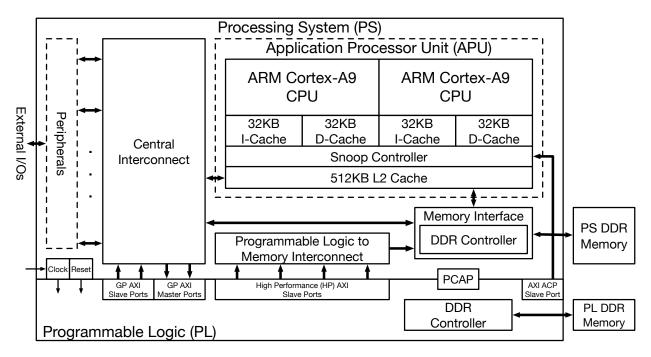

One of the most important components within the PS is the dual-core ARM processor. Figure 3.1 demonstrates the overview architecture of the Zynq SoC. The PS and the PL parts communicate with each other through various interfaces including four general-purpose (GP) AXI interfaces, four high-performance (HP) AXI interfaces, and one AXI accelerator coherence port (ACP) interface.

- GP AXI interfaces provide two slave ports and two master ports. They are designed for general purposes (e.g., passing control signals from the PS to the PL) instead of achieving high performance. The GP AXI master bus is usually used to control the hardware modules in the PL part by the PS processor.

- The four HP AXI interfaces provide four PS master ports with high bandwidth data path to the PS DDR memory. Each interface includes two FIFO buffers for read/write traffic. The PL communicate with memory interconnect to the DDR interface through the four high-speed HP AXI ports. HP AXI interfaces are used by applications that need high throughputs between the PL and the PS.

- The ACP interface provides low-latency access to PL logics, with optional coherency with

Figure 3.1: Zynq SoC Architecture

L1 and L2 cache. The master port is connected to the snoop controller that is responsible for data coherence and consistency. In other words, hardware modules that connects to the AXP slave port in the PL shares the same snoop controller with the PS processor.

The PS has a PS DDR memory that is for applications running on the ARM processor (i.e., Linux OS). The PL DDR memory is optional depending on the board design. If the PL DDR memory is connected to the PL, a DDR controller IP within the PL provides AXI interfaces that PL modules can access. The PL can be controlled via PS software through the processor configuration access port (PCAP) bridge with a bitstream file. The PS provides the clock and reset module that can drive PL logics.

## 3.2 PolyPC Architecture Overview

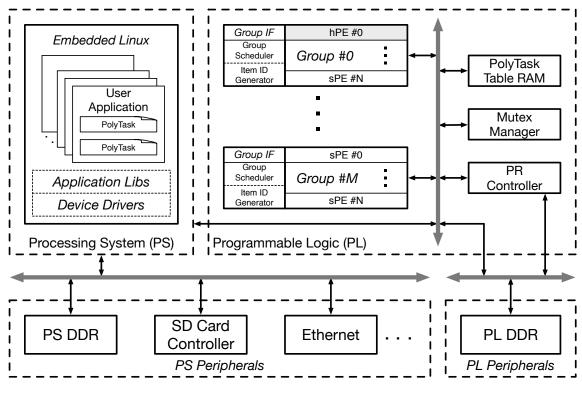

Different from existing hardware architecture, the PolyPC framework has its hardware architecture which adapts the hardware abstraction from the OpenCL platform model and extends to support unique features (i.e., polymorphic task and polymorphic multitasking). Figure 3.2

Figure 3.2: PolyPC Platform Architecture

shows the overview of the PolyPC framework architecture. In the PolyPC framework, the PS is equivalent to the host in the OpenCL platform model, and the architecture implemented on the PL is equal to the compute device. Currently, only one compute device is supported for one host in the PolyPC framework. Groups (sometimes, we call them hardware groups for clarification) are equivalent to and extends functionalities from Compute Units (CUs) within the OpenCL platform model. Each group may contain multiple processing elements (PEs) that are the same with PEs in OpenCL. The PolyPC framework supports a heterogeneous PE architecture. Each PE can be either a dedicated hardware accelerator or a general-purpose processor (i.e., MicroBlaze). The accelerator PE is called an hPE, and the processor PE is referred to as an sPE. PEs within one group can be all hPEs, sPEs, or the combination of them. hPEs can be either unchangeable or re-loadable by using the partial reconfigurable (PR) techniques. The sPEs are always re-loadable since they are general-purpose processors that can load any programs.

An embedded Linux is booted on the PS. Application libraries provide the OpenCL API

functions that are used in the host programs for the PolyPC framework. Device drivers are low-level interfaces between the Linux applications and devices within the PL part. User applications are similar to the host programs from the OpenCL execution model. In the PolyPC framework, a host program (user application) is a typical Linux user program written in the C language. In a host program, one or more polymorphic tasks (PolyTasks) are created, launched, and committed. A PolyTask is associated with a kernel program that is similar to the kernel program in the OpenCL execution model and runs on the compute device. It has polymorphic forms that can run on both sPEs and hPEs.

PS peripherals are exclusively accessible by the host processor. The Linux OS uses the PS DDR memory. Binary files and input data files are stored on the SD card for further loading into the DDR memory to process. The output results can also be moved back to the SD card after processing. The PL DDR memory is accessible by both PS and PL parts. During runtime, data elements are loaded from and stored into the PL DDR memory and processed on the PL. Other hardware modules within the PL part (i.e., PolyTask Table RAM, Mutex Manage, and PR Controller) support unique features of the PolyPC framework.

#### 3.3 Memory Hierarchy

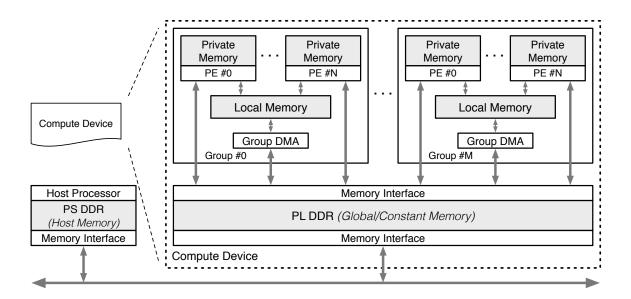

Similar to the OpenCL memory model, the PolyPC framework provides a three-level memory hierarchy within one compute device including private memory, local memory, and global/constant memory. The host memory is exclusively accessible by the host processor.

Figure 3.3 demonstrates the implementation of the three-level memory hierarchy in the PolyPC framework. The global/constant memory is visible to all PEs within their group on the compute device. Besides, global/constant memory is also accessible by the host processor and is used to temporarily store data and binary files that are utilized by the compute device. The local memory is located in a group and shared by PEs within the group. The private memory is exclusive owned per PE. Within each group, a group DMA can move datum between the local

Figure 3.3: PolyPC Memory Hierarchy

memory and the global memory so that PEs are nearer to the datum that is ready to process than those in the global memory.

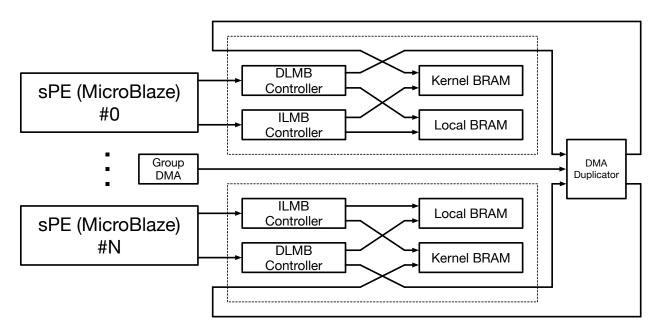

The global memory is connected to the host and the compute device through the AXI bus, as well as connections between memories and PEs. PS DDR and PL DDR memories are used to implement the host memory and the global/constant memory, respectively. Local memories use block RAMs (BRAMs), which are dedicated memory resources on FPGAs. Private memories are different per PE kind. For hPEs, the private memory is determined according to the kernel codes that define the size of the private memory. For sPE, the private memory uses the block RAM that can be only accessible by the general-purpose processor.

## 3.4 Bus Hierarchy

The PolyPC framework uses a hierarchical bus architecture based on the AXI memory-mapped (MM) bus. The AXI4 protocol provides the optional burst addressing and read and write operations works on multiple channels [106]. For example, reading data elements involves Read Address channel and Read Data channel. Under the non-burst mode, a read operation consists

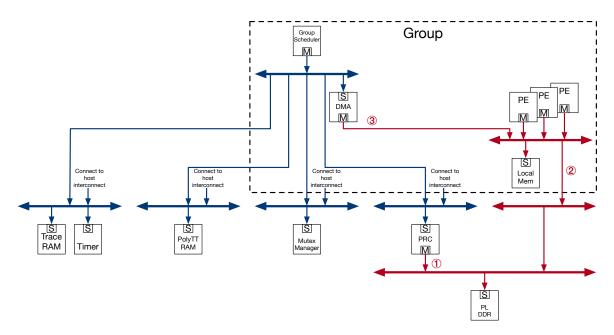

Figure 3.4: Bus Hierarchy of the Compute Device

of a read address request through the Read Address channel and a data read on the Read Data channel. If the size of data is larger than the bus length, the whole process will invoke multiple small read operations. The burst mode provides an efficient way for data transferring with consecutive addresses. Under the burst mode, a read operation consists of one read address request following by multiple data reads, which will significantly improve the bus bandwidth for a large amount of data.

The AXI MM bus is divided into two types: AXI-lite bus and AXI-full bus [9]. The former one does not have burst mode and usually is used for signal controlling. The latter one has burst mode and is designed for high throughput. In a practical design, the control flow bus architecture and data flow bus architecture are independent of each other to avoid interferences. As shown in Figure 3.4, the horizontal double-arrow lines represent AXI interconnects that have both slave and master ports. All memory-mapped IP modules have to communicate with others through AXI interconnects as either a slave device or a master device. The vertical single-arrow lines represent those connections from devices to interconnects.

The blue lines are the control path by using the AXI-lite protocol, and the red ones are data

flow by using the AXI-full protocol. Every peripheral such as PolyTT RAM and mutex manager has their own interconnect, each of which is connected to all groups and the host. Therefore, when different groups access different peripherals, the performance will not be affected since control signals go to different interconnect. The red lines are the data path by using the AXI-full protocol. Three data paths are demonstrated in Figure 3.4.

- PR Controller Data Path The master port of the PR controller is used to fetch PR bitstream files from the PL DDR. When the PR controller is programming the PR region, the PR files are read to write to the ICAP module in burst mode.

- 2. PE Data Path Every PE has the data master port connect to the inner group data interconnect that is connected to the outer group data interconnect. Multiple groups can access the PL DDR through the same outer group data interconnect. The local memory is also attached to the inner group data interconnect. PEs operate on the local memory, which will not affect other groups to access data from the PL DDR. PEs can also use burst mode to fetch and update data from the PL DDR.

- 3. **Group DMA Data Path** The master port of the group DMA shares the same inner group data interconnect with PEs. Data elements between the PL DDR and the local memory are transferred in the burst mode.

Within each group, the group scheduler and PEs work on the group control interconnect and the inner group data interconnect, respectively. This design will leverage features of AXI-full and AXI-lite protocols to avoid the interference between control signals and the data transferring.

Figure 3.5: Structure of PolyTask Table RAM

### 3.5 Compute Device Architecture

### 3.5.1 PolyTask Table Queue

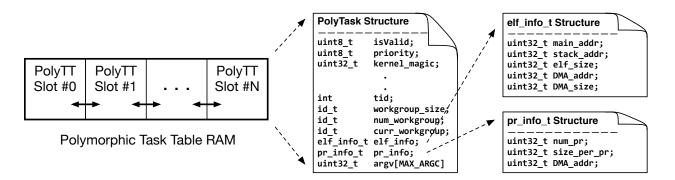

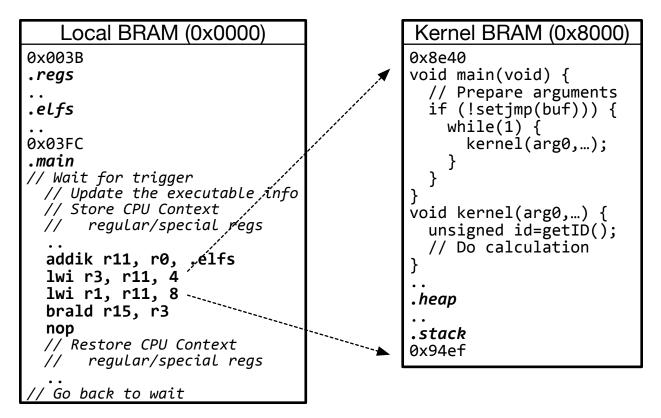

PolyTask table RAM is a doubly-linked list storing PolyTask tables in the block RAM. In host processor one user thread can create and launch one or more kernels that will run on PEs. A running kernel on compute device is called as a polymorphic task (PolyTask) in PolyPC context. Creating a PolyTask by a user thread is the equivalent process to create a PolyTask table in the PolyTask table RAM.

PolyTask table (PolyTT) records execution information to run a PolyTask and to switch between them. Figure 3.5 shows the detailed structure of the PolyTask table. The priority is set by users and is used for schedulers. The tid is copied from the thread ID from the user thread creating that particular PolyTask. The kernel\_magic is defined manually. Together with tid, kernel\_magic is a unique identifier to distinguish each PolyTask. workgroup\_size (the size of each workgroup, i.e., the number of work-items within one workgroup) and num\_workgroup (the number of workgroups totally) are kernel configurations that are the same with OpenCL. The curr\_workgroup is the workgroup IDs indicating the latest workgroup that is running. The array argv stores arguments that pass to the kernel. elf\_info and pr\_info record the information of 'source codes' of a PolyTask in two forms: ELF executables and PR bitstream files. These two files are located in the FPGA DDR, which are initially loaded by user thread. Different from

|                     | ReqID | CurID | RelID |

|---------------------|-------|-------|-------|

| Execution Instances | W     | R     | WR    |

| Mutex Manager       | R     | W     | WR    |

Table 3.1: Accessibility of Registers on the Mutex Manager for a Mutex Lock

pr\_info that only stores the entry addresses and sizes of bitstream files for each hardware thread, elf\_info stores the stack address additionally. To decrease the size of ELF files, sections that are allocated dynamically during run-time are eliminated with only labels remaining (e.g., head and stack sections). Therefore, the ELF file size and the DMA size are not the same and sections are loaded into FPGA DDR one by one according to its virtual memory address.

### 3.5.2 Mutex Manager

Mutex manager provides the underlying mutual exclusion mechanism across any execution instance across the whole system. It is a complement to the original OS mutex functions. In PolyPC, there are three kinds of execution instances: host programs on the host processor, scheduling programs on group schedulers, and PolyTasks on PEs. When acquiring the access of global resources (e.g., PolyTT Queue), threads within Linux can leverage OS-level mutex locks. Polymorphic tasks are not aware of these mutex locks at all. Instead of getting host processor involved to handle mutex requests from polymorphic tasks, a dedicated global mutex manager is set. Therefore, there are totally two-level mutex locks. For threads running on the host processor, firstly, they need to request the global mutex locks to exclude polymorphic tasks on PEs, and then request the OS-level mutex locks. Polymorphic tasks can request global mutex locks directly to exclude all the other threads.

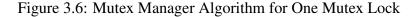

Execution instances request and release mutex locks with the mutex manager through multiple 3-register bundles that are accessible to both execution instances and the mutex manager. One mutex lock occupies three registers to complete its functionality. Table 3.1 demonstrates the accessibility of three registers (i.e., ReqID, CurID, and RelID) from one mutex lock. To avoid

conflicts, one register may be read-only to execution instances and write-only to the mutex manager such as ReqID, and CurID. Since RelID cannot be read and written at the same by the mutex manager and execution instances, it is entirely accessible for both sides. To request and release a mutex lock, every execution instance should have one unique ID to let the mutex manager identify them. In the PolyPC framework, the host program can use the process ID (PID) from the Linux system while the group scheduler can use the group index that starts from 1. The algorithm of requesting a mutex lock from an execution instance is shown as:

1. Keep polling CurID to check if it is equal to its ID.

If not, set ReqID with its ID and repeat this step (1); otherwise, jump to the next step (2).

2. Continue to run.

Possibly, there are multiple requests for one mutex lock by writing their IDs to ReqID during the same period. The mutex manager approves a random request by choosing its ID. Releasing the mutex lock is done by using only one register and is demonstrated as:

1. Keep RelID to check if it has been reset.

If not, set RelID with its ID and repeat this step (1); otherwise, jump to the next step (2).

2. Continue to run.

Since one execution instance can only obtain one mutex lock at one time, the mutex manager monitors the RelID to check if the execution instance would release this mutex lock.

Figure 3.6 summaries how the mutex works for one mutex lock. The mutex manager keeps checking CurID to examine if this mutex lock has been obtained already. If CurID is equal to zero, which means this mutex lock is free to requests no matter there are requests or not, the mutex manager fills CurID with requesting ID from ReqID and resets ReqID in case this is the only request for this mutex lock. If RelID is not equal to zero, which means the execution instance wants to release this mutex lock, the mutex manager resets RelID to tell the execution

```

while true do

if CurID == 0 then

CurID = ReqID;

ReqID = 0;

end

if RelID != 0 then

RelID = 0;

CurID = 0;

end

end

```

Figure 3.7: PolyTask Context Switching Demonstration

instance that the mutex lock has been released, and resets CurID to let the mutex manager know that current execution instance has released this mutex lock.

# 3.5.3 Partial Reconfiguration Controller

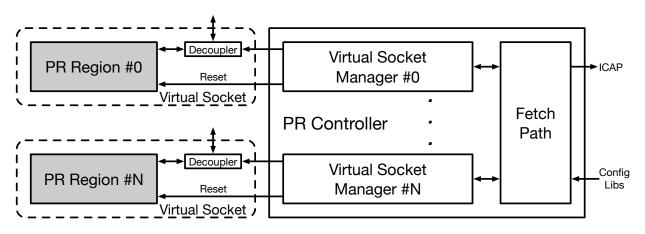

In the PolyPC framework, different hardware threads running on hPEs are switches by using the partial reconfiguration (PR) technique. Each loadable hardware thread exists as a hardware logic module and is placed within a PR region. To switch out a running hardware thread, the group scheduler requests the PR controller to load a PR bitstream file from the PL DDR into a particular PR region. For the group with multiple hPEs, the group scheduler issues multiple requests to the PR controller one at a time. The PR controller works with multiple virtual socket managers

(VSMs) simultaneously. Different group schedulers can issue requests at the same time. Since the PR controller uses the internal configuration access port (ICAP) IP module that can load only one bitstream file at a time, the PR controller queues requests from multiple VSMs and responses to them one by one.

As shown in Figure 3.7, the PR controller consists of VSMs that are connected to the fetch path. A VSM manages one particular virtual socket that refers to a PR region with static logics assisting the PR functionality. For example, the PolyPC framework uses decouplers to isolate PR regions with other static logics. In particular, during the period of loading one PR bitstream file into its corresponding PR region, the output wires of PR regions will be assigned with unexpected values that interfere with control logic on buses (e.g., valid signals on a master AXI Stream bus). This phenomenon may result in confusions of modules connecting to the PR region. For instance, if the PR region connects to a FIFO by using a master AXI Stream bus, the FIFO may be filled with garbage values during PR loading since the valid signal may be asserted for more than one clock cycle. Decouplers are comprised of multiple multiplexers of 2 inputs to isolate these control signals. The VSM uses a 1-bit select line to select correct values of decoupled signals. The POlyPC framework uses another reset signal connecting to the logic that is programmed on the PR region to reset the module in behavior level. To guarantee that the logic runs correctly after loaded into the PR region, each VSM works in the following three states:

- 1. **Initialize** The group scheduler assigns the memory address along with other information (e.g., size) of the PR bitstream file that is applicable on this virtual socket. The VSM waits for triggers or starts signals to load the PR bitstream file. At this state, the decouple and reset signals remain deasserted.

- 2. Load The VSM asserts the decouple signal to trigger the decoupler to work and notice the fetch patch to bring corresponding PR bitstream file from configuration library to the ICAP module. This state may last for a while depending on the size of the bitstream file and the bandwidth of buses connecting to the memory.

Figure 3.8: Group Architecture

3. **Reset** The VSM deasserts the decoupling signal and assert the reset signal. The duration of the reset signal is defined at the Initialize state. After certain clock cycles, the VSM deasserts the reset signal and go back to the Initialize step.

The PR controller uses the ICAP IP module to load PR bitstream files to corresponding PR regions. As discussed in section 3.1, the Zynq device has a PCAP module to load bitstream files. Before using ICAP, the PolyPC framework switches from PCAP to ICAP by clearing the PCAP\_PR bit in the DEVCFG CTRL register. In the PolyPC framework, PR bitstream files of hardware threads are stored in the PL DDR memory along with creating the PolyTthread from the host. The Config Libs refers to the DDR memory that storing bitstream files. The location of PR bitstream files for each virtual socket are set during runtime by the group scheduler.

# 3.6 Group Architecture

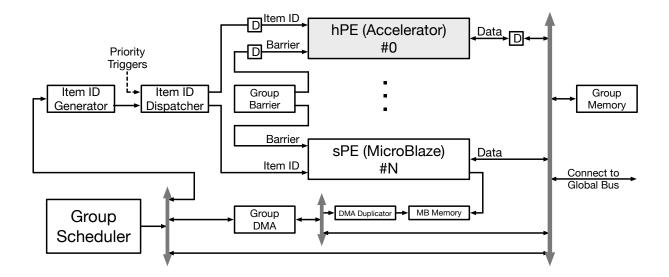

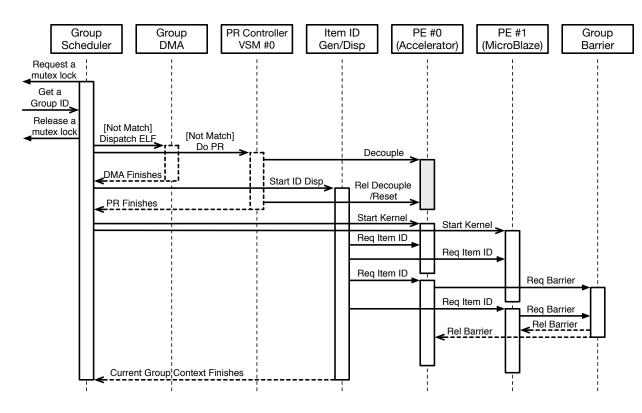

Groups are computing resources in PolyPC. One group consists of the Group Interface (Group IF) and one or more Processing Elements (PEs). Figure 3.8 shows the overview of detailed group

architecture. Within one group, PEs may consist of hardware accelerators, MicroBlazes, or both of them. Hardware modules to run polymorphic tasks are PEs in two variants: hardware accelerators and general-purpose processor (i.e., MicroBlazes). In other words, one polymorphic task has two execution instances: ELF binaries for MicroBlazes and bitstream files for hardware accelerators. In Figure 3.8, the gray PE block is shown as a PR region. The hardware accelerators can be either placed into PR regions for dynamic scheduling or configrured as non-loadable for performance purposes.

#### **3.6.1** Group Interface

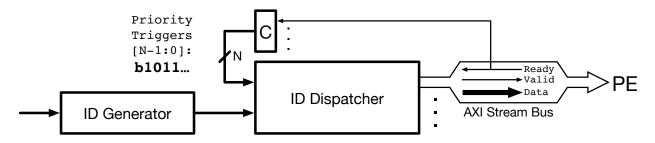

The group IF Group IF has two major components: item ID generator and dispatcher, and the group scheduler. After receiving a trigger command (i.e., the size of a new work group) from the group scheduler, the item ID generator begins to generate item IDs. The item ID is generated one by one clock cycle. The item ID dispatcher will assign one ID to one of the PEs per clock cycle. The item ID generator and dispatcher and PEs are connected by using the AXI-Stream bus. Considering the performance of each PE is different from each other and achieving the best efficiency, Ready signals of item ID AXI stream buses from all PEs are wired to the item ID dispatcher as the priority selection input. In this way, one PE can request an ID as soon as it finishes the current thread.

### **Group Scheduler**

The group scheduler decides what application and which work group will run on this hardware group. The group scheduler handles PolyTask context switching, as well. PolyPC supports run-time thread switching for both software and hardware threads. In other words, the new PolyThead applications are programmed off-line and added to the running system without terminating it. Unique PE architectures are designed to support this feature.

Figure 3.9: ID Generator and Dispatcher

### **ID** Generator and Dispatcher

One ID generator and one ID dispatcher work together to provide item IDs to PEs. Item IDs refer to the global IDs within the problem space (see Figure 3.9). Once requesting a new work group, the group scheduler initializes the ID generator with two arguments: a 2-dimensional global offset of the first position of the new work group and the 2-dimensional size of the new work group. The ID generator then generates each global ID of the new work group one every one clock cycle. The generated ID is passed to the ID dispatcher through the AXI stream bus. In the PolyPC framework, one 2-dimensional ID is composed of two 16-bit width IDs. The total 32-bit wide ID can be delivered and received in one clock on a 32-bit wide AXI stream bus for high throughput. PEs need to know the end of current work group so that one special ID is reserved for the purpose (i.e.,  $0 \times FFFFFFFF$ ). Therefore, the maximum global problem space is  $2^{16} - 1$  by  $2^{16} - 1$ . The reasons why the ID generator generates the global ID instead of the local ID is because we want to save the computation time for PEs to calculate global IDs. In the current design, for one work group, the group scheduler will help PEs to calculate the global ID of the first position of this work group for only one time. If the ID generator generates the local ID, the maximum problem space will expand to  $2^{32}(2^{16}-1)$  by  $2^{32}(2^{16}-1)$  from the ID generator side since the group size is 32-bit width. But in this case, every PE will calculate the global ID for every received item ID if necessary, which may waste computation resources.

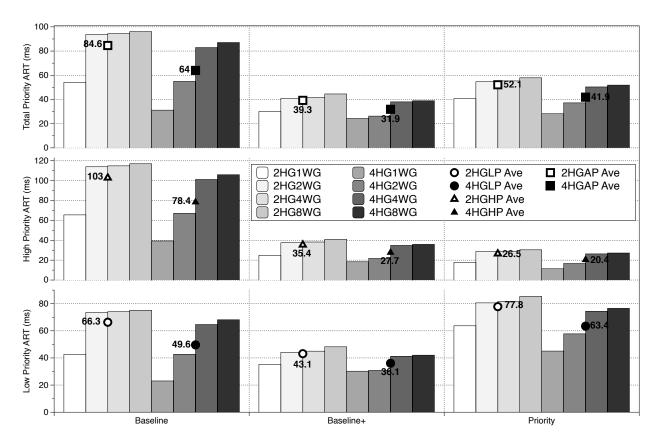

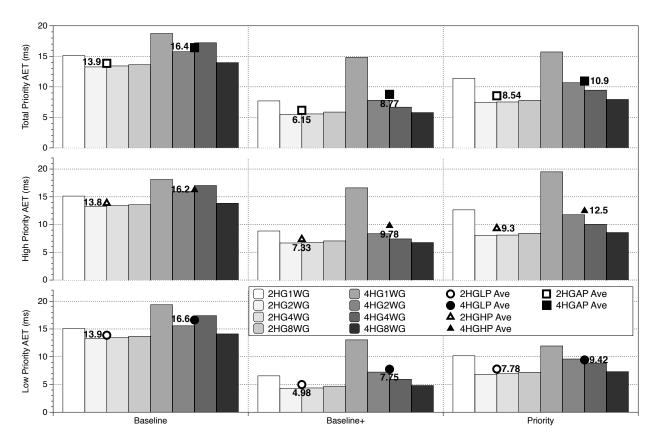

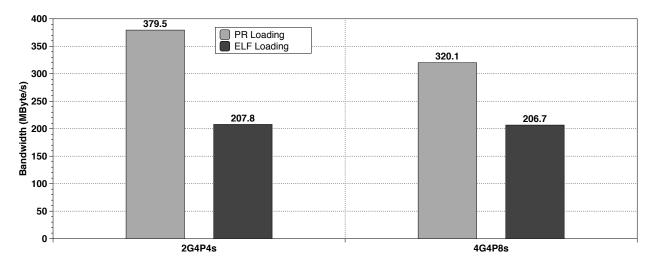

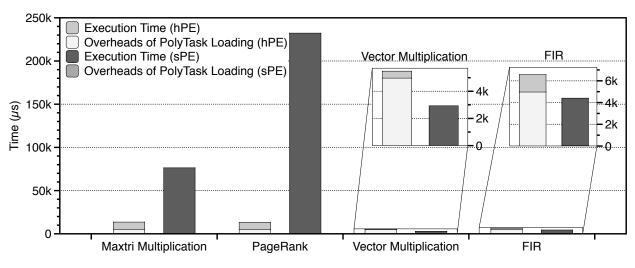

The ID dispatcher dispatches every ID received from the ID generator to all PEs according to the runtime priority. Every PE uses the AXI stream bus to receive the ID and their Ready