University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

12-2014

# Designing and Implementing a Micro-controller based Primaryside Sensing Flyback Converter for LEDs Driver

Nam Nhat Tran University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons

# Citation

Tran, N. N. (2014). Designing and Implementing a Micro-controller based Primary-side Sensing Flyback Converter for LEDs Driver. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/2131

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

Designing and Implementing a Micro-controller based Primary-side Sensing Flyback Converter for LEDs Driver

# Designing and Implementing a Micro-controller based Primary-side Sensing Flyback Converter for LEDs Driver

A Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

# Nam N. Tran Hanoi University of Technology Bachelor of Science in Electrical Engineering, 2007

# December 2014 University of Arkansas

This thesis is approved for the recommendation to the Graduate Council.

Dr. Simon S. Ang Thesis Director

Dr. Juan C. Balda Committee Member Dr. Roy A. McCann Committee Member

#### ABSTRACT

The fast development of LED and its applications has enabled a new generation of lighting device with higher efficiency and long lifespan. By employing a primary-side sensing flyback converter and the PIC18F micro-controller series, an LED driver could achieve two important features: (1) the compatibility with the available lighting fixtures, and (2) reducing unit price. The flyback converter was chosen for its simplicity, competitive low cost, and its ability to provide a constant output current, a necessarily important factor to an LED driver. Meanwhile, the PIC18F micro-controller series offer numerous advanced features which include but not limited to pulse-width modulation (PWM), 10-bit 13-channel Analog-to-Digital Converter (ADC) etc., which suitably meet the requirements for regulating a primary-side sensing flyback converter. The design process was first conducted in simulation stage with aid from Matlab®-Simulink and Cadence OrCAD Capture CIS (PSpice). By using PI based control scheme and making full use of built-in Analog Behavioral Modelling (ABM) blocks, the simulation-relevant difficulties due to lacking of appropriate model for the PIC18F series micro-controller were completely solved. The simulation results matched well with the intended design specifications: the output voltage is 32 VDC while the load current is 350 mA. More importantly, the simulation results demonstrated the feasibility of deploying a primary-side sensing flyback converter in conjunction with a PIC18F micro-controller as an LED driver. Next, a demo printed-circuit board (PCB) was layout by using OrCAD PCB Editor. Finally, the PIC18F4550 micro-controller was programmed to undertake control tasks of the LED driver. The experimental results reflect the project's success with all the parts of the driver harmoniously work as expected.

#### ACKNOWLEDGEMENTS

The 2-year journey at the University of Arkansas has brought to me a lot of unforgettable memoirs. Having opportunity to study in a world class education environment and living in a peaceful place likes Fayetteville are two wonderful experience that lead me on the way to fulfill the dream of my life.

Throughout of my life, my family has been always providing me with the greatest support and the last two years is the time helped me to understand how great it is. I could hardly do anything other than to express my sincere thanks to my father, Liem Tran, and my mother, Hoa Trinh for their inspiration they gave, their determination they taught and their forgiveness they granted. To my brother, Quang Tran, I am thankful to your patience in teaching me everything, includes English that I am writing at this moment. To my wife, Mai Nguyen, and my daughter, Van Tran, I would like to thank for your greatness sacrifice. It is my own family that continuously motivates me to do everything with the highest commitment. Living and studying together at the University of Arkansas and then welcoming the present of our lovely daughter are privileges of our life.

I want to express my gratitude to my advisor, Dr. Simon S. Ang for his willingly and continuously help in study work as well as my personal life. He taught me everything with a great passion, provided me with the best working conditions for the project. The greatest thing I learned from Dr. Ang is his dedication to work that inspired me to overcome all difficulties.

My study at the University of Arkansas would not be successful without invaluable lessons from Dr. Juan C. Balda and Dr. Roy A. McCann, who are also the members of my thesis committee. I

want to show my appreciation to Dr. Balda and Dr. McCann for everything they did for me, which is too much that I can list here.

I want to extend my sincere appreciation to Dr. Chien Nguyen. He is not only the person who leaded me on the way to the University of Arkansas but also the meticulously mentor who helped me from a very first step of my project.

My opportunity to study at the University of Arkansas would be impossible without the financial supporting from the Vietnam Ministry of Education and Training. Thoroughly understood how fortunate I was as a sponsored student, I want to express my appreciation to my sponsor agency. Last but not least, I want to send my appreciation to my lab mates, Dr. Jaber Hasan and Yilong

Ma for their enthusiastic helps and insightful comments.

# **TABLE OF CONTENTS**

| Chapter 1 - Introduction                                                             | 1  |

|--------------------------------------------------------------------------------------|----|

| 1.1 Overview                                                                         | 1  |

| 1.2 Purpose and organization of this thesis                                          | 4  |

| Chapter 2 - Design specifications and considerations                                 | 5  |

| 2.1 Design specifications                                                            | 5  |

| 2.2 Micro-controller as a driver's controller                                        | 7  |

| 2.3 The Flyback Converter                                                            | 9  |

| 2.4 Simulation                                                                       | 13 |

| 2.5 Demo board design                                                                | 13 |

| 2.6 Programming                                                                      | 14 |

| Chapter 3 – Simulation of a micro-controller based primary-side sensing flyback      |    |

| converter for LED driver                                                             | 16 |

| 3.1 Introduction                                                                     | 16 |

| 3.2 PID based control scheme                                                         | 17 |

| 3.3 Modeling the flyback converter                                                   | 18 |

| 3.4 Controller and feedback system design                                            | 21 |

| 3.5 Simulation with Cadence's PSpice                                                 | 30 |

| 3.6 Simulation results                                                               | 39 |

| 3.7 Conclusion                                                                       | 43 |

| Chapter 4 – Hardware implementation                                                  | 44 |

| 4.1 Overview                                                                         | 44 |

| 4.2 Component preparation                                                            | 47 |

| 4.3 The PIC18F4550 micro-controller                                                  | 47 |

| 4.4 Power supply solution for the micro-controller and other ICs                     | 52 |

| 4.5 Capture symbol and footprint preparation for the gate driver and the transformer | 54 |

| 4.6 PCB design                                                                       | 56 |

| 4.7 Artwork generating                                                               | 62 |

| 4.8 The PIC18F4550 programming                                                       | 64 |

| Chapter 5 – Experimental results                                                     | 70 |

| 5.1 Overview                                               | 70 |

|------------------------------------------------------------|----|

| 5.2 The characteristics of the PIC18F4550 micro-controller | 70 |

| 5.3 Open-loop performance                                  | 74 |

| 5.4 Closed-loop performance                                | 75 |

| Chapter 6 – Conclusions                                    | 78 |

| 6.1 Conclusions                                            | 78 |

| 6.2 Future works                                           | 79 |

| References                                                 | 80 |

# LIST OF TABLES

| Table 2.1 – Design specifications                                                    | 6  |

|--------------------------------------------------------------------------------------|----|

| Table 2.2 – Main characteristics of the micro-controller PIC18F4550                  | 9  |

| <b>Table 4.1</b> – Packaging information for PIC18F4550 micro-controller's footprint | 49 |

| Table 4.2 – Parameters of the selected resistors.                                    | 53 |

| Table 4.3 – Bill of Material (BOM) for the current project                           | 59 |

| Table 5.1 - ADC testing's results.                                                   | 74 |

# LIST OF FIGURES

| Figure 1.1 – The total cost for using Incandescent, CFL, and LED bulbs for 20 years            | 3  |

|------------------------------------------------------------------------------------------------|----|

| <b>Figure 2.1</b> – Schematic of the LED driver with micro-controller and primary-side sensing |    |

| flyback converter                                                                              | 7  |

| Figure 2.2 – PIC18F4550 micro-controller and PicKit3 Programmer                                | 9  |

| Figure 2.3 – A flyback converter                                                               | 10 |

| Figure 3.1 - User interface of SISO Tool                                                       | 23 |

| Figure 3.2 - Real-time update designed graphs                                                  | 24 |

| Figure 3.3 - Adding two zeros at -1250 and -22700 to the compensator                           | 25 |

| Figure 3.4 - The system's Root Locus graph was updated with two added zeros and one            |    |

| pole (at <i>s</i> = 0)                                                                         | 26 |

| Figure 3.5 - Bode plot of the closed loop system with demonstration of stability               | 26 |

| Figure 3.6 - Contour of the system loop gain demonstrated on Nyquist plot                      | 27 |

| Figure 3.7 - A closer view at the (-1, 0) point                                                | 28 |

| Figure 3.8 - Step response of the controlled system                                            | 28 |

| Figure 3.9 - The PID controller in Simulink                                                    | 29 |

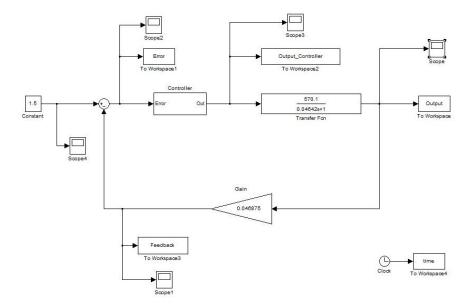

| Figure 3.10 - Simulation of the closed loop system in Simulink                                 | 29 |

| Figure 3.11 - Simulation result from Simulink                                                  | 30 |

| Figure 3.12 - Schematic for full converter simulation in Cadence's PSpice                      | 31 |

| Figure 3.13 - The Snubber Dissipative Circuit                                                  | 32 |

| Figure 3.14 - The Peak Current Detector, a mechanism of Primary Side Sensing for               |    |

| detecting the peak current of secondary side circuit without any contact                       | 34 |

| Figure 3.15 - Demonstrating the PWM mechanism in the micro-controller based LED                |    |

| driver simulation                                                                              | 35 |

| Figure 3.16 - Flowchart of PIC18F based LED driver's algorithm                                 | 36 |

| Figure 3.17 - Visualizing the Zero Current Detector by employing ABM blocks                    | 38 |

| Figure 3.18 – PID controller in PSpice                                                         | 39 |

| Figure 3.19 – Flowchart of control PWM mechanism in PSpice simulation                          | 39 |

| <b>Figure 3.20</b> – Input and output signal of the zero current detector                      | 40 |

| <b>Figure 3.21</b> – Illustrating of PWM mechanism: comparing signal from PID to MOSFET        | 41 |

| M2's source signal and generating of PWM signal                                     |    |

|-------------------------------------------------------------------------------------|----|

| Figure 3.22 – Voltage at the gate of MOSFET M2 under PWM operation (solid), the     |    |

| output voltage (black), and the output current (red)                                | 41 |

| Figure 3.23 – Input Voltage and Input Current (Solid)                               | 42 |

| Figure 4.1 – PCB design process with OrCAD CIS Capture and OrCAD PCB Editor Lite    |    |

| Version                                                                             | 45 |

| Figure 4.2 – Flowchart of Component Preparation                                     | 46 |

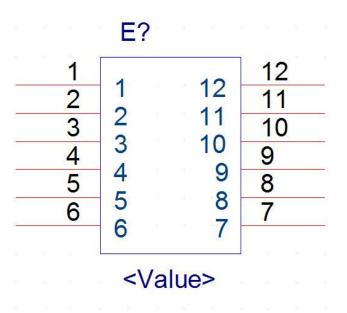

| Figure 4.3 – Designed Capture symbol for a 40-pin DIP-type PIC18F4550 micro-        |    |

| controller                                                                          | 48 |

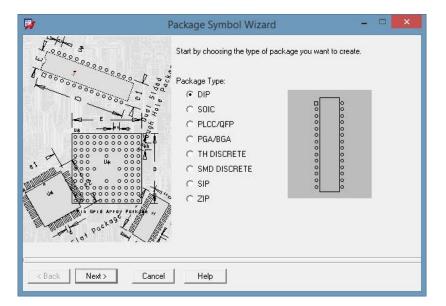

| Figure 4.4 – Selecting the type of package                                          | 49 |

| Figure 4.5 – Selecting the dimension unit                                           | 50 |

| Figure 4.6 – DIP Parameters window                                                  | 50 |

| Figure 4.7 – Choosing a padstack for symbol pins                                    | 51 |

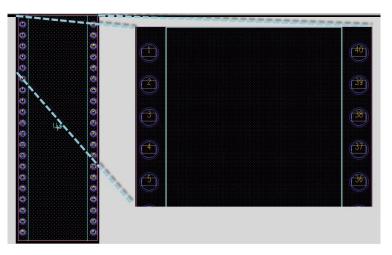

| Figure 4.8 – Designed footprint for the 40-pin DIP-type PIC18F4550 micro-controller |    |

| (PIC18F4550PDIP.dra)                                                                | 51 |

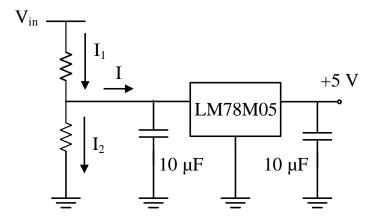

| Figure 4.9 – Circuit Schematic for calculating of voltage divider's power resistors | 52 |

| Figure 4.10 – Capture symbol for the EFD20 transformer                              | 54 |

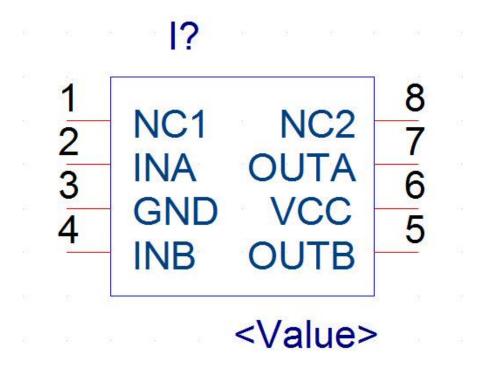

| Figure 4.11 – Capture symbol for the IXDN604SIA gate driver                         | 55 |

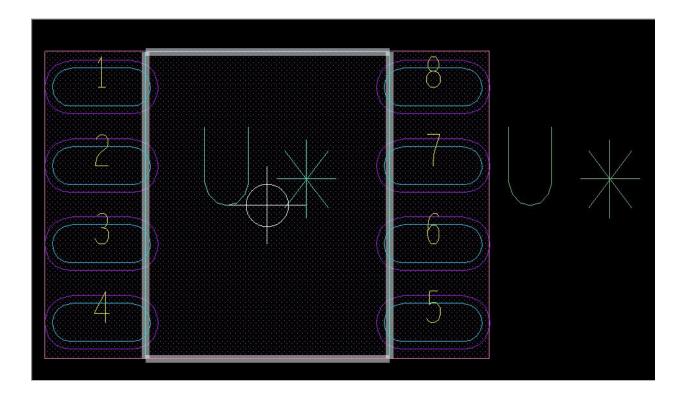

| Figure 4.12 – The Gate driver IXDN604SIA's designed footprint (IXDN604SIA.dra)      | 55 |

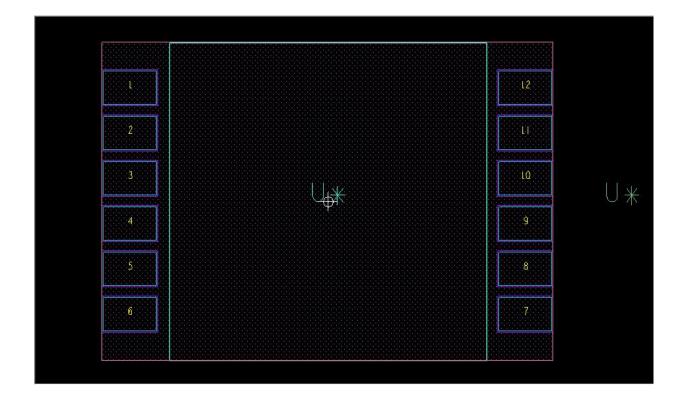

| Figure 4.13 – The EFD20 transformer's designed footprint (EFD20.dra)                | 56 |

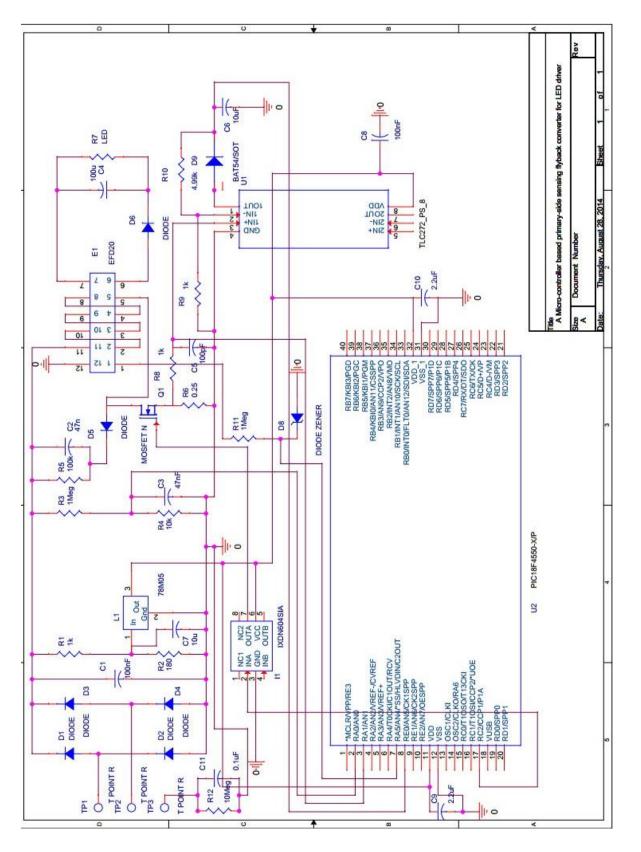

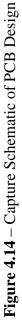

| Figure 4.14 – Capture Schematic of PCB design                                       | 58 |

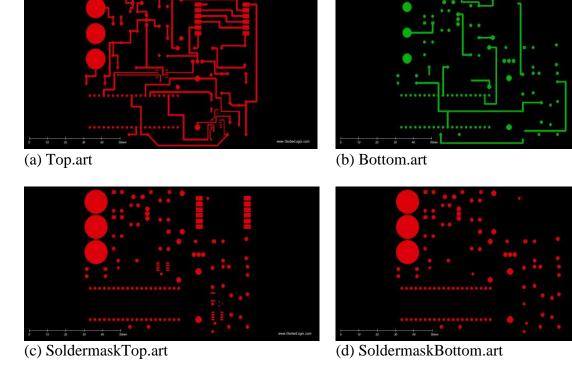

| Figure 4.15 – Defining layer stack-up for the PCB                                   | 60 |

| Figure 4.16 – Arrangement of Components and Routing on the PCB                      | 61 |

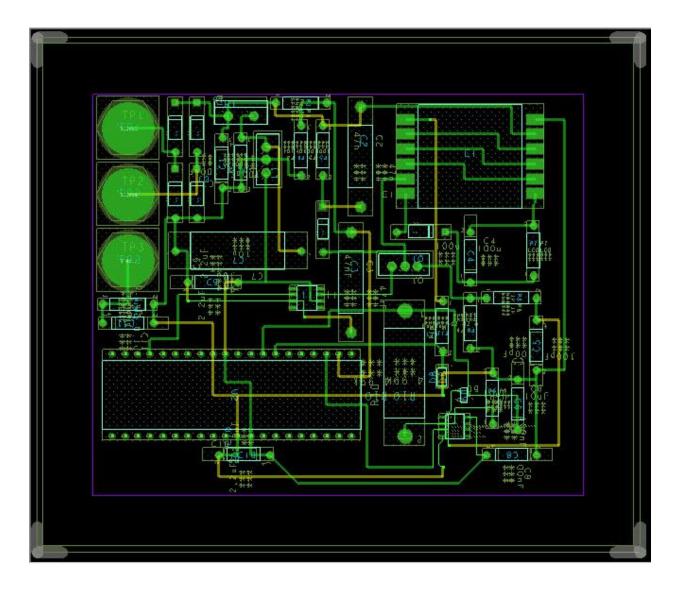

| Figure 4.17 – Generated Artwork files as seen from GerberLogix Viewer               | 63 |

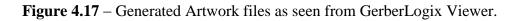

| Figure 4.18 – Designed PCB after fabricating by Sunstone PCB Vendor                 | 64 |

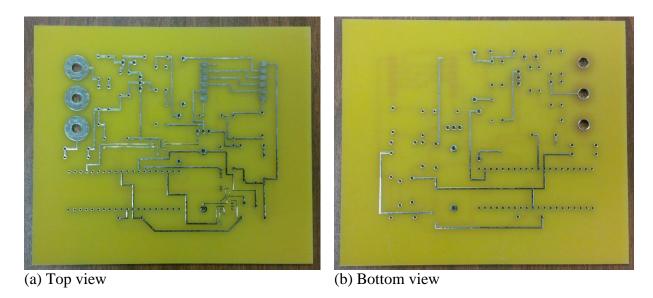

| Figure 4.19 – The complete PCB with soldered components as seen from top view       | 64 |

| Figure 4.20 – Connecting the PIC18F4550 with PicKit3 programmer via a breadboard    | 65 |

| Figure 4.21 - The waveform of 100-kHz PWM with 40% duty cycle                       | 68 |

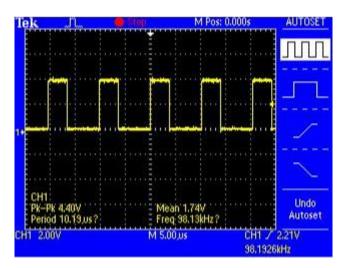

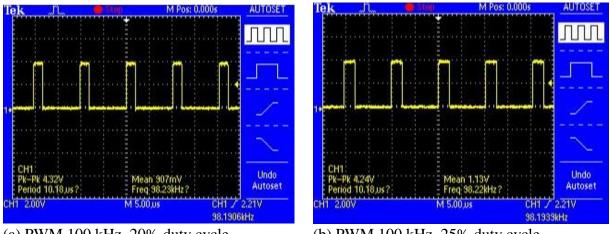

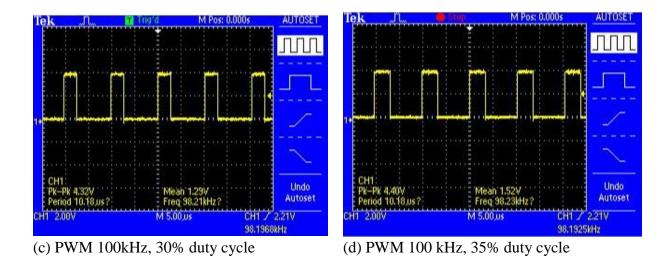

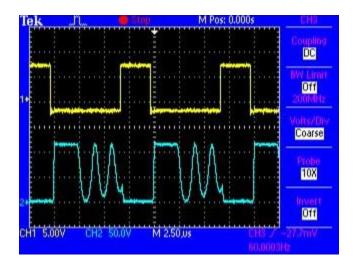

| Figure 5.1 - Various PWM signal with different duty cycles: 20%, 25%, 30%, and 35%  | 71 |

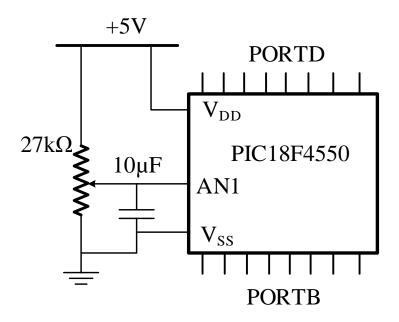

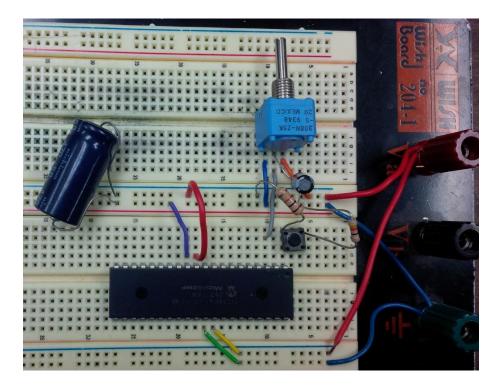

| Figure 5.2 - Circuit schematic for ADC testing                                      | 72 |

| Figure 5.3 - Implementing a testing circuit for PIC18F4550's ADC function           | 73 |

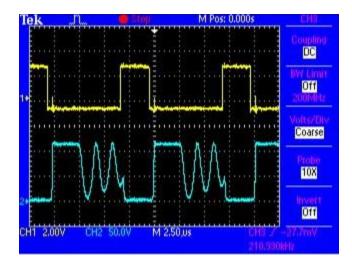

| Figure 5.4 – The waveforms of the switching transistor's gate voltage (yellow) and drain |    |

|------------------------------------------------------------------------------------------|----|

| voltage (blue)                                                                           | 75 |

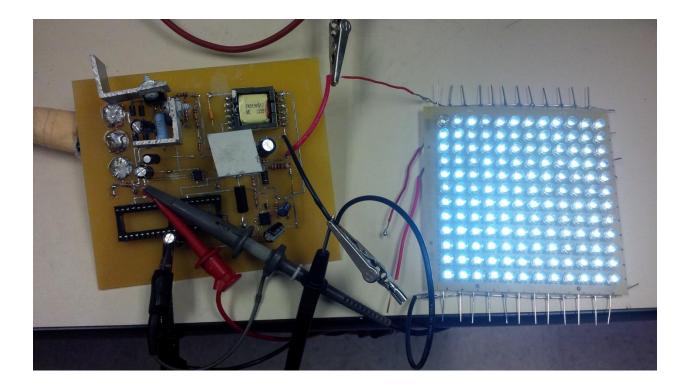

| Figure 5.5 – A matrix of LEDs is lighted up by the designed driver working in open-loop  |    |

| mode                                                                                     | 76 |

| Figure 5.6 – Waveforms of switching transistor's gate (yellow) and drain (blue) in       |    |

| closed-loop mode                                                                         | 77 |

# **Chapter 1**

# Introduction

# **1.1 Overview**

When it comes to electrical energy consumption, there is a truth that may make a lot of people to be amazed. According to the International Energy Agency, lighting accounts for 20 percent of energy consuming all over the world [1]. In fact, the omnipresence of incandescent bulb is the reason for such a high energy consuming percentile. The obsolete incandescent bulb normally converts only 5% of input energy to light and dissipates the rest to the outside environment in the form of heat. This means that one of the most popular electric device in the world is also the most inefficient electric device. Despite the introduction of some new lighting devices, likes the compact fluorescent lamp (CFL), the relatively low price and the shopping habit of most consumers make the incandescent bulb to be an indispensable one in lighting market. Consumers just do not want to buy a new lighting product and then have to replace the whole lighting fixture too. From the customer's perspective, they want to buy a new product with a low price but it must also easy to use. This is a very important thing that all designers must consider during the design process.

A solution for replacement of inefficient lighting device is using new generation light-emitting diode (LED) bulb. The development of semiconductor technology improves the lighting ability of LED significantly year over year. An LED is basically a semiconductor diode except the ability for light emitting when it is forward biased. An LED bulb is going to provide more lighting while consumes less energy. More importantly, its price will drop continuously in the near future. The latter is one of two main factors that prevent LED bulb to be welcomed on the lighting device market since the price range of an LED bulb is still relatively high compared to two of its opponent: the CFL and the incandescent bulb. Spending the same amount of money for an LED bulb, consumer could buy three CFLs, or even twenty incandescent bulbs with the same wattage. However, this correlation is being changed continuously.

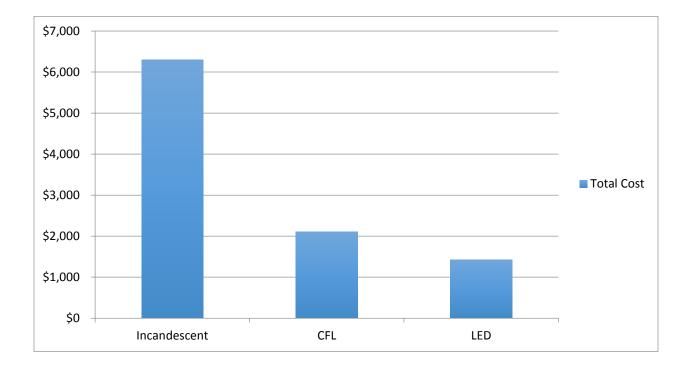

Despite having an unattractive price, LED bulb is invincible when it comes to efficacy, which means that LED bulb can achieve an impressively high light output per watt. Along this outstanding feature, the durability of an LED bulb is another great advantage that is normally ignored by consumers. Many manufacturers claim that the average lifespan of an LED bulb is more than 20 years, which will possibly be the last survivor among all the appliances you buy on the same day. In addition, the long-term benefit of an LED bulb will demonstrate its uniquely high efficacy mentioned above when the total running cost is considered [2]. A research that was done by Men's Journal magazine shows that the total cost for running a lighting system of an American family with 40 bulbs of incandescent type in 20 years (three hours of daily use with national average electricity price) is more than 4 times (\$6,300) the cost for the same system but using LED bulbs (\$1,431). Even with the CFL bulb, which is advertised as a very economical one, the total cost for that lighting system is one-and-half higher (\$2,106) than the LED system. The complete comparison is shown in Fig. 1.1. It should be noted that the total cost did not

include the expense for replacing new bulb. Since the lifespan of an LED is over 20 years, no LED bulb is expected to be replaced the whole interval. Meanwhile, each incandescent bulb could hardly work more than a year. Thus, consumers with incandescent lighting system may have to replace at least  $19 \times 40 = 760$  times during 20 years (in case no more than one bulb stops working at the same time). The situation is somehow improved with CFL bulb with each of this type can last for up to 6 years but this replacement cost will undermine its ability to attract customer.

Figure 1.1 – The total cost for using Incandescent, CFL, and LED bulbs for 20 years.

As mentioned above, the prohibitively expensive price, which will soon to be reduced, is one of two main barriers that prevent LED bulb from becoming a popular lighting product. The other factor is the compatibility of the new generation LED bulbs. In spite of having the long term benefits likes long lifespan, cost saving, and environmentally friendly product, LED bulbs would not able to persuade customers if it required them to purchase additional accessories. From design perspective, it is better to have LED bulb that works perfectly with current available fixtures. Buying a new lighting product with a little bit higher price, customers should be satisfied with their decision for many long term benefits and how easily it mounted on the available fixture at home.

#### 1.2 Purpose and organization of this thesis

The main purpose of this thesis is to design a micro-controller based flyback converter for driving the LED lighting load. The design process starts with simulation task in Matlab/Simulink and Cadence' PSpice (OrCAD Capture CIS). After successfully obtaining design-matched results, a demo board will be designed in OrCAD PCB Editor. The artworks is then transferred to a PCB manufacturer to fabricate. Finally, the micro-controller will be programmed for driver's control purpose. A brief introduction about design specifications and considerations will be presented in Chapter 2 (Design specifications and considerations). Details about simulation works and hardware implementations will be discussed in Chapter 3 (Simulation of a micro-controller based primary-side sensing flyback converter for LED driver), and Chapter 4 (Hardware implementation), respectively. Chapter 5 is about experimental results and Chapter 6 will concludes the thesis.

# Chapter 2

**Design specifications and considerations**

# 2.1 Design specifications

In order to design a driver for an LED that provides all advantages as in the previous chapter, design engineers should meticulously consider all the dimensions. Its form should be small enough to fit within the available commercial fixture, and that small driver should meet all the required technical specifications (power factor (PF), brightness, etc.). Building an LED driver based on a DC-DC switching converter with control task is undertaken by micro-controllers has recently attracted designers for various reasons. The modern micro-controllers are not only extremely powerful but also small enough to be integrated in an LED driver. They offer great a

flexibility with numerous built-in functions like pulse-width modulation (PWM), Analog-to-Digital converter (ADC), timer etc., which allow designers to do many tasks without equipping dedicated circuits. More importantly, benefiting from the development of semiconductor industry, micro-controller is becoming cheaper, greatly contributes on the effort of lowering an LED driver's price.

The work of selecting the DC-DC switching converter candidate for an LED should take into account some features like topology, performance, and implemented cost. Flyback converter emerges as an optimized choice for its simplicity, excellent input voltage-input current relationship, and low cost. The simplicity of the whole driver circuit will be greatly enhanced by regulating the output from the primary side of transformer. Using primary side sensing and regulating not only helps to save the board size by getting rid of unnecessary component like optocoupler but also eliminates its unwanted instability effects. Therefore, the LED driver's price would be further decreased while the performance is also improved.

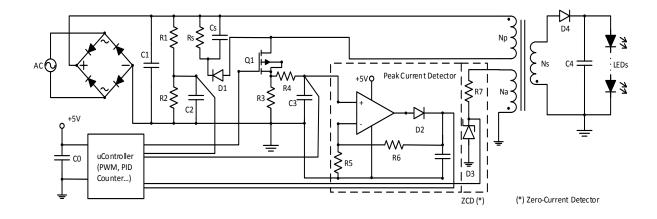

The design specifications of a micro-controller based primary-side sensing flyback converter for LED driver is tabulated in Table 2.1. The schematic for this driver is illustrated in Fig. 2.1.

| <b>F</b>                          |                          |

|-----------------------------------|--------------------------|

| Input voltage (RMS)               | 120 VAC, 60Hz            |

| Output voltage                    | 32 VDC                   |

| Output current                    | 350 mA                   |

| Switching Frequency               | $100 \pm 10 \text{ kHz}$ |

| DC-DC converter type              | Flyback                  |

| Primary-Side Sensing & Regulating | Yes                      |

| Magnetizing inductance            | 40 µH                    |

| Secondary winding inductance      | 8 μΗ                     |

| Transformer's turn ratio          | 2.23/1                   |

| Micro-controller                  | PIC18F4550               |

Table 2.1 – Design specifications

**Figure 2.1** – Schematic of the LED driver with micro-controller and primary-side sensing flyback converter.

The design process of an LED driver will start with simulation, using Matlab-Simulink and Cadence's PSpice (OrCAD Capture CIS). Next, the prototyped printed circuit board (PCB) will be designed using OrCAD PCB Editor Lite, which includes in the same free package from Cadence. The artwork files then will be transferred to a PCB manufacturer to fabricate. For demonstration purpose, the components of PCB are selected based on technical specifications only. Therefore, many of components are through-hole devices, which have larger footprint. The board size should be shrunken considerably by using surface-mount devices (SMD) if the prototyped board worked flawlessly and was ready to be commercialized.

# 2.2 Micro-controller as a driver's controller

Dedicated mixed-signal switching controllers used to be a regular choice for flyback converter regulating work. However, it is not as flexible as most of the modern micro-controller and is gradually being replaced by numerous modern, powerful, and multi-function micro-controller families [3]. Having a lot of built-in functions, micro-controllers allow designers to add more features to the same current board by simply changing control algorithms. No circuit is required

to be added, therefore the current board would not become more complicated. It means that designers will be able to provide their customers with more utilities on the same product with not too much cost for upgrading.

Selecting an appropriate micro-controller is not an easy task. Each manufacturer likes Atmel or Microchip Technology has various families of chip that can meet every control purposes. Even in each family, there are hundreds of type which different from each other by package, amount of memory, speed etc. In general, the task of selecting a micro-controller for a specific project should be based on the following criteria [4]: (1) The ability of micro-controller to provide enough strength with a reasonable price to meet all the design requirements, (2) How easy is it to program, load, and test with the micro-controller?, and (3) The supply source of microcontroller.

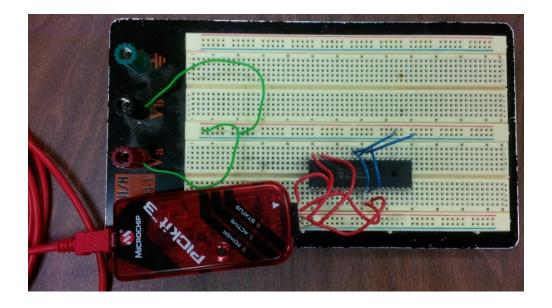

The selected micro-controller for this current project is Microchip Technology's PIC18F4550 (Fig. 2.2). First of all, this 8-bit controller is equipped with 2 Capture/Compare/PWM (CCP) modules, which is suitable for controlling a flyback converter. With 4 timer modules (3 16-bit type and 1 8-bit type), 35 I/Os with 10-bit 13-channel Analog-to-Digital Converter, signal acquisition task becomes a less burdensome work [5]. The PIC18F4550's 32Kbytes of Program Memory and 2048 bytes of Data Memory are abundant for this small LED driver circuit. In addition, the price for one unit is relatively cheap, just less than \$5 for 10 units [6] and it will be decreased dramatically if the order quantity exceeds 100 units. Its programmer, PicKit 3 provides us with a friendly software kit, includes C compiler for free. This product also has a stable supplying source from its manufacturer Microchip Technology or from other electronic component distributors like Digikey or Mouser. In conclusion, the PIC18F4550 micro-controller suitably meets all the requirements for this LED driver project.

| Package                            | DIP                      |

|------------------------------------|--------------------------|

| Number of pin/Number of IO         | 40/35                    |

| Internal Oscillator                | Up to 8 MHz              |

| Timer Module                       | 4 (Timer0 – Timer3)      |

| CCP Module                         | 2 (1 CCP/1 ECCP)         |

| ADC Module                         | 10-bit, up to 13 channel |

| Operating Voltage Range            | 2.2 – 5 V                |

| Program Memory                     | 24 Kbytes Flash          |

| Data Memory                        | 2048 bytes SRAM          |

| Programmer                         | PicKit3                  |

| Integrated Development Environment | MPLAB X                  |

| Programming Language/Compiler      | C/MPLAB XC 8 Compiler    |

Table 2.2 – Main characteristics of the micro-controller PIC18F4550

Figure 2.2 – PIC18F4550 micro-controller and PicKit3 Programmer.

# 2.3 The Flyback Converter

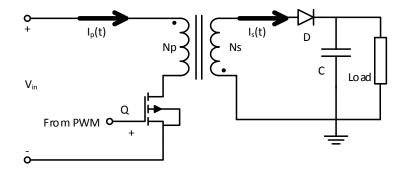

Flyback converter was selected among many DC-DC switching converter topologies for a lot of its advantages compared to the other. The absence of output inductor greatly contributes to the competitive low cost for flyback converter since the board size could be shrunken while the

budget does not have to include the inductor's price (Fig. 2.3). It is replaced by a transformer, which will be able to provide an isolation between the load and the source side [7]. With no direct connection between the two sides, safety is no longer a concern for a flyback-based circuit. This transformer also stores and releases magnetic energy, each operation respectively corresponds to the non-conducting and conducting interval of the secondary side's diode.

Figure 2.3 – A Flyback converter.

One characteristic that makes flyback topology to become the apparent choice for the LED driver is its ability to provide a constant output current or voltage, depends upon discontinuous current mode (DCM) or continuous current mode (CCM) operations. In the case of LED bulb, its brightness heavily depends on the forward current flowing through [8]. Thus, an LED driver should be designed with a constant current output in order to obtain the required performance. For those reasons, a flyback converter which works in DCM operation mode is the exact answer for this project. In addition, the flyback topology has an excellent linear relationship between the average input current  $i_{in,avg}(t)$  and voltage  $v_{in}(t)$  as

$$i_{in,avg}\left(t\right) = \frac{D^2 T}{2L_p} v_{in}\left(t\right)$$

(2.1)

which results in a very high power factor. In the above formula, D is the duty cycle, T is the switching period, and  $L_p$  is the magnetizing inductance of the primary winding. This superb

relationship makes flyback converter to be one of the most favorite choices when it comes to power factor correction. The lowest allowable power factor is an important requirement for new household appliances and must comply with specific regulations, depend on whether it uses for residential or commercial purpose.

Apart from conventional flyback converter, one distinctive feature of the converter in this project is the primary side regulation. Primary side sensing and regulating is the preferred method for this isolated converter since it makes the circuit to be less complicated and also makes full use of the PCB space more efficiently. This helps to save some cost and contribute to the effort of reducing price for the whole circuit. In this project, there is no need for the traditional isolated feedback circuit since the secondary side's operation can be monitored by using an auxiliary winding of transformer in companion with micro-controller's counter. The elimination of the optocoupler in the feedback circuit not only lessens the complex of circuit but also completely eradicates unwanted effects from the optocoupler due to temperature change.

Input voltage for the flyback converter in this project is a DC voltage with  $V_{in,max} = 120\sqrt{2} \approx 169$  V, which is rectified directly from the AC source. When the switching transistor Q is ON, the primary side current is increased linearly until it reaches the maximum value of:

$$I_{p\max} = \frac{V_{in,\max}}{L_p} t_{on} = \frac{169}{40 \times 10^{-6}} \times 0.83 \times 10^{-6} = 3.5 \text{ A}$$

(2.2)

with  $t_{on}$  is the conducting interval of the switching transistor. This on-time can be chosen from 0.5 µs to 5 µs. The on-time value selected here is 0.83 µs, which is equivalent to 0.005% of one full cycle of 60-Hz AC source (approximately 16.6 ms). During  $t_{on}$ , the secondary side's diode

will be reverse biased due to inversed polarity and the load current is supplied by the output capacitor.

At  $t_{on}$ , the switching transistor is OFF and the polarity of the transformer's primary winding immediately inverses. The secondary side's diode is now forward biased, conducts current from the secondary winding to load. This current will decrease linearly, starts from its peak value  $I_{smax}$ , which has the following relationship with primary side peak current:

$$I_{smax} = N \times I_{pmax} = \frac{N_p}{N_s} \times I_{pmax} = \sqrt{\frac{L_p}{L_s}} \times I_{pmax}$$

$$= \sqrt{\frac{40}{8}} \times 3.5 = 7.83 \text{ A}$$

(2.3)

If this current is designed to completely diminish before the switching transistor switches ON again, this mode is called discontinuous current mode. The expected average load current for driving a 1W LED is 0.35 A. The secondary side's diode conducting interval can be known if the moment at which the secondary side's current goes to zero ( $t_2$ ) is identified. The value of  $t_2$  may be obtained from:

$$I_{avg} = \frac{1}{2} I_{smax} \frac{t_2}{T} = \frac{1}{2} I_{smax} \times t_2 \times f$$

(2.4)

$$\Rightarrow t_2 = \frac{2 \times I_{avg}}{I_{smax} \times f} = \frac{2 \times 0.35}{7.83 \times 10^5} = 0.89 \ \mu s \tag{2.5}$$

This calculated value demonstrates that the operating mode is DCM because  $t_2 < T = 1/f$ . The DCM operating mode assures a desired constant output current, delivers an excellent transient response, and also will be able to provide power factor correction feature for the flyback converter. The DCM operating mode, however, requires some components with larger ratings.

As mentioned above, the flyback converter in this project will deploy primary-side sensing and regulating feature. An auxiliary winding of the transformer will be used to monitor the secondary side operations. Assume the inductance of auxiliary winding is 1  $\mu$ H, its voltage will be:

$$V_a = V_p \frac{N_a}{N_p} = V_p \sqrt{\frac{L_a}{L_p}} = 169 \sqrt{\frac{1}{40}} = 26.7 \text{ V}$$

(2.6)

A voltage sense is formed by a zener diode and a resistor. This voltage level will be acquired and then compared with a pre-defined threshold voltage, which is stored by the micro-controller, in order to detect the conducting interval of the secondary side's diode. The secondary side's diode conducting interval will be combined with signal from peak current detector, sample signal of input rectified voltage and the primary side switching current as four inputs of the micro-controller. The micro-controller's PWM feature processes data, then compares with an in-register stored preset value before making decision. If mismatch between the calculated and preset value is not within allowable tolerance, the duty cycle will be adjusted. Otherwise, no action will be triggered from the micro-controller.

#### **2.4 Simulation**

Simulation is vitally an important stage at the beginning of any design process. Unfortunately, it is impossible to set up a straightforward environment for PIC18F4550 micro-controller's behaviors with available tools. By exploiting the first order mathematical model for the flyback converter and using Matlab-Simulink, Cadence's PSpice (OrCAD Capture CIS) and a PID based control scheme, several critical features of the micro-controller (PWM, counter etc.) can be simulated. The simulation process will be discussed in Chapter 3.

#### 2.5 Demo board design

In order to minimize any potential mismatch in design, the PCB design process will start with OrCAD Capture CIS for schematic drawing and then export to OrCAD PCB Editor for layout. The two parts from the same Cadence's Suite helps the design process to be proceeded seamlessly.

Most passive components have defined footprints. However, some components like transformer and micro-controller, whose footprints are not supplied by manufacturers, require manual footprint design. This work becomes less difficult with OrCAD PCB Editor's Footprint Wizard feature. In fact, this feature allows designer to draw any type of footprint, as long as the component's datasheet is available.

Since the design board here is just a demo version, the component selection was not optimized. Some parts might have large footprint and do not follow the board-shrinking spirit due to employing through-hole technology one. The board size can be enhanced by replacing throughhole devices with the same-specification, equivalent SMD parts. This task will be done if: (1) the demo board works properly, and (2) the driver is commercialized.

The PCB design task is finalized by comparing the generated artworks with their predecessor layout. Although the generated artworks can be investigated by PCB Editor itself, the design results should be viewed in a completely independent tool. If the different softwares bring out the same results, the artworks' verification is justified.

### 2.6 Programming

The official programming language that will be used for PIC18F4550 micro-controller is C. The Integrated Development Environment and Compiler are free to download from the

manufacturer's website (<u>www.microchip.com</u>). Code will be conveniently loaded to the microcontroller using PicKit3 programmer through USB interface.

## Chapter 3

Simulation of a micro-controller based primary-side sensing flyback converter for LED driver

# **3.1 Introduction**

Simulation plays a vital role in electrical engineering design process. As the electronic circuits and systems have become more complicated, computer simulation has demonstrated its usefulness in comparing the traditional design verification with breadboard [9]. With the development of modern computer technology and algorithms, the results of simulation can perfectly reflect behaviors of electrical components. Simulation helps design engineer to save not only the cost but also a lot of time since it provides useful information about every component effects on the overall result. Therefore, the LED driver design process in this project started with simulation task.

When it comes to simulation in electrical engineering, Cadence's PSpice (OrCAD Capture CIS) emerges as one of the most favorite choices for designer engineers. It is convenient, powerful,

and has very friendly user interface. PSpice not only provides a tremendous amount of parts but also motivates the designer's creativity by developing new components on his own. Because of this feature, there are thousands of self-made libraries distributed on the Internet, including both free and paid packages. In addition, many electronic vendors consider PSpice as an industrial standard and publicly supply their own product's libraries for free of charge.

Despite the fact that there are numerous ready-to-use PSpice-compatible libraries of microcontroller, it was hard to find a library which contains our chosen one, PIC18F family. The reason originated from the fact that this microchip's product series offers too many advanced features to represent in just only one mathematical model. This means that at the very first step of the simulation task, we have to find a solution to overcome the absence of PIC18F family library.

Two solutions were proposed. The first one is to construct a mathematical model for PIC18F4550 micro-controller that presents exactly all behaviors we need from this chip (PWM, counter, etc.). This solution seems to be an overwhelming as well as time-consuming work with low feasibility. The second one is to make use of Cadence's built-in Analog Behavioral Model (ABM) libraries in conjunction with PID-based control algorithm in order to present necessary features of PIC18F4550. This plan promises to provide the same equivalent results but requires a significantly smaller amount of time.

# 3.2 PID-based control scheme

PID is one of the most widely used controllers in industry since it provides not only good output performance in a wide range of working conditions but also the simplicity, ready-to-use tuning

strategy [10]. In this simulation, the popular three-term PID transfer function in frequency domain will be used as follows:

$$G(s) = K_P + \frac{K_I}{s} + K_D s \tag{3.1}$$

in which  $K_P$ ,  $K_I$ , and  $K_D$  are proportional, integral, and derivative coefficients that represent the correspondent terms, respectively. In fact, the derivative term has the following transfer function:

$$G_D(s) = \frac{K_D s}{\tau_D s + 1} \tag{3.2}$$

with  $\tau_D$  is small enough compared to the time constant of the process itself and usually can be neglected. In Simulink, there is a built-in block PID with the following transfer function:

$$G(s) = P + I\frac{1}{s} + D\frac{N}{1 + \frac{N}{s}}$$

(3.3)

in which *N* is defined as the "Filter Coefficient", which has a default value of 100. With *P*, *I*, and *D* play role of  $K_P$ ,  $K_I$ , and  $K_D$ , we can see the relationship:  $\tau_D = 1/N$ . Therefore, the value of 100 for N could be left unchanged or set as large as possible while working with this built-in PID block in Simulink.

## 3.3 Modeling the flyback converter

A mathematical model for the primary-side sensing flyback converter is necessary for control design procedure. As the flyback converter operated in discontinuous current mode (DCM), a very high power factor will be achieved [11]. Because of this reason, the expected input

characteristics of LED are similar to a pure resistor that we use as a load in this simulation. With such resistor-like load, the control target is achieving and maintaining the output voltage of the flyback converter as close to 32 V as possible so that the current flowing through 1W LEDs is about 350 mA while the settling time and rising time should be small enough to guarantee the fast response of an LED bulb. The percent overshoot is also expected to be small as an LED is basically a diode, so that a small change above the forward biased voltage could make a significant change in current. A first-order model for the flyback converter is suitable for this research because it provides not only the simplicity but also the reasonable accuracy.

For the current flyback converter, its mathematical model was built based on the following parameters and formulae using Matlab:

- L\_PRI= $40*10^{-6}$ : Inductance of the transformer's primary coil (40  $\mu$ H).

- L\_SEC= $8*10^{-6}$ : Inductance of the transformer's secondary coil (8  $\mu$ H).

- Vin=1.414\*120: Amplitude value of input voltage ( $120\sqrt{2} \approx 169$  V).

- Np=2.25: Number of turns for the transformer's primary coil.

- Ns=1: Number of turns for the transformer's secondary coil.

- Naux=0.83: Number of turns for the transformer's auxiliary coil. An auxiliary coil will be used to detect the conducting time of the secondary side's diode without using a feedback system directly from the secondary side. The advantages of this primary-side sensing technique was introduced in Chapter 2.

- $f=100*10^{3}$ : Switching frequency of the flyback converter (100 kHz).

- Vout=32: The expected value of output voltage (32 VDC).

- Iout=0.350: The expected value of output current (350 mA).

- Rout=Vout/Iout: Ohm's law used to calculate equivalent resistance of the LED with assumption that flyback converter was operated in DCM.

- Caux=100\*10^-9: Capacitance of load capacitor on the auxiliary side (100 nF).

- Csec=100\*10^-6: Capacitance of load capacitor on the secondary side (100  $\mu$ F).

The first order transfer function of the flyback converter has a form of [12]:

$$T(s) = \frac{\text{Gain}}{\frac{1}{2}R_eC_e + 1}$$

(3.4)

in which  $R_e$  and  $C_e$  are the equivalent resistance and capacitance of the flyback converter. They are calculated for the simulated model as follow:

- Re=(Vout)^2/(Vout\*Iout): Equivalent resistance is exactly the calculated resistance of the LED above.

- Ce=Caux+Ns/Naux\*Csec: Equivalent capacitance of the model is calculated as a sum of load capacitance on the auxiliary side and the load capacitance on the secondary side referred to the auxiliary side. The factor ½ on the denominator of the transfer function accounts for those two load capacitors.

The "Gain" value depends on the mode of operation. With the intended mode being selected as DCM, formula to calculate the value for "Gain" is:  $Gain=Vin*Ns/Np*sqrt((Re)/(2*L_SEC*f))$ .

Finally, the first order transfer function in frequency domain of the flyback converter is:

$$T(s) = \frac{570.1}{0.04642s + 1} \tag{3.5}$$

Having the mathematical model for the flyback converter means the object control has been identified. We proceed to the next step: design the controller and the feedback system.

### 3.4 Controller and feedback system design

The chosen controller is PID-based scheme for various advantages as mentioned in Section 2 of this Chapter. For this type of controller, several ways to determine gains, called PID tuning, were introduced.

The first approach is manual tuning in which all three parameters  $K_P$ ,  $K_I$ , and  $K_D$  are acquired manually with no math required [13]. Since there is no explicit mathematical formula to obtain PID's parameters, this method may bring some confusions to inexperienced designers due to complicated relationships between the adjustments of gain and design specifications. For example, the increase of  $K_P$  helps lower the steady-state error, but equally makes the percent overshoot increase with a very little impact on the settling time. Meanwhile changing  $K_I$  on the same manner brings 0 for steady-state error with the improvement for both the percent overshoot and the settling time. In addition, determining gains without a mathematical formula means the design process will be done with testing and detecting. This method might be a very timeconsuming and tedious task for people with no deep insight about PID.

A widely used rule of thumb for manual tuning is to first set both  $K_I$  and  $K_D$  to 0.  $K_P$  will be adjusted increasingly until the system becomes oscillated using root locus method. The value of  $K_P$  that makes the system oscillated will be divided by 2 to obtain the proportional gain. Next,  $K_I$ will be incremented in order to achieve a reasonable rise time. The integral gain should not be too big to avoid instability for the system. Next, the derivative gain will be adjusted to meet the

design specifications of the percent overshoot and the settling time. This process seems simple at first but it requires a lot of experiments and does not guarantee the convergence.

The Ziegler-Nichols tuning method was introduced in the 1940s. It is a proven method with explicit mathematical formula for each P, PI, and PID controllers. It is useful for the case that requires an ability of disturbance rejection and a fast closed-loop step response with no excessive oscillation. The process of identifying gains establishes in the same manner with manual tuning by setting both the integral and derivative gains to zero, and then increasing the proportional gain until the system reaches its boundary of oscillation. The value of  $K_P$  that makes the system become oscillated was denoted as  $K_U$  – the ultimate gain. Measuring the period of system oscillation, we acquire  $T_U$  – the ultimate period.

From the ultimate gain  $K_U$  and the ultimate period  $T_U$ , the proportional, integral and derivative gains of P, PI, and PID controllers will be determined, depending on the type of the controller being considered. If a proportional controller is enough, its proportional gain will be set as  $0.5K_U$ . In case a proportional-integral controller is necessary, the proportional gain and integral gain are  $0.45K_U$  and  $0.54K_U/T_U$ , respectively. If a full three-term PID controller is required, the proportional, integral, and derivative gains are  $0.6K_U$ ,  $1.2K_U/T_U$ , and  $0.6K_UT_U/8$ , respectively.

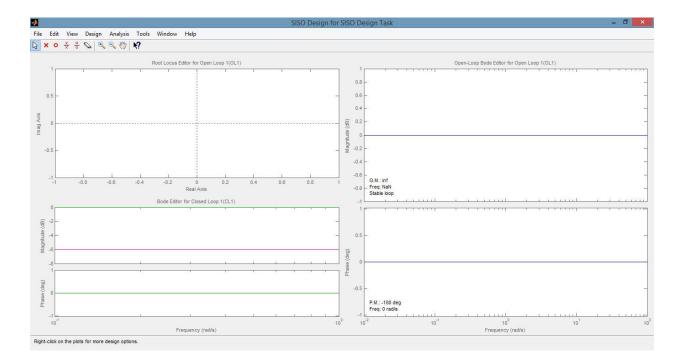

Design with aid from software has emerged as the first choice for engineers in the recent two decades. With the rapid development of computer technology and algorithm, CAD/CAM tools guarantee optimized, highly reliable, consistent results in acceptable running time. The disadvantage of using tuning software is the relevant cost for purchasing and training might be relatively high. In this project, we will use a low-level aided tool, named SISO Tool for design purpose. This software, which is a built-in part of MATLAB [14], was used in companion with Simulink to design the PID controller for the flyback converter.

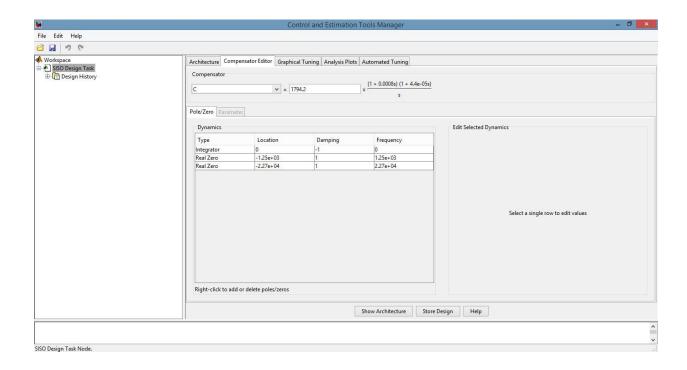

SISO Tool is a powerful software which supports designer in real-time tuning controllers. It is easy to use with friendly graphic user interface (GUI) and does not require any pre-course training. Being integrated in MATLAB, there is no need to pay any additional cost. Any adjustment done during the design process will be immediately demonstrated on selected graphs with almost no delay. After establishing SISO Tool in MATLAB, by default, two windows pop out as shown by Figs. 3.1 and 3.2: "Control and Estimation Tools Manager" window for setting and tuning tasks, and "SISO Design for SISO Design Task" window for presenting real-time update design results.

| <b>W</b>               |                                 | Control and Estimation Tools Manager                      | - 🗇 🗙 |

|------------------------|---------------------------------|-----------------------------------------------------------|-------|

| File Edit Help         |                                 |                                                           |       |

| <u>ମ ଜ</u> ାନ          |                                 |                                                           |       |

| ♦ Workspace            | Architecture Compensator Editor | Graphical Tuning   Analysis Plots   Automated Tuning      |       |

|                        | Control Architecture            | Modify architecture, labels and feedback signs.           |       |

|                        | Loop Configuration              | Configure additional loop openings for multi-loop design. |       |

|                        | System Data                     | Import data for compensators and fixed systems.           |       |

|                        | Sample Time Conversion          | Change the sample time of the design.                     |       |

|                        | Multimodel Configuration        | Change the nominal plant and multimodel options.          |       |

|                        |                                 | Show Architecture Store Design Help                       |       |

|                        |                                 |                                                           | ~     |

| SISO Design Task Node. |                                 |                                                           |       |

**Figure 3.1** - User interface of SISO Tool. A new design can be created or a previous work can be loaded.

In "Control and Estimation Tools Manager" window, under "Architecture" tab, the software provides us with several common controls architecture in "Control Architecture" option. Because there is no special requirement for control architecture, we leave it as default with the most common form, as shown in Fig. 3.1. The mathematical model for the flyback converter, which was found in the previous section by using numerous MATLAB commands, could be imported here to "G" block by "System Data" option. The work now is to design the compensator "C", and the feedback gain, if necessary.

Figure 3.2 - Real-time update designed graphs. Up to 6 graphs can be shown at the same time.

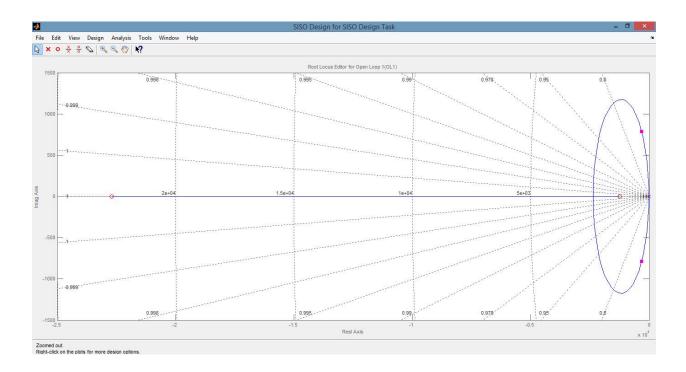

As shown in Fig. 3.2, SISO Tool provides us with several graphs, which includes but is not limited to root locus, Bode plot for closed-loop, and open-loop system. However, we can add up to 6 figures to this window in order to monitor the results of tuning. This task is done by using tab "Graphical Tuning" on the "Control and Estimation Tools Manager" window. From "SISO Design" window, we are able to investigate every change of graphs by relatively adding to the controller either a pole/pair of poles, or a zero/a pair of zeros. These added poles and/or zeros will be immediately updated on the "Control and Estimation Tools Manager" window, under "Compensator Editor" tab. The position of poles and/or zeros could also be precisely selected here and then compare with the results at "SISO Design" window.

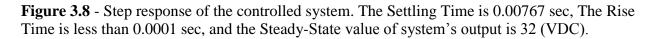

After doing some preliminary calculations, it was found out that by putting two zeros at  $s_1 = -1250$  and  $s_2 = -22700$  on the left-hand plane as shown in Fig. 3.3, all design requirements can be totally satisfied. An input reference of 1.5 and a feedback gain of 0.046875 (1.5/32) were also added in order to achieve the value of 32 VDC as a result of step response. By the time two zeros were added, the system root locus graph was also updated as illustrated in Fig. 3.4.

By adding two zeros as stated above, the transfer function of designed PID controller now is:

$$C(s) = 1795 \frac{(1+0.0008s)(1+4.4e-05s)}{s}$$

= 1.51 +  $\frac{1795}{s}$  + 6.3164 × 10<sup>-6</sup> s (3.6)

**Figure 3.3** - Adding two zeros at -1250 and -22700 to the compensator. SISO Tool also shows the function of equivalent controller.

**Figure 3.4** - The system's Root Locus graph was updated with two added zeros and one pole (at s = 0).

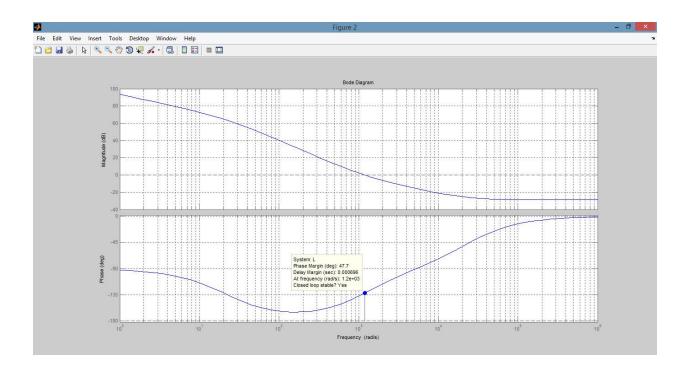

**Figure 3.5** - Bode plot of the closed loop system with demonstration of stability. The closed loop system is stable and the phase margin is 47.8°.

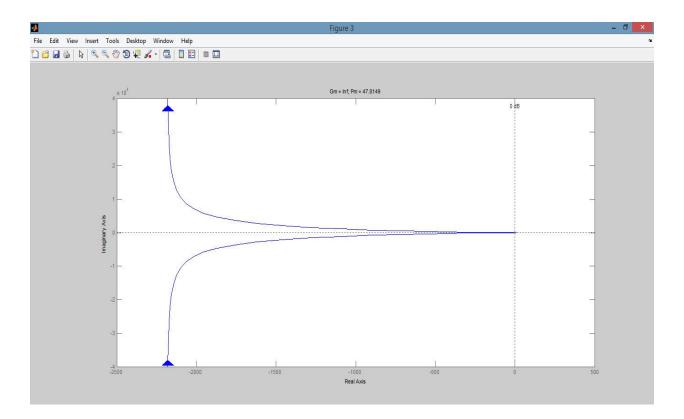

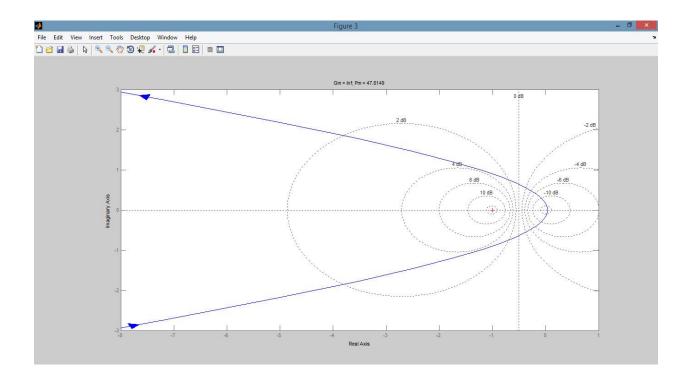

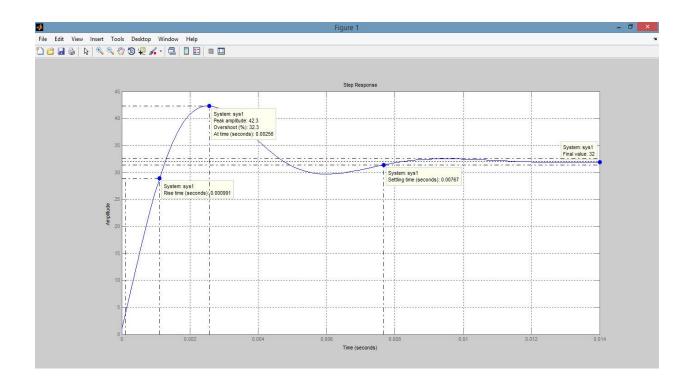

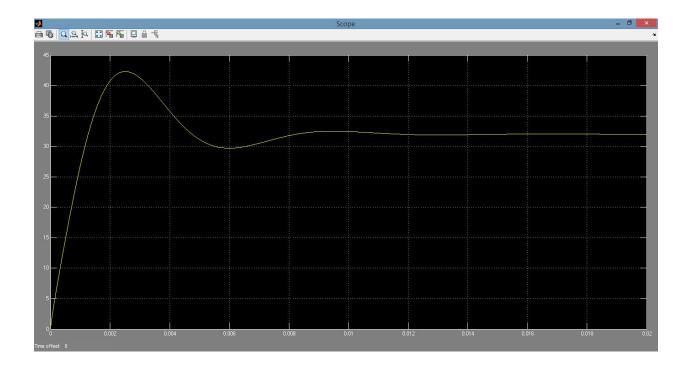

With this PID controller, the system's stability is guaranteed with 47.8° phase margin as indicated in Fig. 3.5. This stability feature was investigated one more time by using Nyquist criterion and the same result was achieved since the system's contour does not encircle the (-1, 0) point and the number of pole for loop gain transfer function is zero [15]. Fig. 3.6 illustrates the Nyquist plot for the current system. Fig. 3.7 zoom in (-1, 0) point to show the relative position of (-1, 0) point with the contour. With such a stable system, the step response is shown in Fig. 3.8. The settling time is merely 0.00767 sec while the rising time is more impressive with just less than 0.0001 sec. The output of the model is 32 V as expected.

In order to check the design results, a simulation in Simulink was employed. The PID controller block was built as in Fig. 3.9, and the whole closed loop system was constructed as in Fig. 3.10.

**Figure 3.6** - Contour of the system loop gain demonstrated on Nyquist plot. It does not encircle the (-1, 0) point any time, showing us the credit of a stability system.

Figure 3.7 - A closer view at the (-1, 0) point.

After running the simulation, then comparing the responses of Simulink simulation (Fig. 3.11) with the designed result from SISO Tool (Fig. 3.8), there was almost no difference. Therefore, the designed PID controller is now ready to be implemented in PSpice simulation.

Figure 3.9 - The PID controller in Simulink.

Figure 3.10 - Simulation of the closed loop system in Simulink.

**Figure 3.11** - Simulation result from Simulink. This result matched perfectly with the designed result from SISO Tool.

## 3.5. Simulation with Cadence's PSpice

The next step in the design process is simulating with full converter using Cadence's PSpice software. There are a lot of reasons for choosing PSpice, among them are two highlight features that make this software the most favorite one for many design engineers: (1) providing high reliable results with significantly fast running time, and (2) having a diversified library of component which seamlessly supports designer not only on stage of simulation but also on task of printed circuit board (PCB) design. The PCB design process was also implemented using several parts from Cadence Product Suite, as will be demonstrated in Chapter 4.

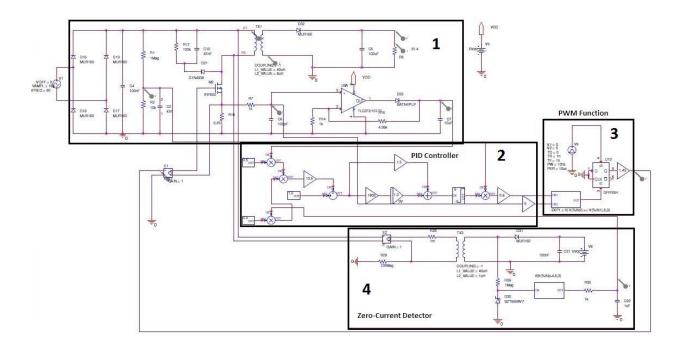

The schematic for full converter simulation is shown in Fig. 3.12. It can be divided into four main parts. The first part, which denoted "1" in Fig. 3.12, is the main circuit of the LED driver. It

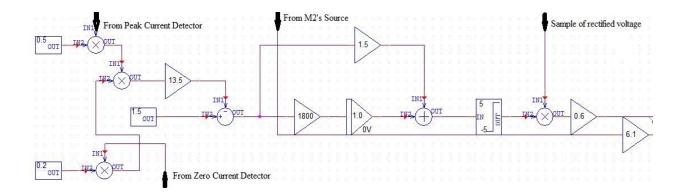

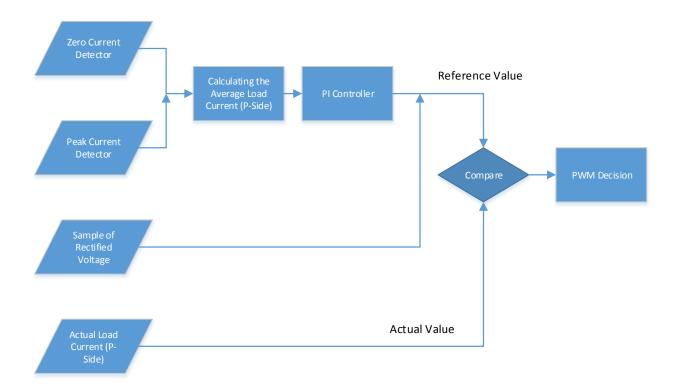

consists of: a rectified circuit which converts 120 rms-value AC source into a DC source, a snubber circuit with function of reducing voltage stress on transistor due to switching action, a flyback topology, and a peak current detector. The second one, "2" is the PID controller which works essentially as a PI controller since the derivative gain is significantly small compared to the proportional gain and integral gain, and its impact can be neglected. The main purpose of using the third part, "3" is illustrated the function of PWM feature of PIC18F series micro-controller. The fourth part, "4", named Zero Current Detector, has its function of detecting and calculating the conducting time of the diode on the secondary side. In practice, except the part 1 has its real, physical circuit, the other three parts were implemented by the micro-controller.

Figure 3.12 - Schematic for full converter simulation in Cadence's PSpice.

Part "1" will connect directly to the standard household120 rms-value AC source, and then rectifying it to a DC source with its peak value of approximately 170 V. A sample waveform of rectified voltage will be extracted and feed through to the micro-controller for control purpose.

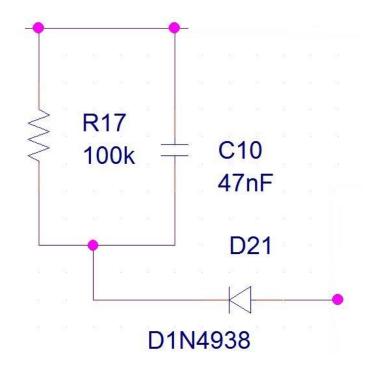

The introduction of the snubber circuit (Fig. 3.13) helps to solve the problem of an excessive voltage might be induced on the switching transistor during turn-off process due to the transformer leakage inductance [16]. It keeps the transient oscillation voltage in safe boundaries, thus lowering the power dissipation of the switching transistor.

Figure 3.13 - The Snubber Dissipative Circuit.

When the switching transistor is switched off, diode D21 is forward biased. The energy from the transformer's leakage inductance due to inductive kick phenomenon will be discharged to capacitor C10 [17]. Therefore, capacitor C10 should be able to store its initial charged energy plus the energy transferred from transformer inductance. According to [16], the minimum value for C10 can be calculated from:

$$C = \frac{L_L \times I_{p\,\text{max}}^2}{\Delta V_C \left(\Delta V_C + 2V\right)} \tag{3.7}$$

where  $L_L$  is the leakage inductance of the transformer. With the intended EFD-20 transformer, from its datasheet:  $L_L = 4 \times 0.24 = 0.96 \ \mu\text{H}$ .  $\Delta V_C$  is the acceptable change of voltage across capacitor C10, that has range from 40 V to 60 V. We can choose a value of 50 V for this calculation. *V* is the secondary side voltage reflected to the primary side, which is calculated as N (= N<sub>P</sub>/N<sub>S</sub>) times of forward biased voltage of the secondary side diode (choose the value of 0.8 V) and the output voltage (32 V). Thus, V =  $2.23 \times (32 + 0.8) = 73.14$  V.

The minimum value for capacitor C10 of the snubber circuit is:

$$C = \frac{0.96 \times 10^{-6} \times 3.5^2}{50(50 + 2 \times 73.14)} \approx 1.2 \times 10^{-9} = 1.2 \text{ nF}$$

(3.8)

The value for resistor R17 should be chosen so that the time constant of R17-C10 circuit is much larger than the switching period ( $1/100 \text{ kHz} = 10^{-5} \text{ s}$ ). In addition, this resistor should be able to dissipate the total transferred energy from transformer's leakage inductance as well as stored energy in capacitor C10. Also according to [16], the formula to calculate power for this resistor is:

$$P_R = \frac{L_L \times I_{p\,\text{max}}^2 \times f}{2} + \frac{V^2}{R}$$

(3.9)

The value of C10 and R17 are tested and adjusted, if necessary, in order to minimize their impacts on the transient response. Finally, with C10 = 47 nF and R17 = 100 k $\Omega$  all the required specifications are justified. The circuit's time constant is  $(47 \times 10^{-9}) \times (100 \times 10^{3}) = 470 \times 10^{-5}$  s, which is much larger than the switching period of  $10^{-5}$  s. The minimum dissipative power for resistor R17 is calculated as:

$$P_{R} = \frac{L_{L} \times I_{p\max}^{2} \times f}{2} + \frac{V^{2}}{R} = \frac{0.96 \times 10^{-6} \times 3.5^{2} \times 10^{5}}{2} + \frac{73.14^{2}}{10^{5}} = 0.641 \text{ W}$$

(3.10)

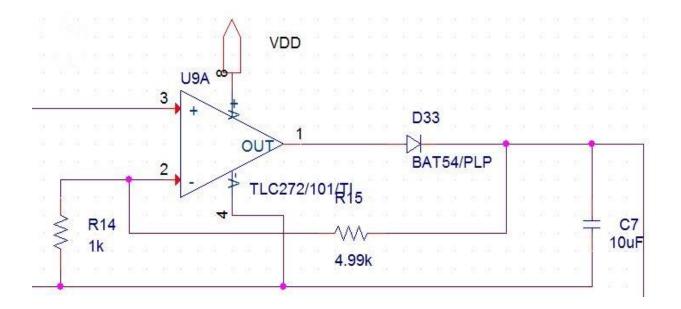

The intention of using the primary-side sensing and control is attained by using a peak-currentdetector circuit for obtaining secondary side's peak current with no device connected to the secondary side at all. The peak current detector, which is shown in Fig. 3.14, receives the waveform of switching current to its port 3 and outputs the maximum value of the primary side current. This value is just the value of maximum secondary side current referred to the primary side. The actual secondary side's current is proportional to the primary side's quantity by a factor of N<sub>p</sub>/N<sub>s</sub> – the turn ratio of transformer [18]. This peak value, along with the waveform of the primary side current will be delivered to the micro-controller to calculate and compare. In simulation, the peak current value is a factor of feedback signal calculation process while the waveform of the primary side current will be compared with the calculated quantity in order to control the PWM mechanism.

**Figure 3.14** - The Peak Current Detector, a mechanism of primary side sensing for detecting the peak current of secondary side circuit without any contact.

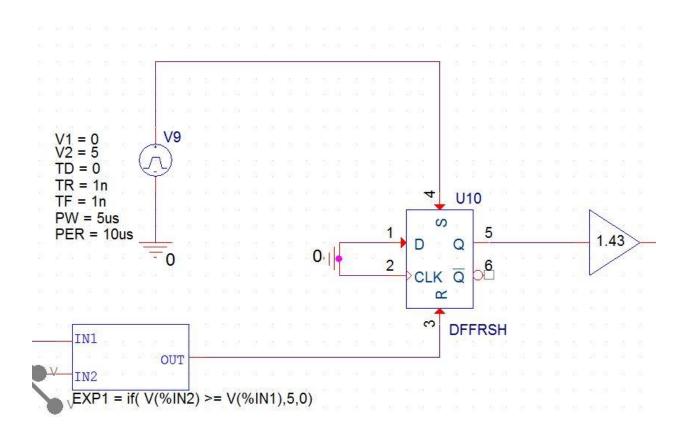

**Figure 3.15** - Demonstrating the PWM mechanism in the micro-controller based LED driver simulation.

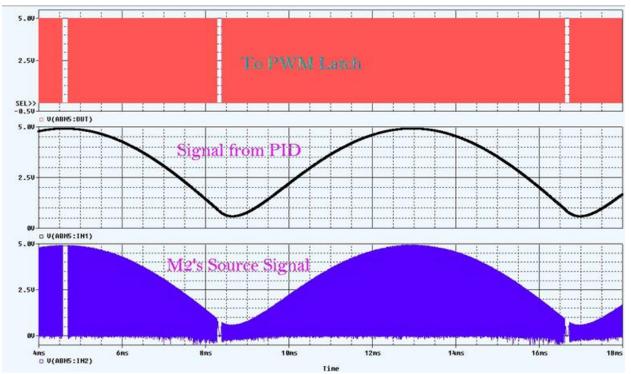

Part 3 illustrates the PWM mechanism of providing the driving signal for switching transistor M2. The post-processed signal from PID controller (IN1), which is chosen as the reference signal, will be compared with signal that represents the primary-side current which flows through the switching transistor (IN2) as shown in Fig. 3.15. If IN2 signal is greater than or equal to IN1 signal, a logic "1" will be send to "R" port on S-R latch. It means that the output of the latch will be forced to low, Q = 0 and the switching transistor M2 is OFF. The S-R latch's output will stay low as long as IN1 signal is smaller than IN2 signal. When IN2 signal is smaller than IN1 signal, a logic "0" exists at "R" port and the output of the S-R latch will be forced high, making the switching transistor to be conducted. Because the output of the S-R latch is just about 3.5 V, a

gain block of 1.43 was used to achieve 5V value to the gate of M2 as shown in Fig. 3.15. Those sequences of action describe exactly the PWM mechanism of PIC18F micro-controller, which will be implemented through programming with algorithm as in Fig. 3.16. In this simulation, ABM (analog behavioral modelling) blocks are used to demonstrate these operations. As will be shown later, ABM blocks will also be employed in parts 2 and 4 which function as the zero current detector as well as to transfer the model of PID controller from Matlab-Simulink to PSpice.

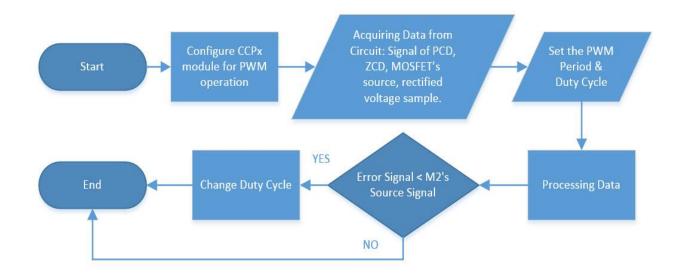

Figure 3.16 - Flowchart of PIC18F based LED driver's algorithm.

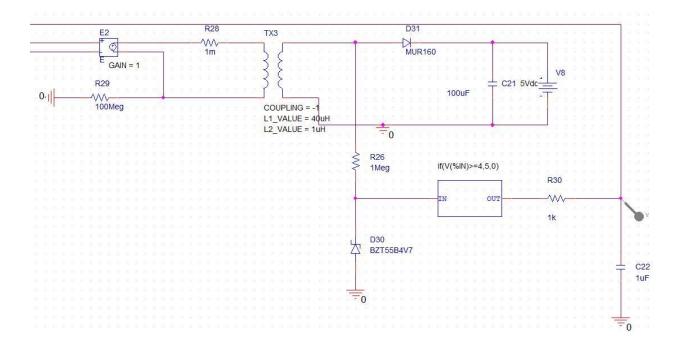

The zero current detector (Fig. 3.17) is actually a virtual circuit whose function is to monitor and calculate the conducting period of the secondary side's diode. The main advantage of the "primary-side sensing" circuit, is the absence of optocoupler, which makes it a more stable sensing circuit. In application, a multi-winding transformer is required. Therefore, along with primary and secondary windings, the third winding's voltage can be used to detect the conducting operation of the secondary side's diode. In Cadence's PSpice, however, there is no

model for multi-winding transformer [19]. Despite the fact that we can design and then use a new 3-winding transformer model, it is more convenient to use an auxiliary transformer instead. Two terminals of the main transformer's primary winding will be connected to another transformer, and a similar-secondary-side circuit will be constructed in order to investigate the secondary side's diode conducting operation. Using a voltage divider which was constructed by a resistor in series with a Zener diode, the status of the secondary side's diode can be obtained through the voltage level of Zener's cathode. After several times of running and measuring, the threshold value of voltage level of Zener's cathode at which the conducting state of secondary side's diode reversed is found to be 4 V. An ABM block with "one input, V out" was used to do that logic expression. Whenever the voltage at Zener's cathode (reflects the anode voltage at the secondary side's diode) is greater than or equal to 4V (i.e., anode voltage of the secondary side's diode is greater than 5 V), the output of the conditional ABM block is 5 V. It means that the secondary side's diode starts to conduct. Meanwhile, the dropping of voltage at Zener's cathode below the threshold of 4 V is the sign that conducting activity of the secondary side's diode is halted. The output signal from ABM block will be fed through a low-pass filter and then contributed to the calculation of output, which was used as feedback signal for PID controller. In application, all is needed to do is just monitoring the voltage of Zener's cathode (which reflects the voltage of the auxiliary winding) and using a counter of micro-controller to achieve the conducting time of the secondary side's diode.

As stated above, the derivative gain value is just  $K_D = 6.3164 \times 10^{-5}$  which is less than 0.01 percent of either the proportional gain  $K_P = 1.51$  or the integral gain  $K_I = 1795$ . Thus, its effect was just minuscule. In practice, the derivative gain should be as small as possible to mitigate the effects of noise. Hence, the designed PID controller (in reality, a PI controller) from Matlab-

37

Simulink was transferred to Cadence's PSpice in a form of PI controller using ABM blocks as shown in Fig. 3.18. This PI controller has a reference input 1.5 as in SISO Tool/Simulink design and the feedback signal is the combination of the peak current detector and the zero current detector's outputs. The specific formula of this feedback signal is [20]:

$$I_{avg,p} = \frac{1}{2} I_{p \max} \frac{t_{on_s}}{T}$$

(3.11)

in which  $I_{pmax}$  is obtained from the peak current detector, and the ratio between the secondary side's diode "on" time  $t_{on_s}$  and the switching period *T* is obtained from the zero current detector.

## Figure 3.17 - Visualizing the Zero Current Detector by employing ABM blocks.

The output of PID controller will be multiplied with the sampled waveform of rectified voltage to make the reference signal for PWM mechanism. The signal to be compared is the switching current measured at the gate of MOSFET M2, which is converted to voltage by a  $0.25\Omega$  resistor. The flowchart of receiving, combining, processing, and comparing is illustrated in Fig. 3.19.

Figure 3.18 – PID controller in PSpice.

Figure 3.19 – Flowchart of control PWM mechanism in PSpice simulation.

# **3.6 Simulation results**

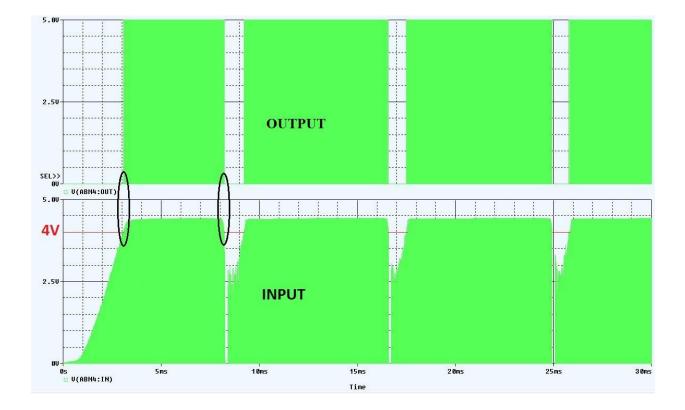

After setting the simulation profile, the simulation was run several times so all the results were investigated carefully. Fig. 3.20 shows the input and output signals of the zero current detector.

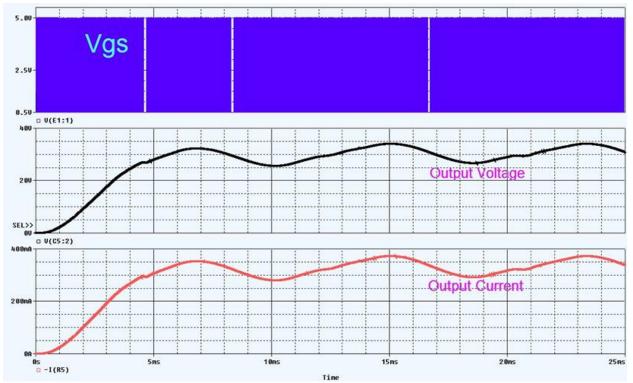

The threshold voltage at which the output is high is 4V. Fig. 3.21 demonstrates the PWM mechanism which will be implemented by the micro-controller. The signal from PID (black line), which is chosen as the reference will be compared with MOSFET M2's source signal (solid purple) in order to generate PWM signal (solid pink), which will be fed to a PWM latch for full simulation of the PWM mechanism. As can be seen from Fig. 3.21, the PWM signal exists whenever the MOSFET M2's signal is at least equal to the reference. Fig. 3.22 shows the voltage at the gate of M2, the output voltage and the output current through the LED load. The average output voltage on LED load is approximately 32V while the average output current is approximately 350 mA. Under the operating of PWM mechanism, the gate voltage of M2 is 5V at intervals that correspond to the existing interval of PWM signal.

Figure 3.20 – Input and output signal of the zero current detector.

**Figure 3.21** – Illustrating of PWM mechanism: comparing signal from PID to MOSFET M2's source signal and generating of PWM signal.

**Figure 3.22** – Voltage at the gate of MOSFET M2 under PWM operation (solid), the output voltage (black), and the output current (red).

Figure 3.23 – Input Voltage and Input Current (Solid).

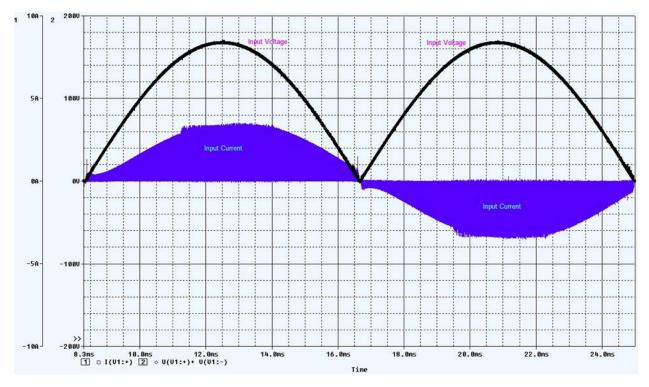

Fig. 3.23 shows the input voltage and input current of the converter. As can be seen, the very slight out of phase between the input voltage and input current demonstrates a very high power factor as expected from a flyback converter operating in the discontinuous current mode (DCM). From the above figures, the simulation results closely matched the results of the intended design. The input peak current is about 3.5 A, the same value as obtained from theory-based calculations in Chapter 2. Meanwhile, Fig. 3.23 is also a useful source to estimate the power factor qualitatively. The input voltage leads the input current by approximately 0.4 ms. The 60Hz source has its full cycle of 1/60 = 16.6 ms, which is equivalent to  $2\pi$ , or  $360^{\circ}$ . Thus, 0.4 ms corresponds to  $0.4*360/16.6 \approx 8.67^{\circ}$ . Therefore, the lagging angle between the input current and the input voltage is  $8.67^{\circ}$ . By definition, the power factor of this circuit is  $\cos(8.67^{\circ}) = 0.988$ . This value is significantly high when compared to the ideal case since the theoretical flyback

converter is among the most favorite choice for its ability of self-power factor correction under discontinuous current mode of operation [21]. The achieved result demonstrated the nearly-perfect relationship between the input voltage and the input current of a flyback converter as mentioned in Chapter 2.

From Fig. 3.22, the average value of output voltage is approximately 32 V, and the average load current is about 350 mA. These values matched with the design expectations, and are evidence for how well the designed PID controller is. In addition, Fig. 3.22 also illustrates the conducting and non-conducting intervals of MOSFET M2. It was continuously switched ON when  $V_{gs}$  has switching pulses while being switched OFF at moments where no  $V_{gs}$  pulse exists. The existence of  $V_{gs}$  pulse contributed to the operation of PWM mechanism which is explained in Fig. 3.12. It clearly shows how signals were compared and then the PWM signal was generated.

## **3.7 Conclusion**

By simulation and comparing the obtained results with the expected design specifications, all necessary functions of PIC18F micro-controller series for the flyback converter LED driver were examined. The design process, which was done by using both SISO Tool of Matlab and Simulink, was successful. Its design product, which was then delicately transferred to PSpice by making use of the built-in ABM blocks for full converter simulation, worked perfectly. For these reasons, the design process of this micro-controller based LED driver can proceed before the hardware implementation.

43

## Chapter 4

## **Hardware Implementation**

#### 4.1 Overview

With the achieved simulation results matched well with theoretical calculations, the design process can now step up to the hardware implementation stage. There are two tasks that needed to be done: (1) Design a printed-circuit board (PCB) for the driver, and (2) Programming for the PIC18F4550 micro-controller.

Before starting a PCB design, the inventory for available components should first be checked. The top priority on selecting a component is to guarantee the system performance. It means that components must be able to provide the same technical parameters as expected. Then, the component's footprint should be as small as possible so that the board size can be reasonable. The board size is not just a cost-saving problem, it is also relevant to aesthetic consideration. For example: Apple Inc. revamped their powerhouse product MacPro in 2012 by a surprisingly way: breaking the motherboard into 3 pieces so every space inside the case is completely exploited. It results in a significant small yet beautiful workstation with extreme power, which attracts a lot of consumer's attention for its unique design [22]. In the current project, the board size plays a very important role in mission of price reducing. There are two ways to optimize the PCB size: (1) Deploying components on both sides of the PCB, and (2) Replacing through-hole devices (THD) parts by surface-mount devices (SMD), which normally have smaller land pattern. However, the current project at first mainly concentrates on circuit performance and the easiness of implementation a demo board, so that problems relevant to board size optimizing and aesthetic consideration are temporarily ignored.

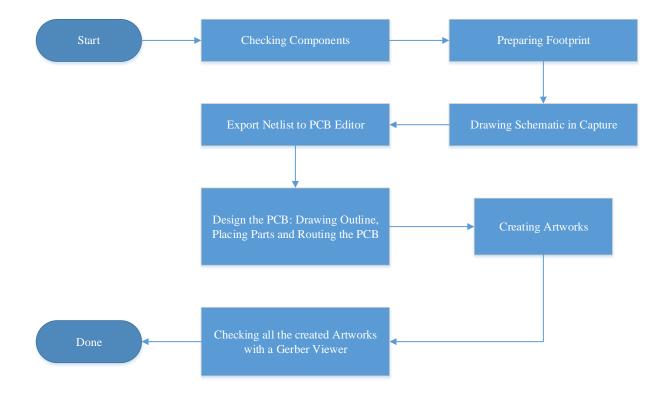

The PCB design process can be summarized as a workflow in Fig. 4.1. The details about "Checking Components" and "Preparing Footprint" stages are illustrated in Fig. 4.2 [23]-[24].

**Figure 4.1** – PCB design process with OrCAD CIS Capture and OrCAD PCB Editor Lite Version [25].

The programming task for PIC18F4550 micro-controller was first executed in MPLAB X, then the resulted HEX file would be loaded into memory using a PicKit3 Programmer. There are two ways to connect the micro-controller to the PicKit3 Programmer. The first method uses breadboard as a mediate environment to connect the micro-controller with the programmer. This method is easy to implement, however, it requires additional components (breadboard, power source for the micro-controller, wires etc.) and the micro-controller must be detached from PCB whenever to be re-programmed. The other way is designing a programmer socket right on PCB. It will make the PCB surface to be more complicated since the programmer needs at least 5 pins to connect. It is not necessary to provide power source since we can supply energy to the micro-controller directly from the PCB. However, a protection must be equipped in order to avoid unwanted phenomena during code-loading process.

Figure 4.2 – Flowchart of Component Preparation.

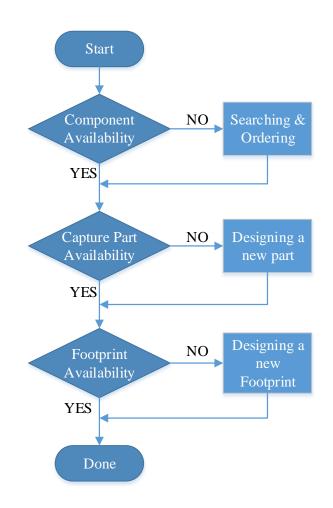

#### **4.2 Component Preparation**

When it comes to a PCB design process, component preparation plays an extremely important role. A designer should be able to keep track of available component and check if it is suitable enough for the project before searching from other sources. Having the list of available components, the next step is investigating their footprints. If one part is adequate in term of technical parameters but has unapproved footprint, it must be replaced by a same-specification one with appropriate footprint. In order to design a PCB with OrCAD Capture CIS and PCB Editor, each component must have two mandatory elements: (1) a Capture part to represent in schematic, and (2) the footprint to represent in layout. Lacking of one element could result in a temporary halt in the design process.

Not all components satisfies both required elements for Capture CIS and PCB Editor as mentioned above. Except common passive parts like resistor, capacitor, and diode etc., which their Capture symbols and footprints hardly have special characteristic, component likes PIC18F4550 micro-controller or IXDN604SIA gate driver have neither compatible Capture symbol nor footprint. Some manufacturers provide their customer with either product's Capturecompatible libraries of symbol or footprint (\*.dra files), some even supply both but it is not the case for this project. After searching thoroughly the Internet, we found out that the better way is to design both Capture symbol and footprint for: the PIC18F4550 micro-controller, the IXDN604SIA gate driver, and the EFD20 transformer. Fortunately, designing a new Capture symbol takes very small amount of time while PCB Editor has a greatly useful wizard tool for footprint design. All we need to find is datasheet for each component.

## 4.3 The PIC18F4550 micro-controller

47