# University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

12-2017

# Asynchronous 3D (Async3D): Design Methodology and Analysis of 3D Asynchronous Circuits

Francis Corpuz Sabado University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Computer Sciences Commons, Electrical and Electronics Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Citation

Sabado, F. C. (2017). Asynchronous 3D (Async3D): Design Methodology and Analysis of 3D Asynchronous Circuits. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/2584

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

# Asynchronous 3D (Async3D): Design Methodology and Analysis of 3D Asynchronous Circuits

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

by

Francis Sabado II

University of Arkansas

Bachelor of Science in Computer Engineering, 2012

University of Arkansas

Master of Science in Computer Engineering, 2015

# December 2017 University of Arkansas

| This dissertation is approved for record | mmendation to the Graduate Council. |  |

|------------------------------------------|-------------------------------------|--|

| Dr. Jia Di                               |                                     |  |

| Dissertation Director                    |                                     |  |

| Dr. Dale Thompson                        | Dr. Jingxian Wu                     |  |

| Committee Member                         | Committee Member                    |  |

| Dr. J. Patrick Parkerson                 |                                     |  |

| Committee Member                         |                                     |  |

#### **ABSTRACT**

This dissertation focuses on the application of 3D integrated circuit (IC) technology on asynchronous logic paradigms, mainly NULL Convention Logic (NCL) and Multi-Threshold NCL (MTNCL). It presents the Async3D tool flow and library for NCL and MTNCL 3D ICs. It also analyzes NCL and MTNCL circuits in 3D IC. Several FIR filter designs were implement in NCL, MTNCL, and synchronous architecture to compare synchronous and asynchronous circuits in 2D and 3D ICs. The designs were normalized based on performance and several metrics were measured for comparison. Area, interconnect length, power consumption, and power density were compared among NCL, MTNCL, and synchronous designs. The NCL and MTNCL designs showed improvements in all metrics when moving from 2D to 3D. The 3D NCL and MTNCL designs also showed a balanced power distribution in post-layout analysis. This could alleviate the hotspot problem prevalently found in most 3D ICs. NCL and MTNCL have the potential to synergize well with 3D IC technology.

#### **ACKNOWLEDGEMENTS**

First, I would like to express my sincere gratitude to my advisor Dr. Jia Di for the continuous support of my Ph.D. study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and writing of this dissertation.

I am also grateful to my committee members: Dr. Dale Thompson, Dr. J. Patrick Parkerson, and Dr. Jingxian Wu for their guidance and support for my research work.

I would like to thank my colleagues at the TruLogic Circuit Design lab and Cato Springs Research Center for their support and collaboration on several projects during my graduate studies. Our deep discussions on various research topics have guided my research work these past years.

Last but not least, I would like to give a special thanks to my family who has been there during the hard times and the fun times. Thank you to my mom and dad, and my brother for their love and support. Your support and encouragements have given me the drive to succeed in all my endeavors.

# **DEDICATION**

To my family whom are always loving and supportive.

# TABLE OF CONTENTS

| 1 | Intr | oduction                                              | 1  |

|---|------|-------------------------------------------------------|----|

| 2 | Pro  | blem Statement                                        | 4  |

|   | 2.1  | Dissertation Contributions                            | 4  |

|   | 2.2  | Dissertation Organization                             | 5  |

| 3 | Bac  | kground                                               | 6  |

|   | 3.1  | NULL Convention Logic                                 | 6  |

|   | 3.1. | 1 NULL Convention Logic Pipeline                      | 9  |

|   | 3.2  | Multi-threshold NULL Convention Logic (MTNCL)         | 11 |

|   | 3.2. | 1 Multi-Threshold NCL Pipeline                        | 14 |

|   | 3.3  | Three Dimensional Integrated Circuits                 | 16 |

|   | 3.3. | 1 Motivation                                          | 17 |

|   | 3.4  | TSV Process Flow                                      | 22 |

|   | 3.4. | 1 Manufacturing technologies for 3D IC                | 23 |

|   | 3.5  | Challenges                                            | 24 |

|   | 3.6  | Discussion                                            | 26 |

| 4 | Asy  | nchronous 3D Tool Flow                                | 27 |

|   | 4.1  | Proposed Flow                                         | 27 |

|   | 4.2  | Circuit Design                                        | 28 |

|   | 4.2. | 1 Unified NCL Environment (UNCLE)                     | 28 |

|   | 4.2. | 2 3D IC Partitioning                                  | 29 |

|   | 4.2. | 3 Automatic Synthesis of Transistor Networks (ASTRAN) | 30 |

|   | 4.3  | Physical Design                                       | 31 |

|   | 4.4  | Standard Library Flow                        | . 32 |

|---|------|----------------------------------------------|------|

|   | 4.4. | .1 Tezzaron 3D Design Kit                    | . 32 |

|   | 4.4. | 2 Cell Schematics                            | 40   |

|   | 4.4. | 3 Cell Verification                          | 40   |

|   | 4.5  | Async3D Library Cell Area                    | 41   |

| 5 | Cas  | se Study: Finite Impulse Response Filter     | . 44 |

| 6 | Ana  | alysis of 3D Asynchronous Circuits           | . 47 |

|   | 6.1  | Design Verification                          | . 47 |

|   | 6.2  | Layout Floorplan                             | . 48 |

|   | 6.3  | Circuit Performance                          | . 50 |

|   | 6.4  | Area/Wire Length                             | 50   |

|   | 6.4. | .1 2D IC Design Circuit Density              | 51   |

|   | 6.4. | 2 3D Design Circuit Density                  | 54   |

|   | 6.5  | Interconnect                                 | . 58 |

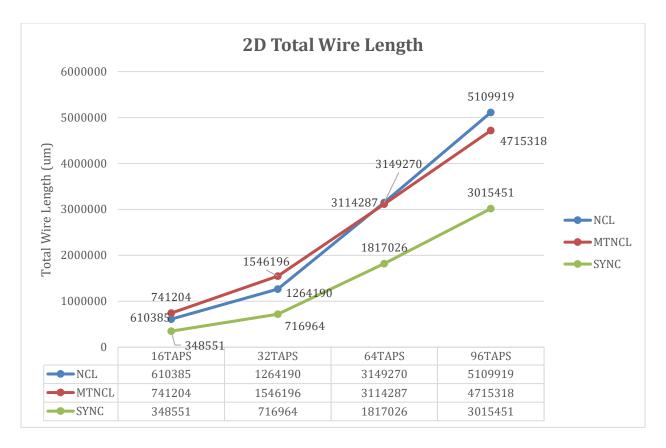

|   | 6.5. | .1 Wire Length Analysis - 2D IC Design       | . 58 |

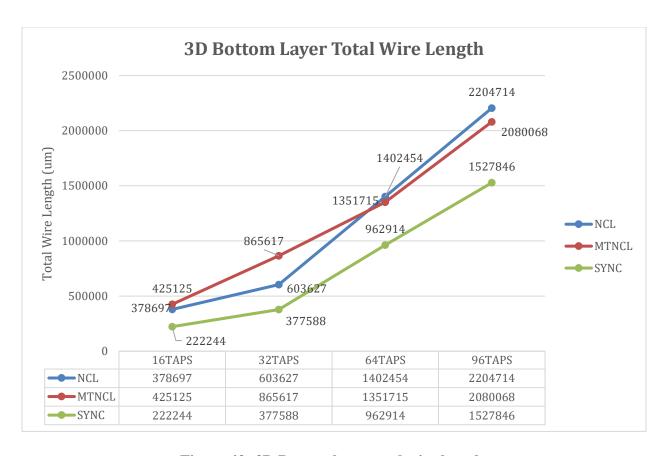

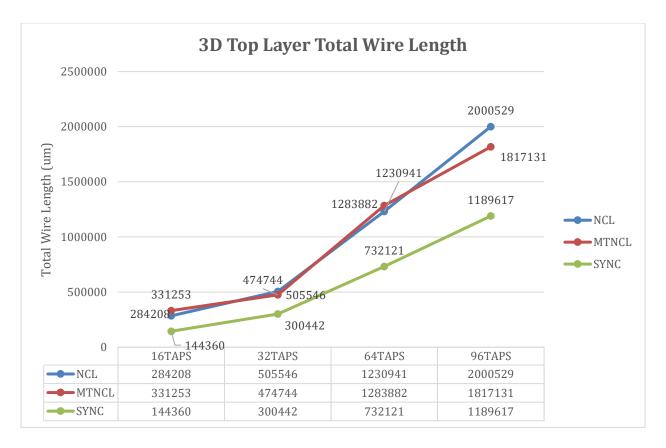

|   | 6.5. | 2 Wire length Analysis - 3D IC Design        | . 59 |

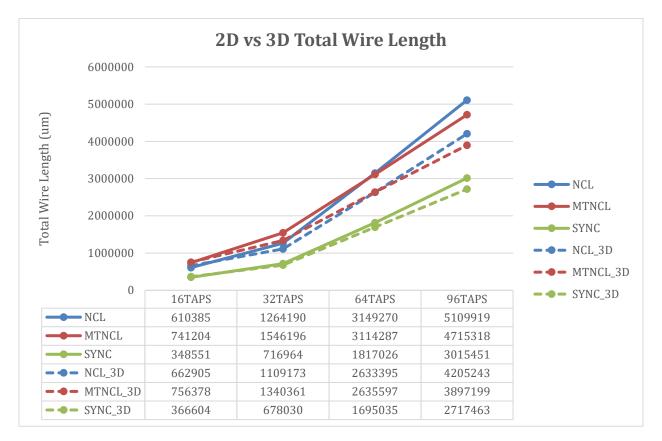

|   | 6.5. | .3 Wire Length Analysis - 2D vs 3D IC Design | 61   |

|   | 6.5. | 4 TSV Count                                  | 65   |

|   | 6.6  | Power Analysis                               | 65   |

|   | 6.6. | .1 Vector-based Power Measurement            | 67   |

|   | 6.6. | 2 Power Data                                 | 68   |

| 7 | Cor  | nclusion                                     | . 73 |

|   | 7.1  | Future Work                                  | .73  |

# LIST OF TABLES

| Table 1: NULL Convention Logic dual-rail encoding. | 6  |

|----------------------------------------------------|----|

| Table 2: NULL Convention Logic fundamental gates.  | 7  |

| Table 3: Gate Transistor Sizing                    | 39 |

| Table 4: Async3D library timing specifications.    | 40 |

| Table 5: Async3D NCL library cell area.            | 42 |

| Table 6: Async3D MTNCL library cell area.          | 43 |

| Table 7: Async3D MTNCL special cells area.         | 44 |

| Table 8: 2D IC area comparison                     | 53 |

| Table 9: TSV/Micro-bumps count.                    | 65 |

| Table 10: 2D Designs power data.                   | 69 |

| Table 11: 3D Designs power data.                   | 69 |

| Table 12: 2D versus 3D power data                  | 70 |

# LIST OF FIGURES

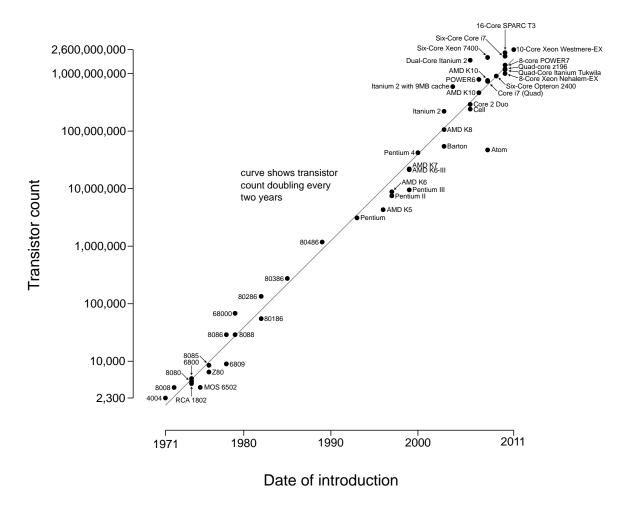

| Figure 1: Transistor count adapted from [8]                       | 2  |

|-------------------------------------------------------------------|----|

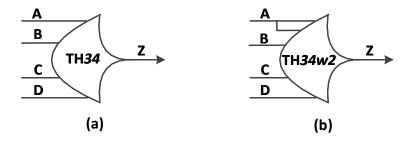

| Figure 2: THmn NCL gates: (a) TH34, (b) TH34w2                    | 8  |

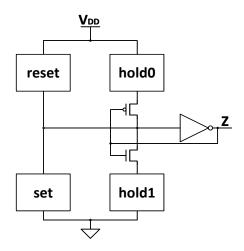

| Figure 3: NCL threshold gate implementation using CMOS technology | 9  |

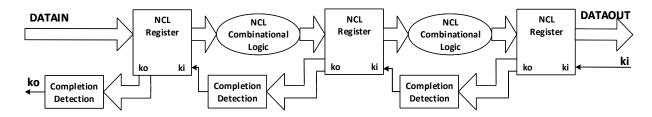

| Figure 4: NCL micro-pipeline architecture [19].                   | 10 |

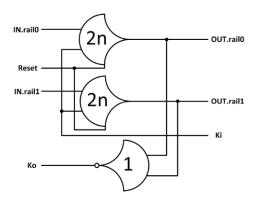

| Figure 5: NCL single-bit dual-rail register [20]                  | 10 |

| Figure 6: Multi-threshold CMOS power gating structure             | 12 |

| Figure 7 Fined Grained MTNCL power gating structure [33].         | 13 |

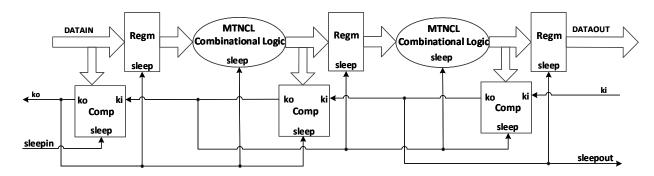

| Figure 8: Multi-threshold NCL pipeline architecture.              | 14 |

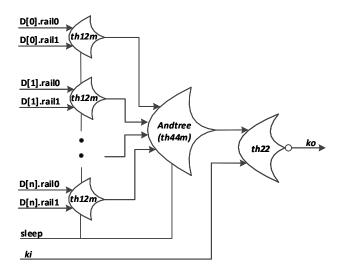

| Figure 9 Early completion detection block in MTNCL pipeline.      | 15 |

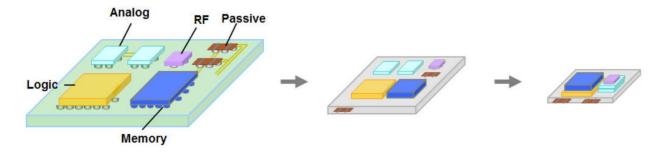

| Figure 10: Trend leading towards 3D IC technology [35]            | 18 |

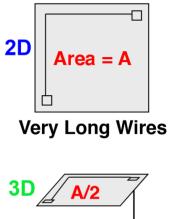

| Figure 11: 2D versus 3D interconnect [36]                         | 19 |

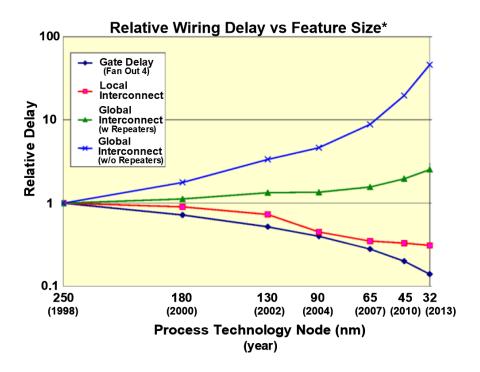

| Figure 12: Global interconnect trends [36].                       | 20 |

| Figure 13: 3D IC bandwidth potential [37]                         | 21 |

| Figure 14: Small form factor consisting of different layers [38]. | 22 |

| Figure 15: 3D cross-section of a TSV [39].                        | 22 |

| Figure 16: Manufacturing 3D ICs [35].                             | 24 |

| Figure 17: 3D IC thermal map [41].                                | 25 |

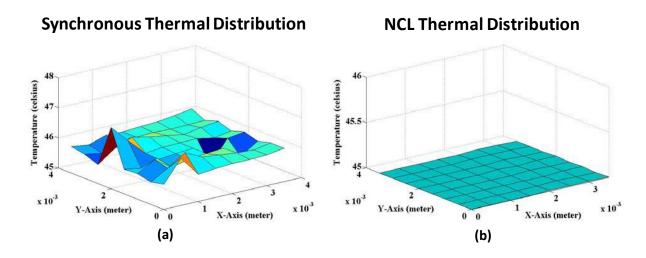

| Figure 18: Synchronous vs NCL thermal distribution [40].          | 25 |

| Figure 19: Async3D tool flow.                                     | 28 |

| Figure 20: Uncle tool flow overview [43] .                        | 29 |

| Figure 21: ASTRAN layout style [45].                              | 31 |

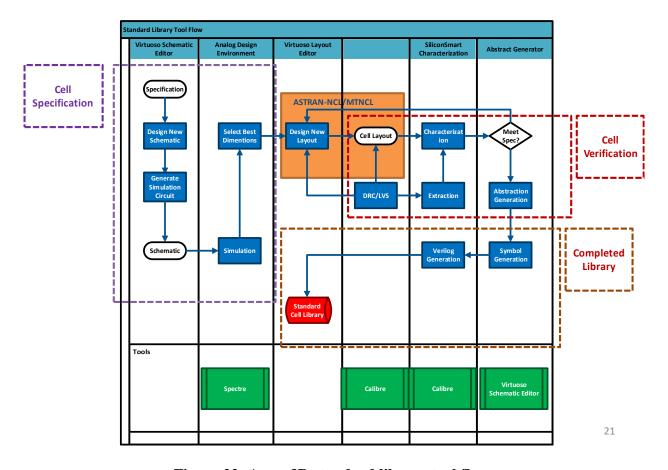

| Figure 22: Async3D standard library tool flow.                    | 32 |

| Figure 23: Tezzaron 3D stack layer [46].            | 33 |

|-----------------------------------------------------|----|

| Figure 24: Two-wafer logic stack [46].              | 34 |

| Figure 25: Async3D layout template.                 | 37 |

| Figure 26: Power rails.                             | 38 |

| Figure 27: Bulk body contacts.                      | 38 |

| Figure 28: Annotated TH44 schematic implementation. | 40 |

| Figure 29: Cell verification flow.                  | 41 |

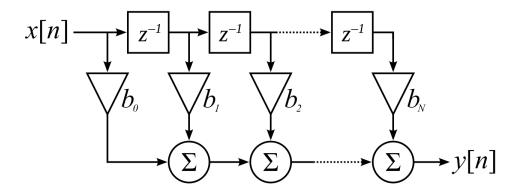

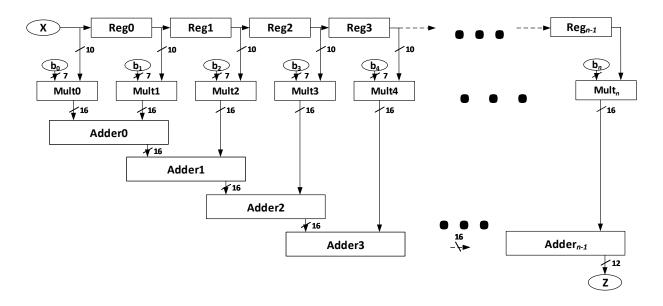

| Figure 30: FIR filter structure.                    | 45 |

| Figure 31: MTNCL FIR filter architecture.           | 46 |

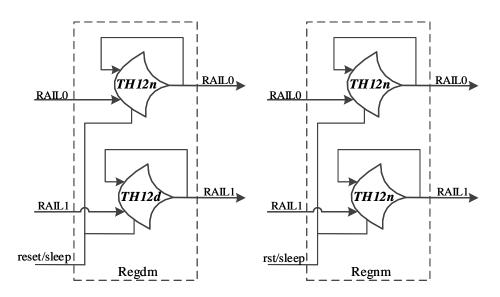

| Figure 32: MTNCL shift registers                    | 47 |

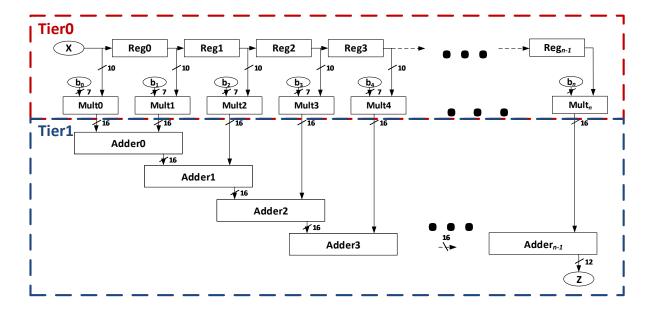

| Figure 33: FIR partitioning.                        | 47 |

| Figure 34: 2D 2.5×5mm floorplan.                    | 49 |

| Figure 35:3D 2.5×5mm floorplan.                     | 49 |

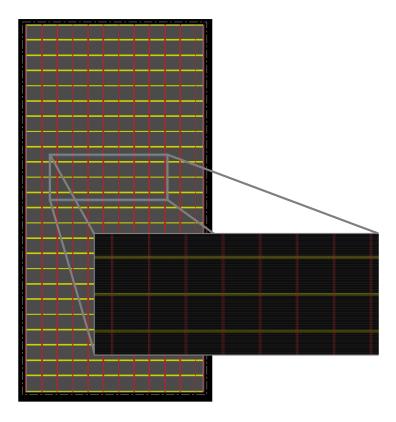

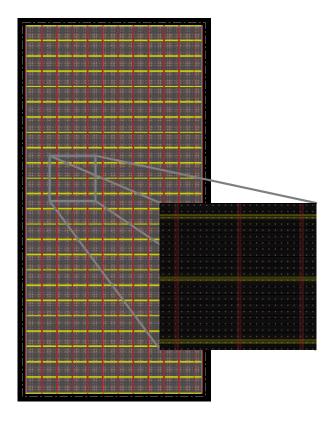

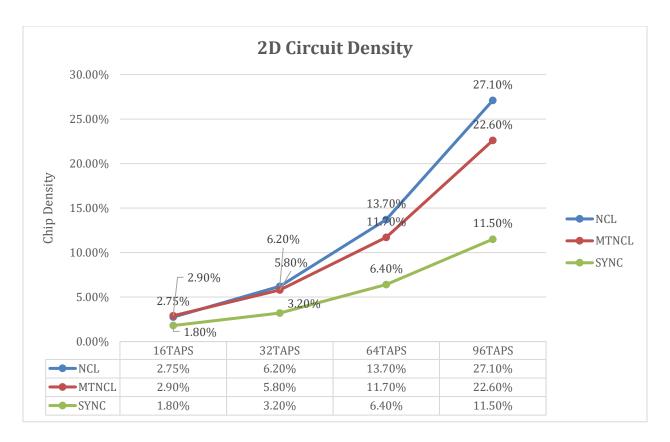

| Figure 36: 2D IC Circuit density                    | 52 |

| Figure 37: 2D IC standard cell area.                | 53 |

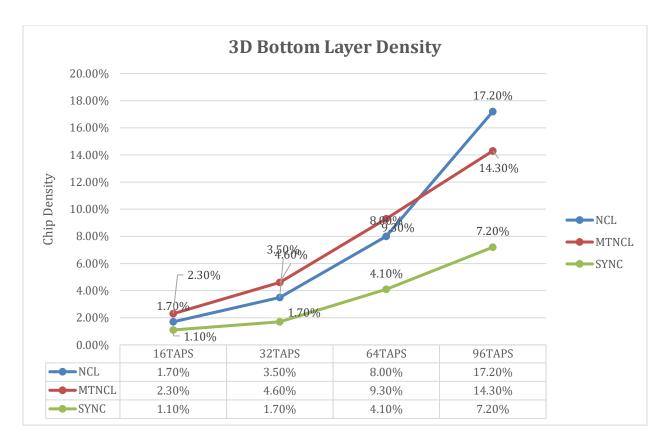

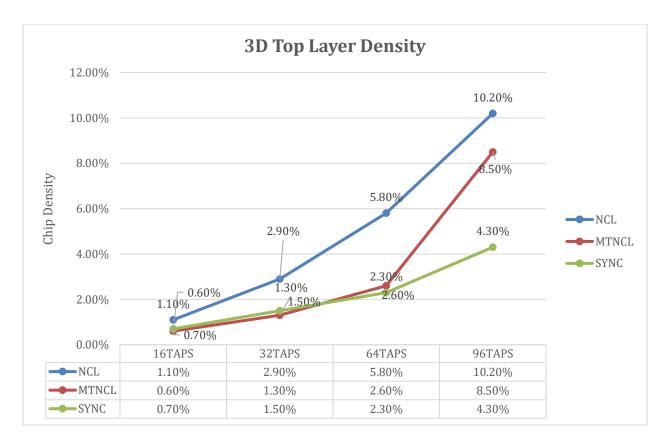

| Figure 38: 3D IC Bottom layer density               | 55 |

| Figure 39: 3D IC Top layer density                  | 56 |

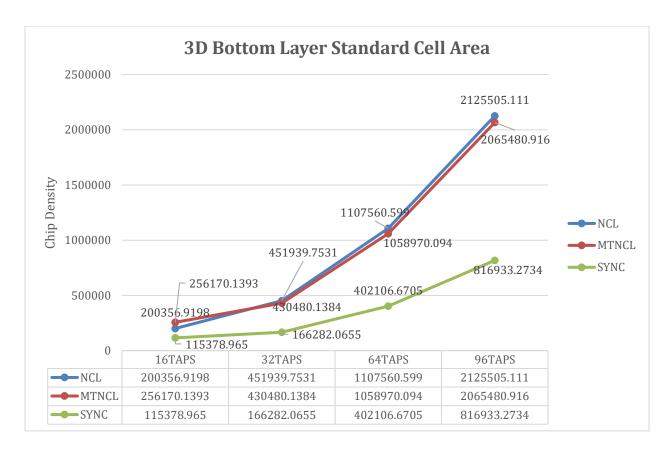

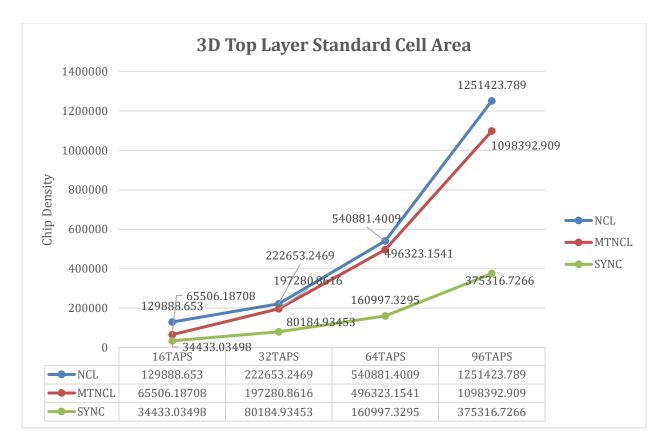

| Figure 40: 3D Bottom layer standard cell area.      | 57 |

| Figure 41: 3D Top layer standard cell area.         | 58 |

| Figure 42: 2D IC total wire length.                 | 59 |

| Figure 43: 3D Bottom layer total wire length.       | 60 |

| Figure 44: 3D Top layer total wire length           | 61 |

| Figure 45: 2D vs 3D IC total wire length            | 62 |

|                                                     |    |

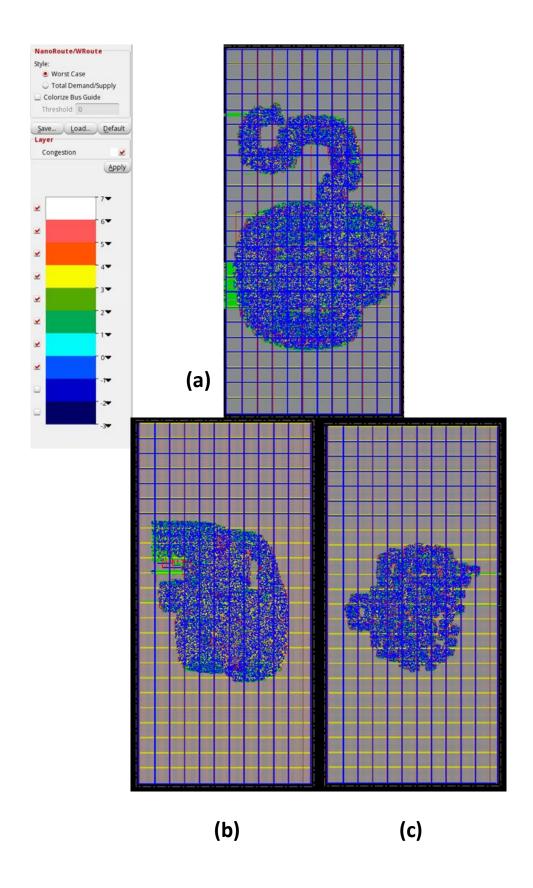

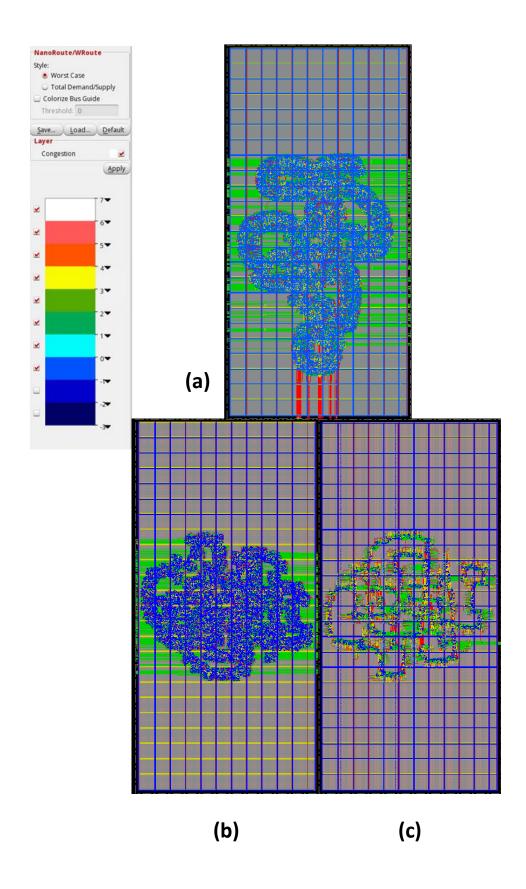

| Figure 46: NCL congestion map.                                 | 63 |

|----------------------------------------------------------------|----|

| Figure 47: MTNCL congestion map.                               | 64 |

| Figure 48: State-dependent leakage data.                       | 67 |

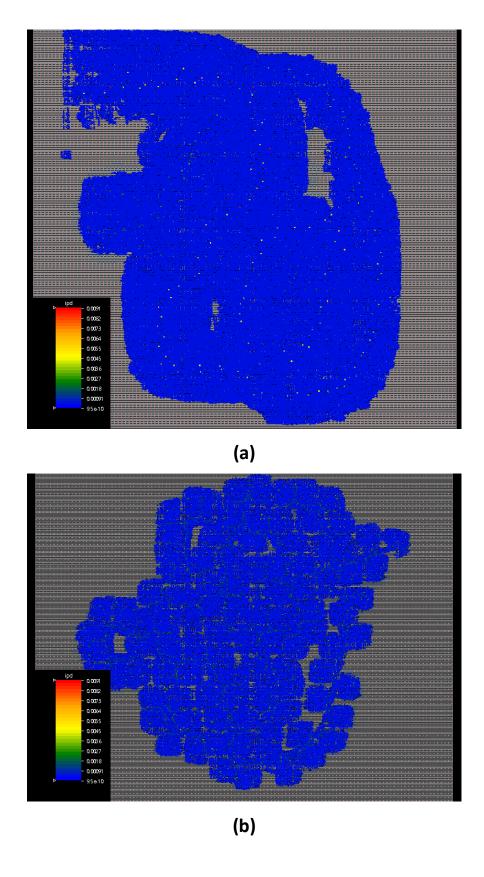

| Figure 49: NCL total power density map: (a) Tier0, (b) Tier1   | 71 |

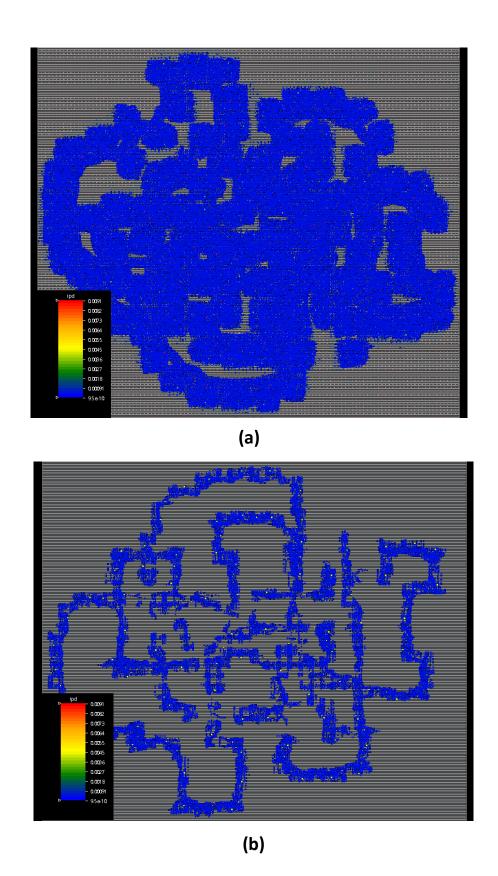

| Figure 50: MTNCL total power density map: (a) Tier0, (b) Tier1 | 72 |

#### 1 Introduction

Digital circuits has gained prominence since the invention of the metal-oxide-semiconductor (MOS) transistor in 1970 [1]. Digital circuits have been applied to many applications including mainframes, smartphones, tablets, wearable devices, and medical devices. The early digital integrated circuits were truly handcrafted full-custom designs involving manually placing, routing, and optimizing transistors [1]. As predicted by Gordon Moore in 1965, the advances in silicon technology have allowed the number of transistors to skyrocket from thousands to billions of transistor on a single chip as shown on Figure 1 [2], [3]. With the advent of very large-scale integration (VLSI), full-custom design became increasingly complex, leading digital designers to automation at higher abstraction. As a result, hardware description languages (HDL) such as VHDL and Verilog [4] and semi-custom design approaches like standard-cell methodology became more appealing and quickly gained prominence among VLSI designers [1], [4]. Using HDL, digital circuit designers could specify the behavior of digital circuits in a precise and formal manner in a textual description enabling technology independent flow that is suitable for code reuse and robust verification [4]. In addition, the standard-cell methodology provided designers with fully verified basic circuits called cells that can be used to develop more complicated ICs. The combination of standard-cell methodology and HDL is widely used in contemporary VLSI design and has been attributed as a key factor in the success of VLSI [5]–[7].

# Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1: Transistor count adapted from [8].

Asynchronous circuits are sequential digital logic circuits that operate without a global clock signal. An asynchronous digital circuit uses local handshaking between components to synchronize, communicate, and operate [9], [10]. According to [9]–[13], asynchronous circuits provide the following benefits: (1) lower dynamic power consumption, (2) potentially faster operating throughput, (3) improved modularity, (4) lower electromagnetic emissions, and (5) higher robustness. In contrast to synchronous circuits, an asynchronous circuit is quiescent when idle and only computes a task whenever a request is received, resulting in lower energy

consumption. Asynchronous design has applications in low power systems since power consumption has become an important consideration in today's electronics industry. The impact of power dissipation has exponentially increased as the size of transistors decrease into nanoscale. This has caused a major paradigm shift where power dissipation has become as important as performance and area. In addition, due to the operating speed depending on the local latencies instead of a global signal, an asynchronous circuit operates in average-case delays rather than worst-case delays. Improved modularity is also inherent because of the reliance on local handshaking rather than a global signal. Since the registers switches at random points of time based on local request, an asynchronous circuit shows lower electromagnetic emissions. Finally, due to the lack of assumptions on inter-cell communication delays, asynchronous circuit has improved tolerance from process, voltage, and temperature (PVT) variations. An asynchronous circuit can also operate correctly in a large variation in power supply.

Despite these advantages, there are several drawbacks of asynchronous circuits including increased area overhead, and circuit and power consumption penalties in some cases [9], [10], [14].

Three-dimensional integrated circuit is a promising technology that could propel the advances of the semiconductor industry and solve the problem of scaling in deep-submicron technologies. It could be the technology that would scale beyond Moore's law. Three-dimensional integrated circuits (3D ICs) consist of multiple layers of logic devices stacked together and connected via vertical interconnects. 3D ICs provide several benefits including shorter interconnect lengths, smaller area, improved interconnect bandwidth, and heterogeneous integration. While 3D IC provides these advantages, it suffers from a critical issue of thermal hotspots[15]. Asynchronous paradigms such as NULL Convention Logic (NCL) and Multi-

threshold NCL could be a potential solution to this thermal hotspot problem [16]. Since NCL and MTNCL lack the global clock signal of synchronous circuits, the power density is more evenly distributed, alleviating the hotspot problem. In addition, the shorter vertical interconnect length could improve the interconnect overhead of NCL and MTNCL designs. Asynchronous circuit designs such as NCL and MTNCL could synergize well with 3D IC technology, creating a more compact low power circuit.

#### 2 Problem Statement

#### 2.1 Dissertation Contributions

- Develop an Asynchronous 3D Tool Flow: The lack of EDA tool support for asynchronous circuits and 3D ICs has made the development of asynchronous 3D ICs especially difficult. This dissertation presents a semi-automated tool flow designed for asynchronous 3D ICs. It incorporates several prominent industry EDA tools as well as in-house scripts and open source programs. It utilizes a modified ASTRAN tool adapted for NULL Convention Logic and Multi-Threshold NCL. ASTRAN is an automated layout generation tool for quick creation of standard cells. It also includes tools for asynchronous 3D IC partitioning using Design Compiler. Physical design and verification of cells utilize industry standard tools such as Cadence Innovus, Voltus, and Mentor Graphics Calibre.

- Develop Asynchronous 3D Standard Libraries (Async3D Library): This dissertation

includes the development of a low-power NCL and MTNCL standard library called Async3D.

As of this writing, Async3D standard-cell library contains over 300 NCL and MTNCL cells.

Several size variations for each cell were developed based on cell drive strength for fined-grained optimizations and low power applications. The library is fully verified with industry standard EDA tools including Mentor Calibre DRC/LVS. In addition, the cells have been

designed to be fully compatible with foundry provided Chartered 130nm synchronous standard cell library called CORELIB\_LP, providing digital circuit designers the possibility of employing over a 1000 different types of cells in hybrid architectures. This is especially useful for synchronous and asynchronous 3D heterogeneous applications.

• Analysis of Asynchronous 3D ICs: This dissertation includes an analysis of asynchronous circuits designed in NCL and MTNCL architecture. The NCL and MTNCL circuits are implemented using the Async3D library while the synchronous counterparts were implemented using the CORELIB\_LP library for comparison. Different circuits were implemented ranging in complexity using the Async3D tool flow. Chip area, wire-length, power consumption, and power density were analyzed for the asynchronous and synchronous designs to study design trade-offs. Circuit performance between designs was normalized to set up a fair comparison.

## 2.2 Dissertation Organization

The chapters are structured to provide the fundamental background information and presents technical analysis towards the end of the dissertation. Finally, the data are analyzed and summarized. Chapter 3 provides the background information on NULL Convention Logic, Multi-Threshold NCL and 3D ICs. Chapter 4 presents the Async3D tool flow and the Async3D library used to implement the NCL and MTNCL designs. Chapter 5 describes the FIR test circuit used to compare the different architectures. Chapter 6 presents the analysis of the NCL, MTNCL, and synchronous designs in terms of area, wire length, power consumption, and power density. Finally, Chapter 7 summarizes the findings and concepts presented on this dissertation and presents future work that could expand the application of asynchronous circuits with 3D IC.

## 3 Background

## 3.1 NULL Convention Logic

NULL Convention Logic (NCL) is a delay-insensitive (DI) asynchronous paradigm that lacks delay requirements and operates correctly as long as the transistors switch properly. NCL circuits utilize a local hand shaking protocol and multi-rail encoding to achieve delay-insensitivity. The most prevalent multi-rail encoding scheme is the dual-rail encoding, which uses two signals to represent four states. As shown on Table 1, the two signals *rail0* and *rail1* determine the current data value of a dual-rail encoding. Data0 is represented when *rail0* is logic 1 and *rail1* as logic 0, and data1 is denoted when *rail0* is logic 0 and *rail1* is logic 1. NULL and INVALID states are represented when both rails are either logic 0 or logic 1, respectively.

Table 1: NULL Convention Logic dual-rail encoding.

|       | DATA0 | DATA1 | NULL | INVALID |

|-------|-------|-------|------|---------|

| Rail0 | 1     | 0     | 0    | 1       |

| Rail1 | 0     | 1     | 0    | 1       |

An NCL circuit is designed using 27 fundamental gates called threshold gates. Table 2 shows all threshold gates and their equivalent logic 1 set functions. These threshold gates were originally proposed by Theseus Logic, Inc. [17]. NCL threshold gates have the following properties: (1) consist of *n* inputs, (2) only becomes asserted when at least *m* of the *n* input become asserted, (3) special function gates are denoted by *D* or *N* refer to resettable gates to either zero or one, and (4) hysteresis property where the output de-asserts only when all the inputs de-assert.

Table 2: NULL Convention Logic fundamental gates.

| NCL Gate | Set Function                |

|----------|-----------------------------|

| TH12     | A+B                         |

| TH22     | AB                          |

| TH13     | A+B+C                       |

| TH23     | AB + AC + BC                |

| TH33     | ABC                         |

| TH23w2   | A + BC                      |

| TH33w2   | AB + AC                     |

| TH14     | A+B+C+D                     |

| TH24     | AB + AC + AD + BC + BD + CD |

| TH34     | ABC + ABD + ACD + BCD       |

| TH44     | ABCD                        |

| TH24w2   | A + BC + BD + CD            |

| TH34w2   | AB + AC + AD + BCD          |

| TH44w2   | ABC + ABD + ACD             |

| TH34w3   | A + BCD                     |

| TH44w3   | AB + AC + AD                |

| TH24w22  | A + B + CD                  |

| TH34w22  | AB + AC + AD + BC + BD      |

| TH44w22  | AB + ACD + BCD              |

| TH54w22  | ABC + ABD                   |

| TH34w32  | A + BC + BD                 |

| TH54w32  | AB + ACD                    |

| TH44w322 | AB + AC + AD + BC           |

| TH54w322 | AB + AC + BCD               |

| THxor0   | AB + CD                     |

| THand0   | AB + BC + AD                |

| TH24comp | AC + BC + AD + BD           |

By utilizing *m*-of-*n* threshold gates, the design complexity of NCL circuits is significantly improved. NCL gates use the following naming convention of TH*mn* gates, where *m* represents the threshold requirement and *n* represents the number of inputs pins of the gate. Each gate transitions to a logic 1 value only if a certain *threshold* of input pins transitions to a logic 1. The output of the gate will be logic 1 when any *m* inputs pins have switched to logic 1 and can be set low only when all inputs are logic 0. Using this convention, a C-element can be interpreted as *n*-of-*n* threshold gate with hysteresis. Hysteresis is a special property of NCL gates.

Once the output of an NCL gate is logic 1, it remains high until all the inputs are logic 0. An example gate is a TH34 gate shown on Figure 2a and a TH34w2 gate shown on Figure 2b.

Figure 2: THmn NCL gates: (a) TH34, (b) TH34w2.

In addition to the threshold and hysteresis characteristics, NCL gates also utilize input weights. Weighted threshold gates are a variation of the basic threshold gates and are denoted by THmnWw<sub>1</sub>w<sub>2</sub>...w<sub>R</sub> where  $1 < w_R \le m$ . The values of  $w_{1,w_2,...w_R}$  indicate the weights of the input pins in order starting from input A. The weight of input A is indicated by w1, w2 denotes the weight of input B, etc. For example, a weighted threshold gate is shown on Figure 2b and has the following naming convention of TH34w2. A TH34w2 gate has 4 inputs and has a value threshold of 3 with a weighted input A having a weight of 2. Since input A has a weight of 2, TH34w2 could be set to logic 1 with input A as logic 1 and another input pin set to logic 1. The weights of input pins B, C, and D are not indicated on the naming convention because they have a weight of 1. Another variation are gates that have resettable functionally [18]. Resettable gates are often included to initialize the state of the gate. A reset input pin in added into the gate and can set the output of the gate to either logic 1 or logic 0. Resettable gates have an added notation of N or D, where having the N notation indicates a resettable gate to logic 0, and having a D notation indicates a resettable gate to logic 0. Resettable gates are used in designing shift registers in an NCL circuit.

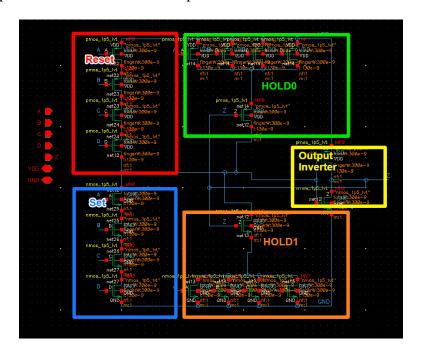

Figure 3: NCL threshold gate implementation using CMOS technology.

NCL threshold gates could be implemented using CMOS technology. A generic threshold gate consists of 5 components: set, reset, hold0, hold1, and an output inverter as shown on Figure 3. The set component controls how the gate will be asserted to logic 0 and corresponds to the set functions described on Table 2, while the reset component controls how the gate will be deasserted. The hold1 component is a complement of set component, while the hold1 component is a complement of the reset component.

#### 3.1.1 NULL Convention Logic Pipeline

The micro-pipeline framework for NCL is shown on Figure 4. The NCL pipeline follows DATA-NULL cycles in which DATA inputs are always followed by a NULL spacer. In a DATA cycle, the values in the gates are set by sending data inputs to the gates. The DATA cycle must then be followed by a NULL cycle where the inputs are all set to logic 0 to reset the gates to a NULL state. The NULL cycle acts as a boundary to prevent the current DATA cycle from being overwritten by the next DATA cycle. An NCL pipeline consist of several NCL combinational logic blocks separated by NCL registers. An NCL pipeline is similar to a synchronous pipeline architecture in that they both use registers between combinational blocks. However, special

registers are used for the NCL architecture. An NCL single-bit dual-rail register is shown on Figure 5.

Figure 4: NCL micro-pipeline architecture [19].

Figure 5: NCL single-bit dual-rail register [20].

These special registers are used to maintain delay-insensitivity and performs handshaking during sequential operations. An NCL register consist of resettable and inverting NCL gates. In the NCL pipeline architecture, one pipeline stage consists of an NCL combination block between two NCL registers. The registers between pipeline stages interact via ki and ko signals. NCL registers sends ki signal as input and ko signal as output. The ki represents the request signal and the ko represents the acknowledge signal. When a register's ki signal is logic 0, only DATA is allowed to pass. On the other hand, when the register's ki signal is logic 1, only NULL is allowed to pass. The acknowledge signal ko can represents a Request for NULL (rfn) via logic 0 and a Request for DATA (rfd) via logic 1. In addition to registers, the NCL architecture also utilizes a special component block called completion detection. The completion detection

consists of a tree of C-elements and is used for data validation. A completion detection is required when multiple single registers are combined to form an *n*-bit register.

There are two important requirements when designing an NCL requirement: input-completeness [21] and observability [22]. Input-completeness requires that all outputs of the combinational blocks do not transition until all the inputs arrive. Observability requires that no orphans may propagate through a gate [23]. An orphan is defined as a wire that transitions during the current DATA cycle but is not used to determine the output. The observability condition ensures that every gate that transitions is necessary to transition at least one of the outputs.

Compared to a synchronous circuit design, an asynchronous circuit paradigm such as NCL provides several advantages. Past scientific research has demonstrated that NCL circuit has the potential to have a wide-range of applications and benefits as described by the following:

- NCL circuits show resilience when considering performance-energy tradeoffs [24].

- Energy and performance advantages have been demonstrated in normal and nearthreshold voltage regions [25].

- NCL circuits have shown promising application in hardware security [26], [27].

- NCL circuits have exhibited lower electromagnetic interference [11], and immunity to meta-stable behavior [28].

- The resilience of NCL circuits have been validated in a wide range of process, voltage, and temperature variations [29], [30].

## 3.2 Multi-threshold NULL Convention Logic (MTNCL)

The advantages of NCL circuits could be improved by utilizing power gating into the NCL gates, creating a new logic paradigm called Multi-Threshold NCL (MTNCL). MTNCL is an optimized low power asynchronous paradigm that achieves better performance-energy tradeoff

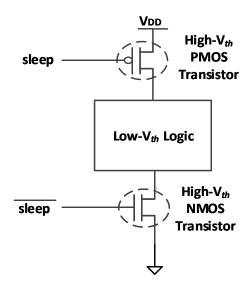

when compared to NCL. This is achieved by reducing static power during quiescent NULL states while maintaining high performance during DATA propagation. The static power consumption is reduced by implementing sleep-able MTNCL gates during NULL states. Multithreshold technology is commonly used in synchronous designs for power-gating mechanism by utilizing several transistors with varying threshold voltages (V<sub>th</sub>). Figure 6 shows a typical power-gating structure for CMOS technology. The threshold voltage of a field-effect transistor (FET) is the minimum gate-to-source voltage potential that is required to create a conducting path between the source and drain terminals. The threshold voltage depends on the choice of the oxide and on oxide thickness. Low-V<sub>th</sub> transistors are faster but have higher subthreshold leakage current running through the device, while high-V<sub>th</sub> transistors are slower but have less leakage current [31].

Figure 6: Multi-threshold CMOS power gating structure.

MTNCL gates have reduced leakage current during idle states while also maintaining performance while processing data [32]. High- $V_{th}$  transistors are used to reduce subthreshold leakage during idle states, while low- $V_{th}$  transistors are used to maintain performance while processing data. The high- $V_{th}$  transistors are controlled by the *sleep* signal. When the *sleep* signal

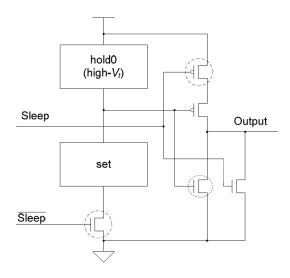

is logic 0, the MTNCL gate is in active mode and the gate functions normally. When the sleep signal is logic 1, the MTNCL gate is in sleep mode and the output low- $V_{th}$  transistor is turned on to set the output of the MTNCL gate to logic 0, while the high- $V_{th}$  transistors are turned off to reduce subthreshold leakage. A more fined grained MTNCL power gating structure shown on Figure 7 have been proposed to eliminate the output wake-up glitch and provide several improvements.

Figure 7 Fined Grained MTNCL power gating structure [33].

The sleep mode and active mode of an MTNCL gate is based on the NCL DATA-NULL cycles. The sleep mode of an MTNCL circuit is equivalent to the NULL cycle while the active mode is equivalent to the DATA cycle. As shown on Figure 7 of the improved MTNCL gate power gating structure, the reset block and its corresponding complement hold1 block has been removed from the NCL gate structure because the sleep mode can generate a NULL cycle. With these changes, MTCNL gates have fewer transistors than NCL gates. In addition, the input-completeness and observability requirements from NCL circuit design can be eliminated. The hysteresis property of NCL gates is also only required by a small subset of MTNCL gates [26].

## 3.2.1 Multi-Threshold NCL Pipeline

The MTNCL pipelining framework is very similar to the NCL counterpart. A pipeline stage consists of a combination logic block with two sets of MTNCL registers. Figure 8 shows the MTNCL pipeline architecture.

Figure 8: Multi-threshold NCL pipeline architecture.

The MTNCL registers are now sleep-able and are used to generate a NULL cycle. When the MTNCL combinational logic are set to sleep mode, the outputs of the gates are set to logic 0. This is equivalent to a NULL state. The completion detection has also been modified and improved by utilizing early completion [34]. Early completion detection, shown on Figure 9, is used to improve the throughput of the pipeline while maintaining delay-insensitivity. It is also used to ensure that all the outputs of a pipeline stage are NULL before allowing the DATA cycle to pass.

The corresponding request and acknowledge signals ki and ko are still required for the handshaking protocol, but they are also used to control the sleep signal. The output of the completion logic ko signal is used to sleep the MTNCL registers, completion logic, and the combination block of the next stage in the pipeline.

Figure 9 Early completion detection block in MTNCL pipeline.

After the first DATA cycle, the output *ko* signal of the completion logic will be logic 0 which represents a Request for NULL. This *ko* signal activates the active mode for the next stage in the pipeline and allows the combination logic to propagate the input data. This *ko* signal remains de-asserted until a NULL cycle is detected on the input ports and the completion logic is forced to sleep. When the output of the completion logic is logic 1, representing a Request for DATA, it also activates sleep mode for the next stage of the pipeline, propagating the NULL cycle. The DATA-NULL cycle propagation continues until a valid data is present on the output port.

There are several major differences between NCL and MTNCL and they can be summarized by the following: (1) sleep signal controls the local handshaking between pipeline stages in MTNCL pipeline, (2) MTNCL have lower leakage power consumption due to power gating (3) MTNCL gates forego the NCL hysteresis property.

#### 3.3 Three Dimensional Integrated Circuits

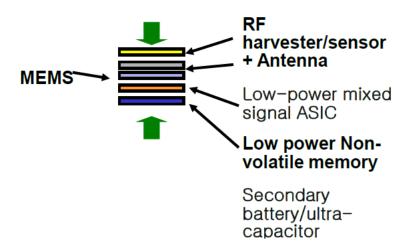

Three-dimensional integrated circuit (3D IC) is a circuit manufactured by 3D stacking multiple silicon wafers/die into one device. The main enabler of such technology is the throughsilicon via (TSV) that enables vertical interconnects between the different layers. 3D ICs with TSVs offer new levels of efficiency, power, performance, and form-factor advantages to the semiconductor industry. As an emerging technology, 3D IC promises to leap forward the Semiconductor Industry beyond the challenges of Moore's law. As demand for increasing density, higher bandwidths, and lower power intensifies, 3D IC integration provides a potential solution to these problems by packing in a great deal of functionality in a small form factor. 3D IC also provides designers with the freedom to create multiple heterogeneous die on the same circuit. Circuits as logic, memory, analog, RF, and micro-electrical mechanical systems (MEMS) could be integrated into one 3D IC with different process nodes suitable for each component. For example, a 3D IC could harness the cutting-edge advantages of a 28nm process node for highspeed logic while using legacy 130nm process node for analog components. Heterogeneous integration could alleviate cost associated with node migration, and allow designers to take advantage of existing legacy nodes.

The impact of 3D IC is very broad. Applications of 3D IC are prominent in areas such as networking, graphics, mobile communications, and computing. Considering of the current trends where mobile devices are pervasive, 3D IC could cause a significant paradigm shift to the way ICs are manufactured. One area where 3D IC could be a potential alternative is System-on-Chip (SoC). SoC in the modern world has allowed the advent of "smart" devices where different components are integrated as one unit to save floor space, power, and increase bandwidth. 3D IC allows the same integration in an even smaller area, lower power, and faster bandwidth. The

most exciting and more useful advantage of 3D IC over conventional 2D process is the reduction in the interconnect length between components. Such reduction will be most advantages in circuits such as microprocessors, memory, and Field Programmable Gate Arrays (FPGA).

#### 3.3.1 Motivation

There are several advantages 3D ICs have over traditional 2D circuits. The advantages could be summarized by the following:

- Shorter interconnect length

- Increased interconnect bandwidth

- Heterogeneous Integration

- Smaller form factor

Due to the closer integration of components, the bandwidth could be significantly improved.

3D ICs are ideal for compact mobile devices due to the space saving on the board. In addition, there is potential for power reduction on 3D ICs due to the reduction in resistance-inductance-capacitance (RLC) on the interconnect between devices. The interconnects between components are reduced and can improve the overall performance of chip. 3D IC provides the ability to create modularize components in different process nodes through heterogeneous integration.

When compared to other technologies such as SoC/System-in-Package (SiP), 3D IC offers improved level of integration on a smaller form factor. Figure 10 shows the industry trend of integration from traditional systems to SoC, and finally to 3D IC in the future.

Figure 10: Trend leading towards 3D IC technology [35].

3D IC provides significant improvements over the traditional model, but there are additional challenges that must be solved. These challenges include thermal issues, timing, and power management concerns.

#### **3.3.1.1** Shorter interconnect

The most valuable advantage of 3D IC is the reduction of interconnects. This is because as technology scaled down, wire has not scaled along with it. Two factors contribute to the delay of the overall IC, i.e., the switching speed and propagation delay. Unfortunately, narrower wire only results in increased resistance, while smaller pitches increase capacitance. Due to this fact, as technology advances to the sub-micron level, the RC delay has become the dominant factor over the switching delay. The active power (switching) consumption in microprocessor interconnect contribute greater than 50% of the overall power [36]. In addition, over 90% of the interconnect power is consumed by only 10% of the wires. In memory applications, an 8GB four-stack 3D DDR3 DRAM using TSVs can reduce standby power by 50% and active power by 25%. Another example is in microprocessors with a 3D implementation of the Pentium 4 gaining 15% performance improvement while simultaneously lowering power consumption by 15% at the cost of only 14°C rise in temperature. Figure 11 is a diagram showing the advantage of the TSV vertical interconnects over the traditional 2D wire interconnect.

Figure 11: 2D versus 3D interconnect [36].

## 3.3.1.2 Wiring Delay

Shorter interconnects come with several improvements over the overall circuit. The speed of devices is improved and capacitance on the wire is reduced. Furthermore, this reduction in wire length reduces power consumption because less power is required to drive the wire. Figure 12 shows the comparison of the relative delays between interconnects and gate delays. The graph shows that as the feature size becomes smaller from 250nm to 32nm, the global interconnect dominates the delay, especially if repeaters are not used. The relative difference between the global interconnect versus the gate delay is in the order of several magnitudes.

Figure 12: Global interconnect trends [36].

## 3.3.1.3 Memory Bandwidth

The memory bandwidth demands on computing systems are rapidly growing. The trend in mobile devices is the same, requiring 50 Gbps and higher. Graphics and networking can easily benefit from 1Tbps, as well as data-driven workloads requiring cross-system bandwidth. 3D IC can provide high memory bandwidth at better power efficiencies than conventional packaging.

## 3.3.1.4 Bandwidth density

3D IC integration includes vertical vias to connect the different layers, allowing the construction of wide-bandwidth buses between different functional blocks. The typical application of a stack layer is the integration of a processors and a memory on a 3D stack. This arrangement could potentially solve the memory wall problem. The memory wall or the bandwidth gap is a known issue in industry. Due to the dramatic difference between the processing speed of the processor and the memory, the memory has been the bottleneck in terms

of performance. Figure 13 shows the potential bandwidth between different technologies with 3D IC showing the highest potential, reaching 1 Tbps/mm<sup>2</sup>.

| Technology            | Approximate limit         |

|-----------------------|---------------------------|

| High density laminate | ~ 50 Gbps/mm              |

| Silicon interposer    | ~ 150 Gbps/mm             |

| 3DIC - microbumps     | > 10 Tbps/mm <sup>2</sup> |

| 3DIC - TSV            | > 1 Tbps/mm <sup>2</sup>  |

Figure 13: 3D IC bandwidth potential [37].

## 3.3.1.5 Heterogeneous Integration

Heterogeneous integration allows a single silicon die to include an incredible amount of functionality by including processors, digital logic, memory, and analog components.

Furthermore, 3D IC integration has an advantage over traditional SoCs by utilizing different process nodes. Traditionally, analog and RF designs in advanced process nodes are challenging and could potentially require significant amount of time to develop and test. This is further exasperated by different process variabilities. Compared to the traditional implementation, 3D IC could integrate different functional layers based on optimized process nodes. For example, a digital logic in an advanced node (e.g., 22 nm) could be placed on top of analog circuits in a legacy node (e.g., 180 nm).

## 3.3.1.6 Small Form Factor

Due to the 3D stacking, 3D ICs are compact and can be designated to have multiple layers. An example of a 3D stacked device consisting of different types of components is shown in Figure 14. The circuit consist RF sensors/harvester, low-power ASIC, memory, and analog devices. TSVs provide the vertical interconnect between these layers.

Figure 14: Small form factor consisting of different layers [38].

#### 3.4 TSV Process Flow

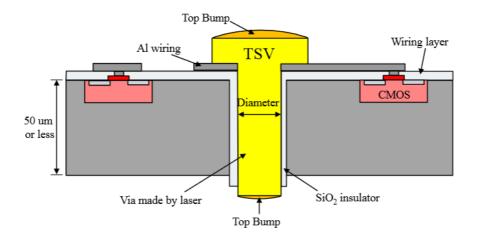

TSV has been the main enabler of 3D IC integration. TSVs are electrically conducting electrical connections that allow multiple layers on a chip to communicate. TSVs are copper vias with diameters that may range from 1 to 30 microns. Figure 15 shows the cross-section of a 3D die with TSV.

Figure 15: 3D cross-section of a TSV [39].

First step in the TSV creation is the etching process to create an etched hole where a TSV will be placed. The etching process is done through deep reactive-ion etching. In addition, sidewall passivation is performed where an insulation layer is created around the etched region to separate

the TSV from the bulk. TSV filling is accomplished by a vapor deposition process. The conductive fill is typically copper or tungsten. Afterwards, wafer thinning is done by grinding and chemical mechanical planarization (CMP). Finally, alignment is one of the last critical steps before permanent bonding occurs.

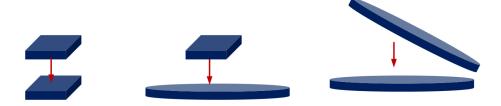

After the creation of each layer, the 3D stacked using three possible configurations: face-to-face, face-to-back, and back-to-back. Different configurations are possible in single devices, especially when more than two dies are stacked.

## 3.4.1 Manufacturing technologies for 3D IC

There are three possible integration methods for 3D ICs: wafer-to-wafer (W2W), die-to-wafer (D2W), or die-to-die (D2D). W2W involves directly bonding the wafer stacks together and then dicing them into individual die stacks. This bonding process is associated with the highest throughput, but requires the different layers to have the same form factor. Due to this requirement, W2W is more suitable for homogeneous integration, e.g., 3D stacked memory. In addition, W2W could suffer from significant yield loss due to the stacking of good and bad die. In comparison, D2W and D2D hope to resolve these issues by dicing the bare die from the wafer and then stacking them on die/wafers. These bonding strategies could achieve higher stack yield by only bonding known good die. Figure 16 shows the three types of bonding process.

Figure 16: Manufacturing 3D ICs [35].

## 3.5 Challenges

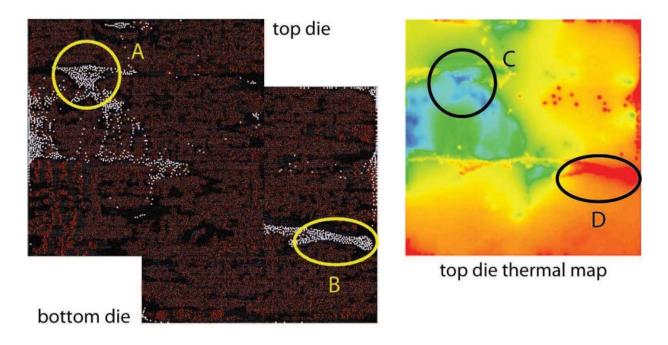

When compared to the logic gates and other circuit features, the TSV is very large and requires careful consideration on placement and usage. Excessive use of TSVs could be detrimental and result in increased wire length. Due to coupling, TSVs also require keep-out zones, reducing mechanical stress placed on nearby devices. This in turn causes thermal hot spots; therefore, careful floor planning is necessary to find optimal TSV placements on the die. Thermal issues and mechanical stress could affect the performance of the device. Figure 17 shows the thermal hotspots of a 3D IC denoted in bright red. In addition, die stack order is important as the middle stack is more susceptible to thermal problems due to the reduce access to cooling. The bottom stack is generally closest to the cooling system and so the most thermally sensitive die is best placed at the bottom. The densely packed stack is also prone to generate a lot of heat. There are several solutions to the thermal issues. Air-cooling is possible but it requires active power management. Another potential solution is liquid cooling. Another viable solution is to evenly distribute the power density throughout the chip to prevent the hotspot problem. Previous research has explored the application of NCL circuits with 3D IC as a potential solution to the thermal hotspot issue [40]. Figure 18 shows the comparison between synchronous and NCL circuits in terms of thermal map distribution. The NCL circuit showed a more evenly distributed thermal map than the synchronous counterpart.

Figure 17: 3D IC thermal map [41].

Figure 18: Synchronous vs NCL thermal distribution [40].

3D IC also comes with increased design complexity. Especially with heterogeneous integration, the 3D stack could combine digital and analog/RF circuitry, requiring tools with strong analog/mixed-signal capabilities. In addition, the manufacturing process demands the expertise in several domains from 3D manufacturing to 3D IC packing, requiring close collaboration and co-design between groups in the whole design chain.

Testing 3D ICs is a challenge due to the tight integration between active layers in the 3D stack. A significant amount of interconnect is associated between each layer for communication. Conventional testing methods do not account for the overhead associated with TSVs as well as the different modules on the stack. To achieve high yield rates and reduce cost, each die must be tested independently. One of the challenges in testing 3D IC is gaining access to the die inside the 3D stack. 3D IC testing included two levels, wafer test and package test. Wafer test involves testing each silicon die while package test involves testing after assembling the die into a package. Compared to the traditional testing method, 3D IC includes many more intermediate steps due to the die stacking and TSV bonding process. Wafer test is critical in cost reduction as it reduces the chance of a bad die being used in a package. A failed check could result in a failed package-level test.

#### 3.6 Discussion

3D IC has shown significant improvements over the traditional paradigm of 2D counterpart. 3D IC integration offers improvements in power consumption, form factor, and performance. It also allows heterogeneous integration by incorporating different process nodes. While the advent of 3D IC integration has yet to be realized, it has shown potential in revolutionizing the way circuits will be design in the future. The application of 3D IC includes networking, graphics, mobile communications, and computing. However, the shift to 3D IC integration comes with several challenges. First, a 3D IC must be designed from the initial planning process to take full advantage of the 3D process. In addition, the associated cost in manufacturing 3D ICs must be reduced to encourage widespread use. Furthermore, thermal issue remains a concern and must be carefully evaluated. Testing 3D IC is another hot research topic.

# 4 Asynchronous 3D Tool Flow

# 4.1 Proposed Flow

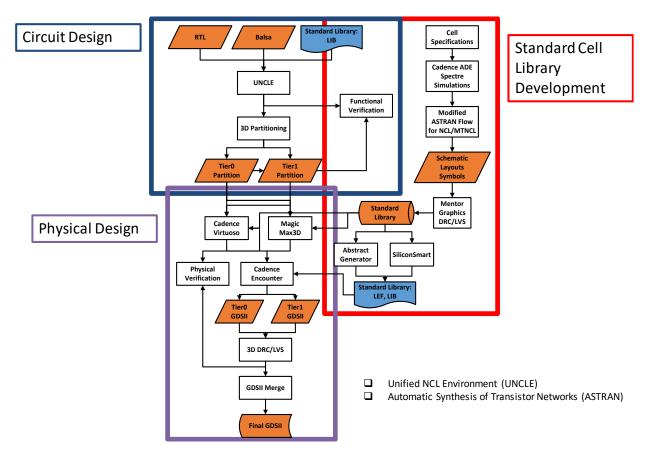

This chapter presents the Async3D tool flow that was developed and used for this dissertation work. The proposed flow is shown on Figure 19. It consists of three main components: circuit design, physical design, and standard cell library development. The bottom and top layers of the 3D stack are called Tier0 and Tier1 in the tool flow.

Figure 19: Async3D tool flow.

### 4.2 Circuit Design

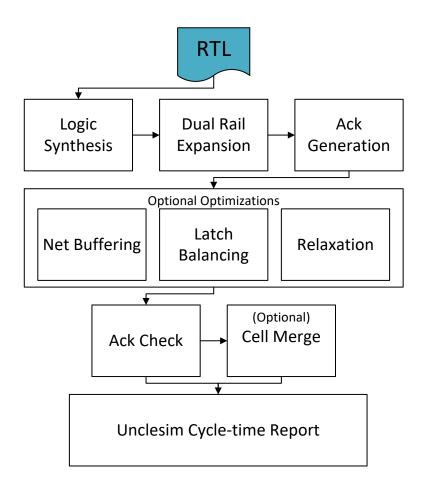

#### **4.2.1** Unified NCL Environment (UNCLE)

The Unified NCL Environment (UNCLE) is a toolset developed for the synthesis of dual-rail NCL designs from a Verilog RTL specification [42]. The tool supports two NCL based system implementations: data-driven approach and control driven approach. The data-driven approach utilizes NCL gates for registers while the control driven approach uses Balsa style registers and control. UNCLE features several optimizations including net buffering, latch balancing, relaxation, and cell merging. In addition, UNCLE allows logic synthesis via commercial toolset such as Synopsys Design Compiler, and can automatically generate the dual-rail expansion and acknowledge pipelines. Figure 20 shows the full UNCLE tool flow.

Figure 20: Uncle tool flow overview [43].

UNCLE provides full support for NCL designs. As of this writing, the latest version 0.2.6 can generate a netlist from an NCL design with some limited support for MTNCL designs.

# 4.2.2 3D IC Partitioning

After the synthesis, the netlist must be partitioned to create the top and bottom netlist.

Synopsys Design Compiler was used for the 3D IC partitioning phase of the tool flow. Previous work has proposed a set of scripts for 3D IC partitioning for NCL and MTNCL circuits [44].

Their approach used python scripts to parse through the netlist and create TSV components between the partitioned netlist. While this automated the 3D partitioning, the partitioning scripts became hard to maintain and produced netlist that were very difficult to debug and verify. One of

the issue with the 3D IC partitioning phase is that the post-synthesis netlist is often flattened, removing all hierarchies. Partitioning this manually would be error prone and laborious. The Async3D flow leverages existing industry tools to partition the netlist. It takes advantage of the naming convention used in the flattened netlist. By using regular expressions in conjunction with the group and ungroup feature of Design Compiler, the design structure could be restored and the 3D netlist for the top and bottom tiers can be created in a more convenient manner. In addition, this method has the benefit of easier debugging.

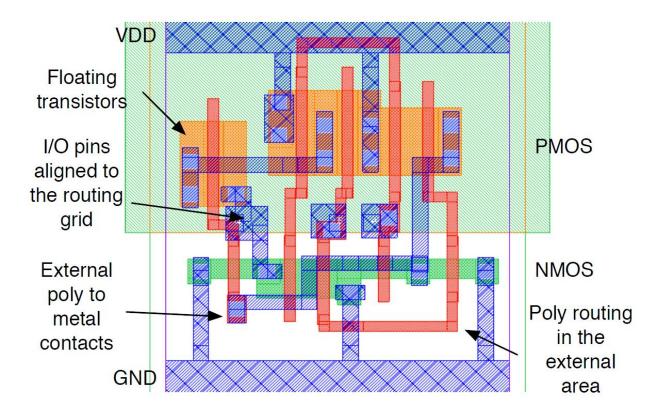

### **4.2.3** Automatic Synthesis of Transistor Networks (ASTRAN)

The Async3D tool flow utilizes an automated layout generation tool to generate the cell libraries. Automatic Synthesis of Transistor Networks (ASTRAN) is an open-source tool used for physical synthesis [45]. ASTRAN can generate the layouts of CMOS cells using a transistor-level netlist specification. The cell netlist must follow the SPICE format. The area overhead of ASTRAN versus an optimized hand-made layout is around 3.7% on average. ASTRAN provides several features including transistor sizing, floorplanning, cell placement, and routing. The layout tool also includes several optimizations such as transistor folding, intracell routing, and 2-D layout compaction. The layouts can be exported in CIF, GDSII, and LEF formats. These formats can then be imported to Cadence Virtuoso for viewing or further optimizations. The version used in this dissertation has been modified to support the cell dimensions and specifications described on the Async3D library section. In addition, the code has been improved to support multi-threshold transistors used for MTNCL. Figure 21 shows an example of an ASTRAN style layout. The project is active with plans to support 45nm process and beyond.

Figure 21: ASTRAN layout style [45].

# 4.3 Physical Design

The main tool used for physical design phase was Cadence Innovus. The latest version of Innovus has included some features for 3D IC design. After Tier0 and Tier1 are placed and routed, the GDSII are extracted. This post-layout file can then be imported back to Cadence Virtuoso for verification or merged to create final GDSII. For the Async3D flow, a 3D DRC and LVS are included the foundry kit for verification. The 3D DRC and LVS utilizes Mentor Calibre for post-layout verification. After post-layout verification, the two files are merged using a tool provided in the foundry kit to create the final GDSII combining Tier0 and Tier1.

#### 4.4 Standard Library Flow

This section presents the Async3D standard library. The standard library could be divided into three main parts: cell library specification, cell creation, and cell verification. The standard library tool flow is shown on Figure 22.

Figure 22: Async3D standard library tool flow.

#### 4.4.1 Tezzaron 3D Design Kit

The 3D process design kit used for this dissertation is the Tezzaron 3D design kit. It supports a 2-layer stacked device based on the Chartered 130nm Low Power process. The 2-layer devices are stacked top of each other to create a 3D stack. There is an option to create a 2-layer stack as well as an additional 3rd layer for the use of a memory module. This dissertation work uses the 2-layer stack configuration.

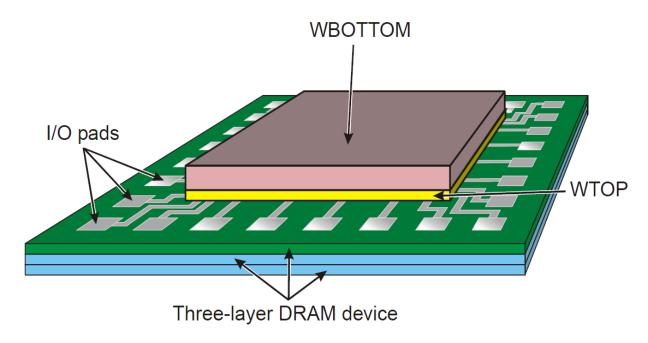

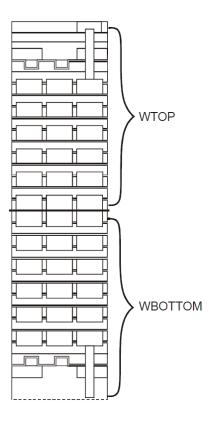

Figure 23: Tezzaron 3D stack layer [46].

The 2-layer logic stacks are connected in a face-to-face (wafer-to-wafer) configuration via Cu-to-Cu thermocompression process. The two logic die on Figure 23 are aptly named WBOTTOM and WTOP. A vertical cross-section of the 3D stack is shown on Figure 24. WTOP will be thinned to expose the TSV that will be connected to the memory. The number of metals used is 6 metal layers, with Metal 6 being used as a layer for the micro-bumps.

Figure 24: Two-wafer logic stack [46].

The maximum TSV spacing is 1000 microns and the minimum spacing is 100 microns. Higher TSV density is recommended for 3D stacks that have more layers to allow more surface for bonding. The diameter of the micro-bumps is 1.2 microns with a depth of 6 microns. The parasitic capacitance between the face-to-face interconnects is negligible, and is essentially the same as the top metal layer.

The Chartered 130nm process consists of 1.5V and 3.3V transistors. This dissertation work uses the 1.5V transistors. In addition, low- $V_{th}$  and normal- $V_{th}$  transistors are used to implement the multi-threshold gate configurations.

# 4.4.1.1 NCL vs MTNCL Naming Convention

The naming convention follows THmnWw1w2...wR where:

• TH - stands for threshold

- *m* denotes that at least *m* of the *n* inputs must be asserted before the output will become asserted

- n number of inputs

- W means the inputs are weighted

- w1 weight of input1

- *w*2 weight of input2

- wR weight of inputR

For this dissertation, lowercase naming was used to resolve an issue with case-sensitivity in the VHDL and Verilog netlist. MTNCL cell names are derived from NCL cell names. Adding "\_m" suffix denotes that the gate is an MTNCL gate. For example, TH12 becomes TH12m.

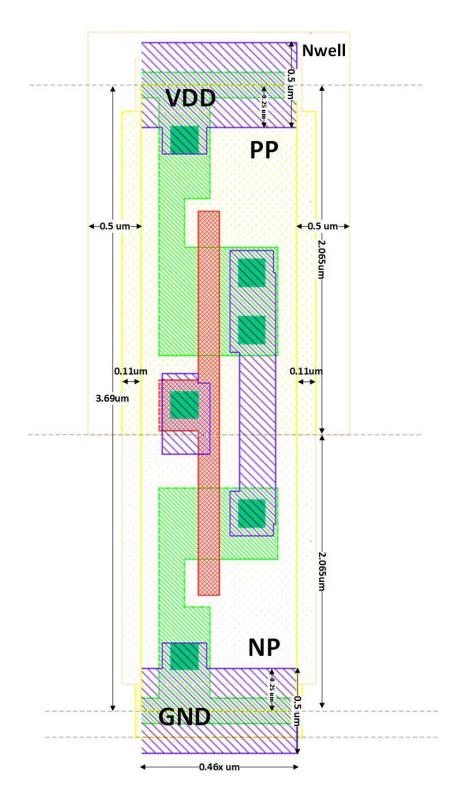

#### 4.4.1.2 Cell Layout Dimensions

The cell layout dimensions were determined based on the foundry provided synchronous library. This was done such that the synchronous and asynchronous libraries are fully compatible. In addition, all cells can be abutted side by side, reducing total chip area. The cell layout requirements are shown on Figure 25. The cell layout dimensions are specified by the following rules:

- Height multiple of horizontal pitch: Height =  $0.41 \times$

- Width multiple of vertical pitch: Width =  $0.46 \times$

Pitch is defined as the distance from center to center of a layer. This dimension is important because it is used to determine the routing grid. On-grid pin placements reduce computation resource requirements during place and route. The cell height dimension is 3.69µm and is a multiple of the horizontal pitch. The cell width can vary as long as it is a multiple of the vertical pitch. The cell sizes are calculated from VDD and GND metal pitch. The power rails have a

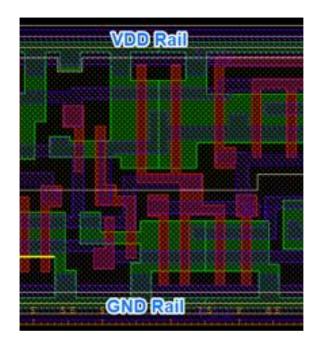

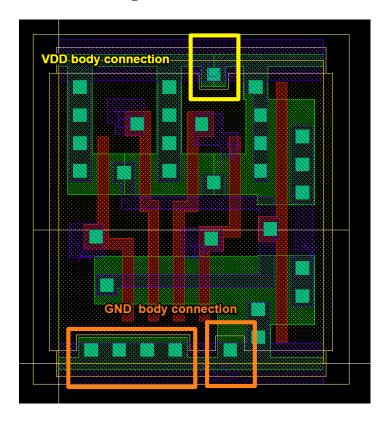

fixed height of 500nm. The VDD and GND are placed on top and bottom of the cells. Figure 26 shows an example of the VDD and GND rails. In addition, Figure 27 shows a layout example for the bulk body contacts.

Figure 25: Async3D layout template.

Figure 26: Power rails.

Figure 27: Bulk body contacts.

### 4.4.1.3 Cell Specification

Cadence Spectre was used to simulate the cells. The transistor gate sizes are shown on Table 3 and the library timing parameters are shown on Table 4. A load capacitance of 500 fF was used to characterize the cells for cell sizing. The variables represent the following: value of *riseTimeIZ* and *riseTimeZ* are the time required for *IZ* and *Z* nets to rise from 10% to 90% of VDD, while the value of *fallTimeIZ* and fallTimeZ is time required for *IZ* and Z net to fall from 90% of VDD. The net *IZ* represents the internal net driving the output inverter while net Z is the output of the inverter. These values are used to calculate the linearized load. The variables *riseKLoad* and *fallKload* represent the linearized load factor using rise and fall times. It is one of the metrics used to determine the drive strength of the cells. This value is based on the load capacitance, *riseTimeZ*, and *fallTimeZ*. This is derived from the CORELIB\_LVT specification document. It is calculated using Equation 1. These metrics are matched to create well-balanced and power efficient cells.

**Equation 1: Linearized load factor.**

(a) riseKload =

$$\frac{riseTime}{2LoadCapacitance}$$

(b) fallKload =

$$\frac{fallTime}{2LoadCapacitance}$$

**Table 3: Gate Transistor Sizing**

| Transistor Size | PMOS Size (um) | NMOS Size (um) |

|-----------------|----------------|----------------|

| XL              | 0.3            | 0.16           |

| X1              | 0.64           | 0.25           |

| X2              | 1.28           | 0.5            |

| X4              | 2.29           | 1              |

| X6              | 3.84           | 1.5            |

| X8              | 4.68           | 2              |

Table 4: Async3D library timing specifications.

| <b>Gate Size</b> | riseTimeIZ (ns)    | fallTimeIZ (ns)    | riseTimeZ (ns) | fallTimeZ (ns) | riseKLoad (ns/pf) | fallKLoad (ns/pf) |

|------------------|--------------------|--------------------|----------------|----------------|-------------------|-------------------|

| XL               | Less than 0.100 ns | Less than 0.100 ns | 10 – 10.3      | 10 – 10.3      | 10 – 10.3         | 10 – 10.3         |

| X1               | Less than 0.100 ns | Less than 0.100 ns | 4.8 - 5.2      | 4.8 - 5.2      | 4.8 - 5.2         | 4.8 - 5.2         |

| X2               | Less than 0.100 ns | Less than 0.100 ns | 2.3 - 2.5      | 2.3 - 2.5      | 2.3 - 2.5         | 2.3 - 2.5         |

| X4               | Less than 0.100 ns | Less than 0.100 ns | 1.2 - 1.4      | 1.2 – 1.4      | 1.2 – 1.4         | 1.2 – 1.4         |

| X6               | Less than 0.100 ns | Less than 0.100 ns | 0.76 - 0.79    | 0.76 - 0.79    | 0.76 - 0.79       | 0.76 - 0.79       |

| X8               | Less than 0.100 ns | Less than 0.100 ns | 0.61 - 0.63    | 0.61 - 0.63    | 0.61 - 0.63       | 0.61 - 0.63       |

#### 4.4.2 Cell Schematics

Figure 28 shows an annotated schematic from a TH44 gate. The schematic transistors are broken down to set, reset, hold1, hold0, and output inverter. This schematic follows the NCL threshold gate specification discussed in Chapter 3.

Figure 28: Annotated TH44 schematic implementation.

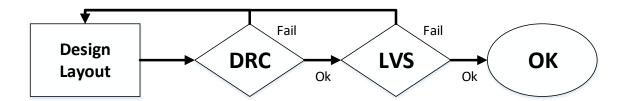

#### 4.4.3 Cell Verification

Mentor Graphics Calibre was used for cell verification. The cell verification flow is shown on Figure 29. The verification phase includes design rule check (DRC), layout versus schematics (LVS), and parasitic extraction (PEX). DRC is the process that determines whether

the generated layouts meet the recommended physical design rules. This is a major step of the cell verification phase. Any problems in this step must be resolved before moving on to LVS. After a successful DRC, LVS must be passed. LVS is the phase where the verification tool determines whether the cell layout matches the schematic diagram. The final step is parasitic extraction where the parasitic effects are calculated from the devices and wire interconnects. This creates an accurate model of the circuit with signal delays, and it is used to generate the liberty characterization file.

Figure 29: Cell verification flow.

#### 4.5 Async3D Library Cell Area

Table 5-7 shows a full list of the completed Async3D NCL and MTNCL libraries. As of this writing, the library contains 6 different sizes ranging from the low power cells such as THmn\_XL and large drive strength cells such as THmn\_X8. The tables also include the post-layout cell area metrics. The special cells on Table 7 were developed to support the fined-grained MTNCL optimizations developed in [47].

Table 5: Async3D NCL library cell area.

| Cell Name                  | Cell Height (um)     | Cell Width (um)   | Cell Area (um²)  | Cell Name            | Cell Height (um) | Cell Width (um) | Cell Area (um²)    |

|----------------------------|----------------------|-------------------|------------------|----------------------|------------------|-----------------|--------------------|

| th12_X1                    | 3.69                 | 2.3               | 8.487            | th34w2_X1            | 3.69             | 7.36            | 27.1584            |

| th12_X2                    | 3.69                 | 2.3               | 8.487            | th34w2_X2            | 3.69             | 7.36            | 27.1584            |

| th12_X4                    | 3.69                 | 2.76              | 10.1844          | th34w2_X4            | 3.69             | 10.12           | 37.3428            |

| th12_X6                    | 3.69                 | 4.14              | 15.2766          | th34w2_X6            | 3.69             | 10.58           | 39.0402            |

| th12_X8                    | 3.69                 | 4.6               | 16.974           | th34w2_X8            | 3.69             | 12.88           | 47.5272            |

| th12_XL                    | 3.69                 | 2.3               | 8.487            | th34w2_XL            | 3.69             | 6.9             | 25.461             |

| th13_X1                    | 3.69                 | 3.22              | 11.8818          | th34w32_X1           | 3.69             | 6.44            | 23.7636            |

| th13_X2                    | 3.69                 | 2.76              | 10.1844          | th34w32_X2           | 3.69             | 5.52            | 20.3688            |

| th13_X4                    | 3.69                 | 4.14              | 15.2766          | th34w32_X4           | 3.69             | 5.98            | 22.0662            |

| th13_X6                    | 3.69                 | 4.6               | 16.974           | th34w32_X6           | 3.69             | 6.44            | 23.7636            |

| th13_X8                    | 3.69                 | 5.98              | 22.0662          | th34w32_X8           | 3.69             | 6.44            | 23.7636            |

| th13_XL                    | 3.69                 | 3.22              | 11.8818          | th34w32_XL           | 3.69             | 5.98            | 22.0662            |

| th14_X1                    | 3.69                 | 3.68              | 13.5792          | th34w3 X1            | 3.69             | 6.44            | 23.7636            |

| th14_X2                    | 3.69                 | 3.68              | 13.5792          | th34w3_X2            | 3.69             | 6.44            | 23.7636            |

| th14_X4                    | 3.69                 | 6.9               | 25.461           | th34w3_X4            | 3.69             | 6.9             | 25.461             |

| th14_X6                    | 3.69                 | 5.52              | 20.3688          | th34w3_X6            | 3.69             | 6.9             | 25.461             |

| th14_X8                    | 3.69                 | 6.44              | 23.7636          | th34w3_X8            | 3.69             | 7.82            | 28.8558            |

|                            |                      |                   |                  |                      |                  |                 |                    |

| th14_XL                    | 3.69                 | 3.68              | 13.5792          | th34w3_XL            | 3.69             | 5.98            | 22.0662            |

| th22_X1                    | 3.69                 | 3.68              | 13.5792          | th34_X1              | 3.69             | 6.9             | 25.461             |

| th22_X2                    | 3.69                 | 3.68              | 13.5792          | th34_XL              | 3.69             | 6.9             | 25.461             |

| th22_X4                    | 3.69                 | 4.14              | 15.2766          | th44w22_X1           | 3.69             | 7.82            | 28.8558            |

| th22_X6                    | 3.69                 | 5.98              | 22.0662          | th44w22_X2           | 3.69             | 7.82            | 28.8558            |

| th22_X8                    | 3.69                 | 6.44              | 23.7636          | th44w22_X4           | 3.69             | 10.12           | 37.3428            |

| th22_XL                    | 3.69                 | 3.68              | 13.5792          | th44w22_X6           | 3.69             | 10.58           | 39.0402            |

| th23w2_X1                  | 3.69                 | 5.52              | 20.3688          | th44w22_X8           | 3.69             | 12.42           | 45.8298            |

| th23w2_X2                  | 3.69                 | 5.52              | 20.3688          | th44w22_XL           | 3.69             | 7.82            | 28.8558            |

| th23w2_X4                  | 3.69                 | 5.06              | 18.6714          | th44w2_X1            | 3.69             | 7.36            | 27.1584            |

| th23w2_X6                  | 3.69                 | 5.98              | 22.0662          | th44w2_X4            | 3.69             | 13.8            | 50.922             |

| th23w2_X8                  | 3.69                 | 6.9               | 25.461           | th44w2_XL            | 3.69             | 7.36            | 27.1584            |

| th23w2_XL                  | 3.69                 | 5.52              | 20.3688          | th44w322_X1          | 3.69             | 6.9             | 25.461             |

| th23_X1                    | 3.69                 | 5.98              | 22.0662          | th44w322_X2          | 3.69             | 7.82            | 28.8558            |

| th23 X2                    | 3.69                 | 5.52              | 20.3688          | th44w322_X4          | 3.69             | 11.04           | 40.7376            |

| th23_X4                    | 3.69                 | 7.36              | 27.1584          | th44w322_X8          | 3.69             | 17.02           | 62.8038            |

| th23_X6                    | 3.69                 | 7.82              | 28.8558          | th44w322_XL          | 3.69             | 6.9             | 25.461             |

| th23_X8                    | 3.69                 | 10.12             | 37.3428          | th44w3 X1            | 3.69             | 6.44            | 23.7636            |

| th23 XL                    | 3.69                 | 5.52              | 20.3688          | th44w3 X2            | 3.69             | 5.06            | 18.6714            |

| th24comp_X1                | 3.69                 | 6.9               | 25.461           | th44w3_X4            | 3.69             | 6.9             | 25.461             |

| th24comp_X1                | 3.69                 | 6.44              | 23.7636          | th44w3_X6            | 3.69             | 8.28            | 30.5532            |

| th24comp_X4                | 3.69                 | 6.9               | 25.461           | th44w3_X8            | 3.69             | 10.12           | 37.3428            |

| th24comp_X6                | 3.69                 | 6.9               | 25.461           |                      | 3.69             | 5.06            | 18.6714            |

|                            |                      |                   |                  | th44w3_XL            |                  |                 |                    |

| th24comp_X8                | 3.69                 | 7.36              | 27.1584          | th44_X1              | 3.69             | 5.52            | 20.3688            |

| th24comp_XL                | 3.69                 | 5.98              | 22.0662          | th44_X2              | 3.69             | 5.98            | 22.0662            |

| th24w22_X1                 | 3.69                 | 6.9               | 25.461           | th44_X4              | 3.69             | 8.28            | 30.5532            |

| th24w22_X2                 | 3.69                 | 7.36              | 27.1584          | th44_X8              | 3.69             | 9.66            | 35.6454            |

| th24w22_X4                 | 3.69                 | 8.74              | 32.2506          | th44_XL              | 3.69             | 5.52            | 20.3688            |

| th24w22_X6                 | 3.69                 | 9.66              | 35.6454          | th54w22_X1           | 3.69             | 6.44            | 23.7636            |

| th24w22_X8                 | 3.69                 | 10.12             | 37.3428          | th54w22_X4           | 3.69             | 8.28            | 30.5532            |

| th24w22_XL                 | 3.69                 | 6.9               | 25.461           | th54w22_X6           | 3.69             | 8.74            | 32.2506            |

| th24w2_X1                  | 3.69                 | 6.44              | 23.7636          | th54w22_X8           | 3.69             | 11.04           | 40.7376            |

| th24w2_X2                  | 3.69                 | 6.44              | 23.7636          | th54w22_XL           | 3.69             | 7.36            | 27.1584            |

| th24w2_X4                  | 3.69                 | 7.82              | 28.8558          | th54w322_X1          | 3.69             | 7.82            | 28.8558            |

| th24w2_X6                  | 3.69                 | 8.28              | 30.5532          | th54w322_X2          | 3.69             | 7.36            | 27.1584            |

| th24w2_X8                  | 3.69                 | 8.28              | 30.5532          | th54w322_X4          | 3.69             | 7.82            | 28.8558            |

| th24w2_XL                  | 3.69                 | 6.9               | 25.461           | th54w322_X8          | 3.69             | 9.2             | 33.948             |

| th24_X1                    | 3.69                 | 9.2               | 33.948           | th54w322_XL          | 3.69             | 7.36            | 27.1584            |

| th24_X2                    | 3.69                 | 8.74              | 32.2506          | th54w32_X1           | 3.69             | 6.44            | 23.7636            |

| th24_X4                    | 3.69                 | 8.74              | 32.2506          | th54w32_X2           | 3.69             | 5.98            | 22.0662            |

| th24_X6                    | 3.69                 | 9.2               | 33.948           | th54w32_X4           | 3.69             | 9.2             | 33.948             |

| th24_X8                    | 3.69                 | 9.66              | 35.6454          | th54w32_X6           | 3.69             | 9.66            | 35.6454            |

| th24_XL                    | 3.69                 | 8.74              | 32.2506          | th54w32_X8           | 3.69             | 11.04           | 40.7376            |

| th33w2 X1                  | 3.69                 | 5.98              | 22.0662          | th54w32_XL           | 3.69             | 6.9             | 25.461             |

| th33w2_X1                  | 3.69                 | 5.06              | 18.6714          | thand0_X1            | 3.69             | 6.9             | 25.461             |

| th33w2_X4                  | 3.69                 | 6.44              | 23.7636          | thand0_X2            | 3.69             | 9.66            | 35.6454            |

|                            |                      |                   |                  |                      |                  |                 |                    |

| th33w2_X6                  | 3.69                 | 6.9               | 25.461           | thand0_X4            | 3.69             | 10.12           | 37.3428            |

| th33w2_X8                  | 3.69                 | 8.28              | 30.5532          | thand0_X6            | 3.69             | 16.1            | 59.409             |

| th33w2_XL                  | 3.69                 | 5.06              | 18.6714          | thand0_X8            | 3.69             | 19.78           | 72.9882            |

| th33_X1                    | 3.69                 | 4.6               | 16.974           | thand0_XL            | 3.69             | 6.9             | 25.461             |

| th33_X2                    | 3.69                 | 4.6               | 16.974           | thxor0_X1            | 3.69             | 6.9             | 25.461             |

| th33_X4                    | 3.69                 | 5.06              | 18.6714          | thxor0_X2            | 3.69             | 6.44            | 23.7636            |

| th33_X6                    | 3.69                 | 7.36              | 27.1584          | thxor0_X4            | 3.69             | 8.74            | 32.2506            |

| th33_X8                    | 3.69                 | 8.28              | 30.5532          | thxor0_X6            | 3.69             | 10.12           | 37.3428            |

| th33_XL                    | 3.69                 | 4.6               | 16.974           | thxor0_X8            | 3.69             | 11.5            | 42.435             |

|                            | 3.69                 | 8.28              | 30.5532          | thxor0_XL            | 3.69             | 7.36            | 27.1584            |

| th34w22d_X1                |                      |                   | 33.948           | bufSleep_X1          | 3.69             | 2.3             | 8.487              |

| th34w22d_X1<br>th34w22d_X2 | 3.69                 | 9.2               | 33.340           |                      |                  |                 |                    |

| th34w22d_X2                | 3.69<br>3.69         |                   |                  |                      |                  |                 |                    |

|                            | 3.69<br>3.69<br>3.69 | 9.2<br>9.2<br>9.2 | 33.948<br>33.948 | th12b_X1<br>th22d_X1 | 3.69<br>3.69     | 3.68<br>5.06    | 13.5792<br>18.6714 |

(a) (b)

Table 6: Async3D MTNCL library cell area.

| Cell Name                | Cell Height (um) | Cell Width (um) | Cell Area (um²) |

|--------------------------|------------------|-----------------|-----------------|

| th12m_X1                 | 3.69             | 4.6             | 16.974          |

| th12m_X2                 | 3.69             | 6.44            | 23.7636         |

| th12m_X4                 | 3.69             | 8.28            | 30.5532         |

| th12m_X6                 | 3.69             | 10.12           | 37.3428         |

| th12m_X8                 | 3.69             | 12.42           | 45.8298         |

| th12m XL                 | 3.69             | 3.68            | 13.5792         |

| th13m X1                 | 3.69             | 5.06            | 18.6714         |

| th13m X2                 | 3.69             | 7.36            | 27.1584         |

| th13m X4                 | 3.69             | 10.12           | 37.3428         |