University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

12-2018

# Investigation of a GaN-Based Power Supply Topology Utilizing Solid State Transformer for Low Power Applications

Akrem Mohamed Elrajoubi University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electronic Devices and Semiconductor Manufacturing Commons, and the Power and Energy Commons

#### Citation

Elrajoubi, A. M. (2018). Investigation of a GaN-Based Power Supply Topology Utilizing Solid State Transformer for Low Power Applications. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3024

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

### Investigation of a GaN-Based Power Supply Topology Utilizing Solid State Transformer for Low Power Applications

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

by

Akrem Mohamed Elrajoubi College of Industrial Technology Bachelor of Science in Electro-Mechanical Engineering, 2006 Universiti Teknologi Malaysia Master of Science in Electrical Engineering, 2010

### December 2018 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

Simon S. Ang, Ph.D. Dissertation Director

Juan C. Balda, Ph.D. Committee Member

Roy A. McCann, Ph.D. Committee Member

Jia Di, Ph.D. Committee Member

#### ABSTRACT

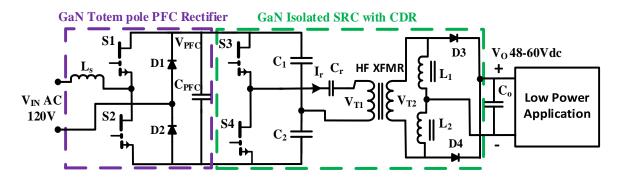

Gallium nitride (GaN) power devices exhibit a much lower gate capacitance for a similar onresistance than its silicon counterparts, making it highly desirable for high-frequency operation in switching converters, which leads to their significant benefits on power density, cost, and system volume. High-density switching converters are being realized with GaN power devices due to their high switching speeds that reduce the size of energy-storage circuit components. The purpose of this dissertation research is to investigate a new isolated GaN AC/DC switching converter based on solid-state transformer configuration with a totem-pole power factor corrector (PFC) front-end, a half-bridge series-resonant converter (SRC) for power conversion, and a current-doubler rectifier (CDR) at its output. A new equivalent circuit model for the converter is constructed consisting of a loss-free resistor model for the PFC rectifier with first harmonic approximation model for the SRC and the CDR. Then, state-space analysis is performed to derive the converter transfer function in order to design the controllers to yield sufficient phase margins.

The converter offers the advantages of voltage regulation feature of the solid-state transformer, low harmonics and close-to-unity power factor of the PFC rectifier, soft-switching of the halfbridge SRC, reduced size of the high-frequency transformer, and smaller leakage inductance of the CDR which is used for low-voltage high-current applications as the CDR draws half of the load current in the transformer secondary side yielding less copper losses. A high-frequency nanocrystalline toroid transformer, based on a modified equation to determine its leakage inductance, is designed and fabricated to satisfy the performance specifications of the converter. A meticulously planned gate driving strategy together with a Kelvin-source return circuitry is used to mitigate Miller effects, minimize gate ringing, and minimize the parasitics of the pull-down and pull-up loops of the converter. A new programming method that combines MATLAB Simulink embedded coder with code composer studio for the TMS320F28335 digital signal processor (DSP) controller is developed and demonstrated. Finally, the GaN-based AC/DC converter is experimentally verified for a 120Vac to 48Vdc/60Vdc conversion operating at 100 kHz for various loadings.

©2018 by Akrem Mohamed Elrajoubi All Rights Reserved

#### ACKNOWLEDGMENT

First of all, all thanks and praise are due to Allah, the Almighty, Lord of the worlds.

I would like to express my sincere gratitude and thanks to my advisor Dr. Simon Ang, for his continuous guidance, patience, encouragement and support of my Ph.D study. His advice and guidance and expertise on all the time of my research have been invaluable for me.

Besides my advisor, I would like to thank the rest of my dissertation committee members, Dr. Juan Balda, Dr. Roy McCann, and Dr. Jia Di for serving as my research committee members. I am very grateful to your help, expertise, and guidance.

Special thank you to my wife, Intisar, and my little kids. You suspended your dreams and goals in order to help me. I am so grateful for your dedication, motivation, patience, and support throughout the whole journey.

Additionally I would also like to express my sincere thanks to all my research team and friends: Luciano García, Vinson Jones, Roderick Montoya, Kirsch Mackey, Kenny George, Ali Abushaiba, and Affan Abbasi. You helped me to achieve my research objectives and overcome many challenges.

Last but not least, I would like to thank and express my special appreciation to my brothers, and friends both in the United States and Libya who have supported me along the way. You all who helped and encouraged me to overcome all the hardships, not only in the study but also in my daily life affairs. They have been always there supporting and encouraging me. God bless you all.

## **TABLE OF CONTENTS**

| CHAPTER 1: INTRODUCTION                                                   | 1  |

|---------------------------------------------------------------------------|----|

| 1.1 GaN Based Converters' Features                                        | 1  |

| 1.2 Solid-State Transformer Functionalities                               | 4  |

| 1.3 Dissertation Motivation                                               | 6  |

| 1.4 Dissertation Objectives                                               | 8  |

| 1.5 Dissertation Organization                                             | 9  |

| 1.6 References                                                            | 9  |

| CHAPTER 2: LITERATURE REVIEW                                              | 11 |

| 2.1 Introduction                                                          | 11 |

| 2.2 Solid State Transformer Operation and Functionalities                 | 14 |

| 2.3 Solid State Transformer Components and Topologies                     | 16 |

| 2.4 Solid State Transformer Applications and Emerging Research Directions | 20 |

| 2.5 Resonant Conversion Concepts and Soft Switching Operation             | 23 |

| 2.6 GaN Gate Drivers Design Considerations                                | 24 |

| 2.7 Conclusion                                                            | 26 |

| 2.8 References                                                            | 27 |

|                                                                           |    |

# CHAPTER 3: SIMULATION AND MODELING OF THE PROPOSED GaN

| TOPOLOGY                                                  | 29 |

|-----------------------------------------------------------|----|

| 3.1 Introduction                                          | 29 |

| 3.2 Proposed GaN AC/DC Power Supply Converter             | 30 |

| 3.3 Converter Design Calculations                         | 32 |

| 3.4 Proposed Converter Topology Simulation                | 34 |

| 3.5 Closed-loop Simulation and Controller Design          | 39 |

| 3.6 Converter Modes of Operation and Equivalent Modelling | 47 |

| 3.7 Converter Loss Analysis                               | 52 |

| 3.8 Converter Simulation in PSpice                        | 53 |

| 3.9 Conclusion  |   |    |

|-----------------|---|----|

| 3.10 References | 5 | 58 |

| CHAPTER 4: HIGH-FREQUENCY TRANSFORMER DESIGN      | 60 |

|---------------------------------------------------|----|

| 4.1 Introduction                                  | 60 |

| 4.2 High-Frequency Transformer Design Methodology | 61 |

| 4.3 Transformer Design Examples                   | 69 |

| 4.3.1 Design Example 1                            | 69 |

| 4.3.2 Design Example 2                            | 74 |

| 4.4 Conclusion                                    | 77 |

| 4.5 References                                    | 78 |

# CHAPTER 5: TMS320F28335 DIGITAL SIGNAL PROCESSOR PROGRAMMING

|                                                                | 79  |

|----------------------------------------------------------------|-----|

| 5.1 Introduction                                               | 79  |

| 5.2 CCSV6 Target Configuration                                 | 82  |

| 5.3 Setup of xMakefile for CCS v5                              | 84  |

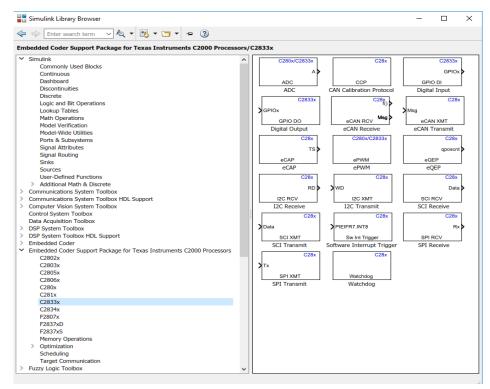

| 5.4 Embedded Coder Support Package for TI C2000 Processors     | 86  |

| 5.5 Flash Memory Programming (Stand-Alone Mode)                | 88  |

| 5.6 Debug Configurations and Code Running                      | 90  |

| 5.7 ePWM, ADC, GPIO, and PI Blocks                             | 91  |

| 5.8 Closed-Loop Control model for the Developed AC/DC Topology | 98  |

| 5.9 Conclusion                                                 | 100 |

| 5.10 References                                                | 101 |

| CHAPTER 6: EXPERIMENTAL RESULTS AND DISCUSSIONS |     |

|-------------------------------------------------|-----|

| 6.1 Introduction                                |     |

| 6.2 Converter Topology Prototype Design         |     |

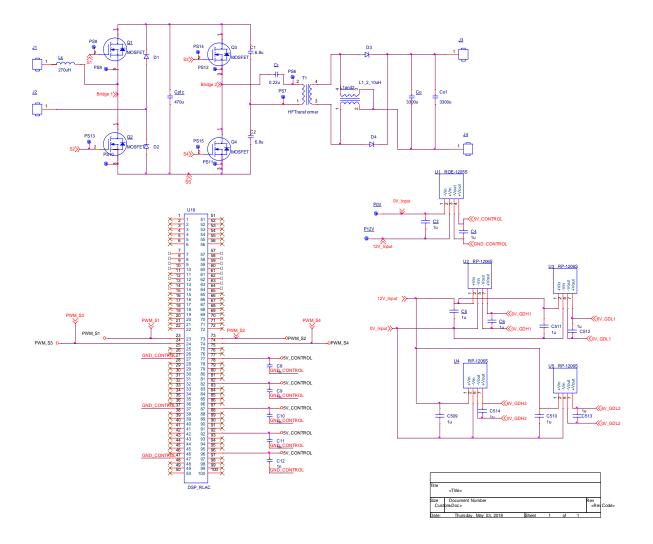

| 6.2.1 OrCAD Capture Circuit Schematic Design    | 102 |

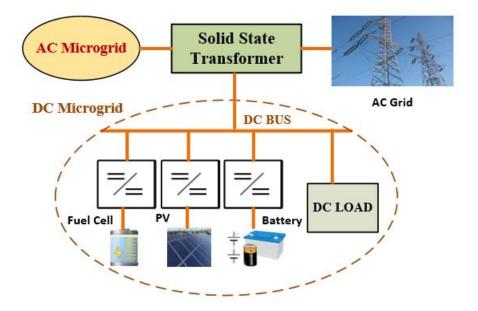

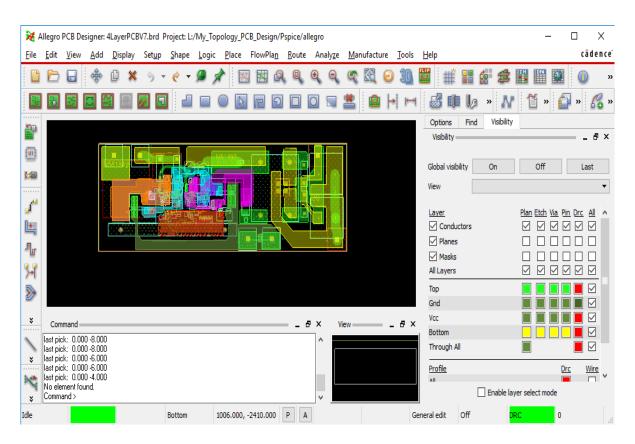

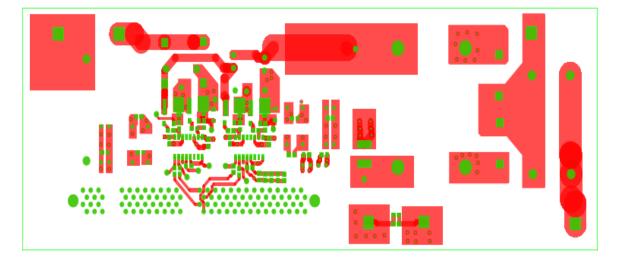

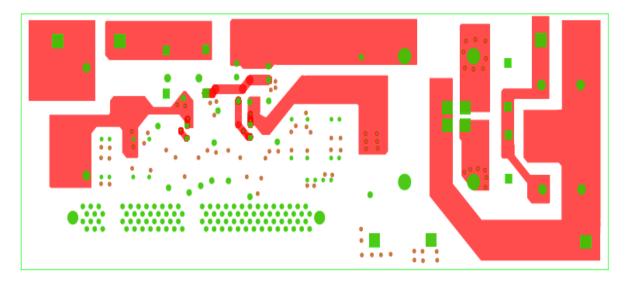

| 6.2.2 Allegro PCB Editor Layout Design | 102 |

|----------------------------------------|-----|

| 6.3 GaN Gate Driver Considerations     |     |

| 6.4 Converter Components Selection     | 111 |

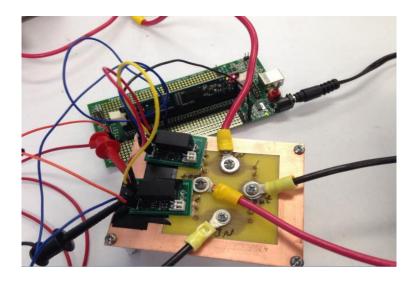

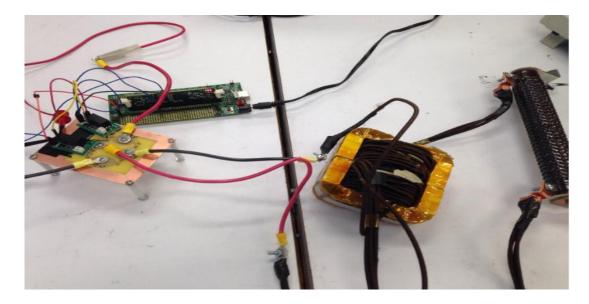

| 6.5 Experimental Prototype Testing     | 112 |

| 6.6 Experimental Results               | 115 |

| 6.7 Conclusion                         | 125 |

| 6.8 References                         | 127 |

#

| 7.1 Introduction                                          |  |

|-----------------------------------------------------------|--|

| 7.2 Dissertation Contributions                            |  |

| 7.3 Dissertation Recommendations for Future Research Work |  |

| Appendix A: MATLAB Code for HF Transformer Design Example 1         | 134 |

|---------------------------------------------------------------------|-----|

| Appendix B: TMS320F28335 DSP C Code for the AC/DC converter model   | 137 |

| Appendix C: Converter closed-loop MATLAB schematic.                 | 153 |

| Appendix D: The OrCAD Capture schematic of the AC/DC converter      | 154 |

| Appendix E: The OrCAD Allegro PCB Editor 4-Layer PCB Layout Design. | 155 |

### LIST OF FIGURES

| Figure 1.1. The Advantageous of GaN properties compared to Si and GaAs1                                   |

|-----------------------------------------------------------------------------------------------------------|

| Figure 1.2. Solid State Transformer structure                                                             |

| Figure 1.3. SST power management for DC microgrid5                                                        |

| Figure 1.4. The proposed GaN AC/DC converter topology                                                     |

| Figure 2.1. Solid State Transformer configuration                                                         |

| Figure 2.2. SST functional configuration15                                                                |

| Figure 2.3. Topology classification of SST18                                                              |

| Figure 2.4. Three stages SST configuration                                                                |

| Figure 2.5. Gen-I SST single phase topology19                                                             |

| Figure 2.6. Single phase Gen-I SST average model19                                                        |

| Figure 2.7. Future distribution network utilizing SSTs20                                                  |

| Figure 2.8. SST compensates reactive power and filters harmonics                                          |

| Figure 2.9. SST for DC Microgrid22                                                                        |

| Figure 2.10. The gate driver for the GaN half-bridge structure                                            |

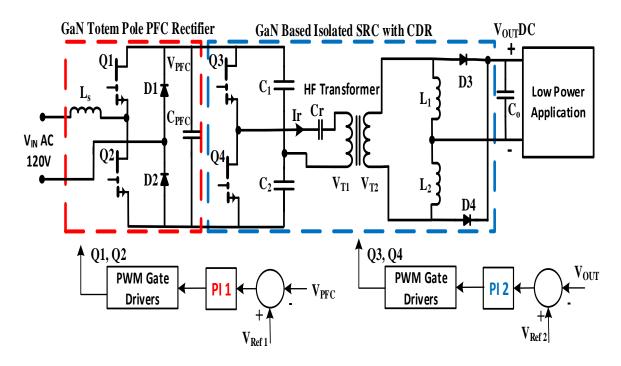

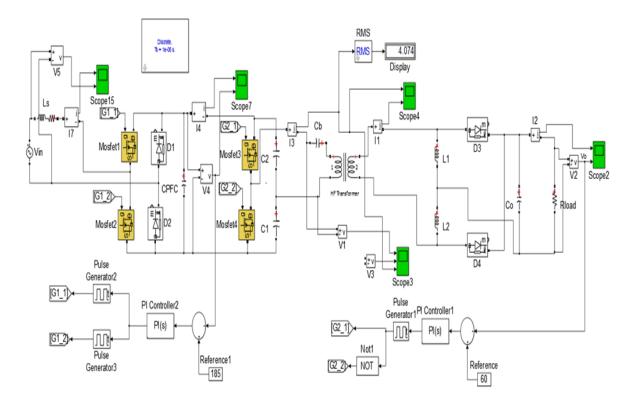

| Figure 3.1. The proposed GaN AC/DC converter topology                                                     |

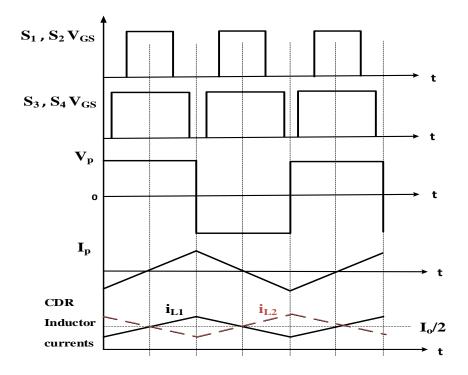

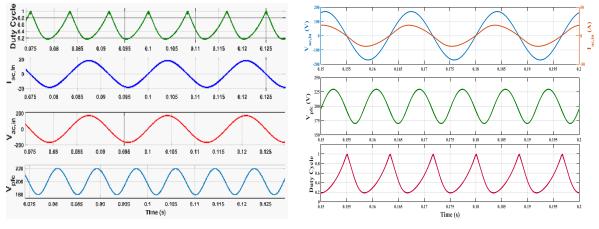

| Figure 3.2. Key theoretical waveforms of the proposed converter                                           |

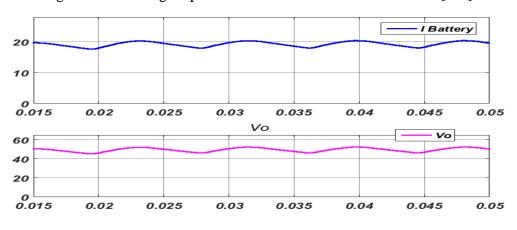

| Figure 3.3. The converter output current and voltage                                                      |

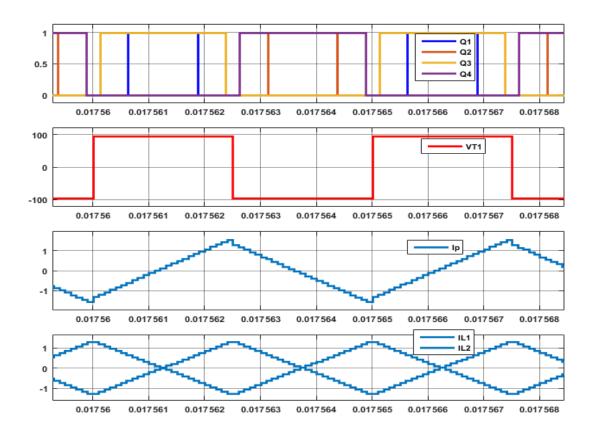

| Figure 3.4. Main simulation waveforms of the proposed converter at 64 kHz35                               |

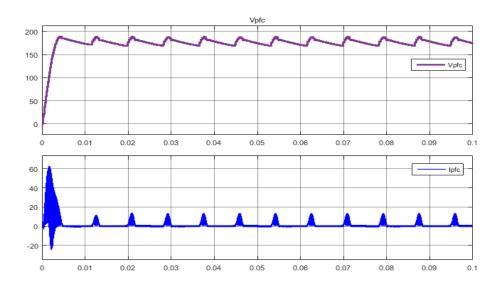

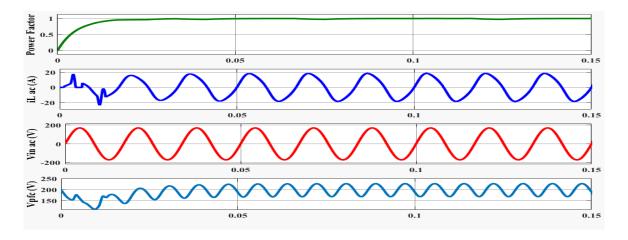

| Figure 3.5. PFC voltage and input current open-loop simulation waveforms                                  |

| Figure 3.6. Key simulation waveforms of the proposed converter at $f_s = 200$ kHz36                       |

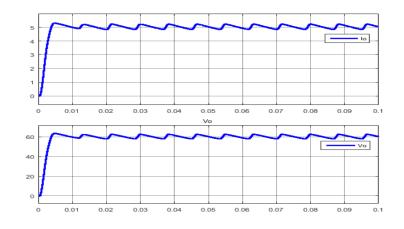

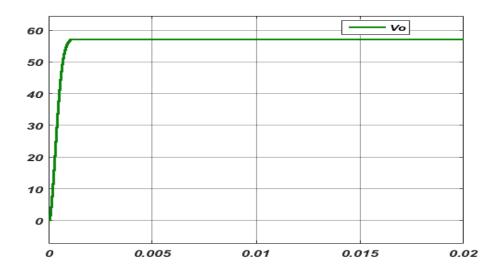

| Figure 3.7. The converter regulated output voltage ( $V_0 = 57 \text{ V}$ )                               |

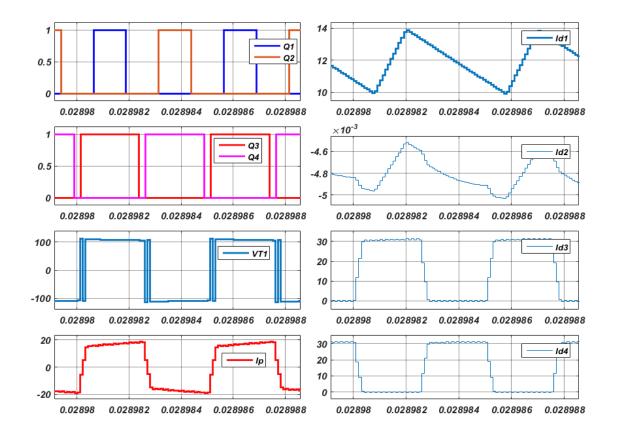

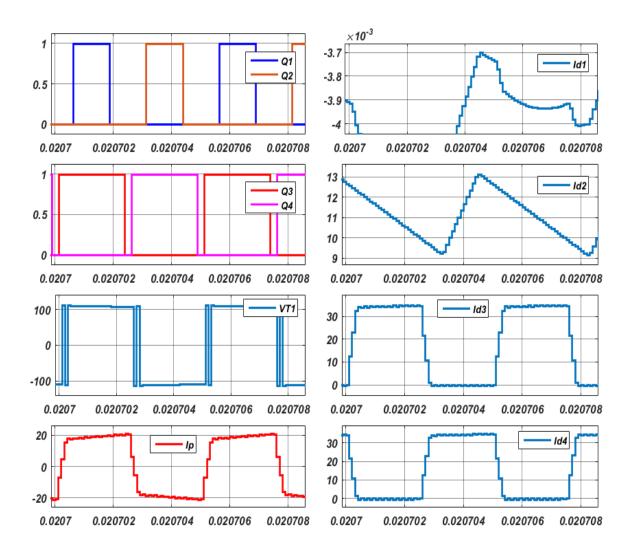

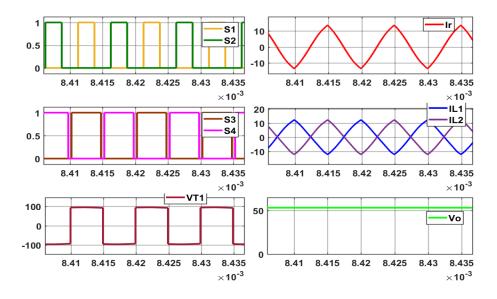

| Figure 3.8. Switches' pulses, $V_{T1}$ , $I_p$ , and diodes' currents when $D_1$ is ON and $D_2$ is OFF37 |

| Figure 3.9. Switches' pulses, $V_{T1}$ , $I_p$ , and diodes' currents when $D_2$ is ON and $D_1$ is OFF38 |

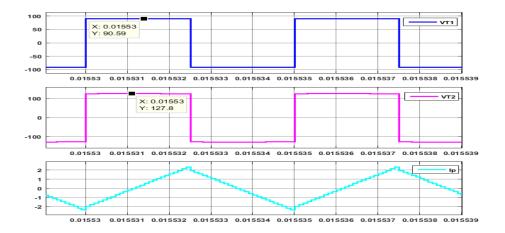

| Figure 3.10. $V_{T1}$ , $V_{T2}$ , and $I_p$ of the proposed converter for 200 kHz, 300 W load39          |

| Figure 3.11. The proposed GaN AC/DC converter with PI controllers40                                       |

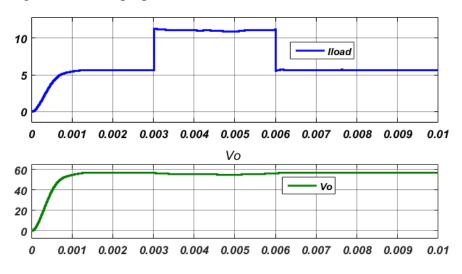

| Figure 3.12. The converter output current and voltage for load step disturbance40                         |

| Figure 3.13. Key simulation waveforms of the proposed converter at 100 kHz41                              |

| Figure 3.14. Converter closed-loop MATLAB schematic                                                    |

|--------------------------------------------------------------------------------------------------------|

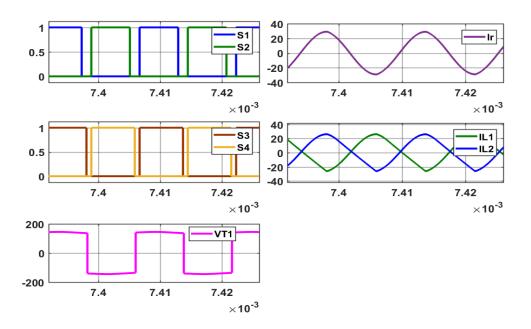

| Figure 3.15. PFC control simulation waveforms42                                                        |

| Figure 3.16. PFC average current mode control simulation waveforms                                     |

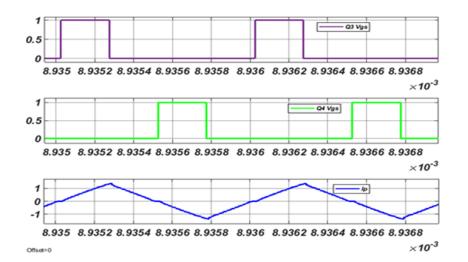

| Figure 3.17. SRC gate pulses and DCM resonant tank current                                             |

| Figure 3.18. Battery voltage and charging current                                                      |

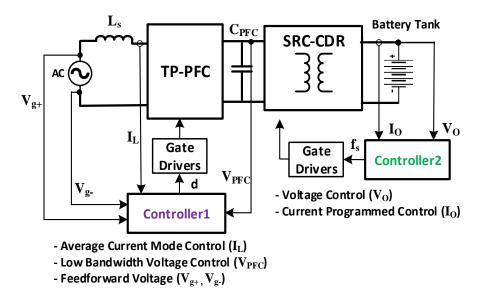

| Figure 3.19. The controller diagram for the proposed converter                                         |

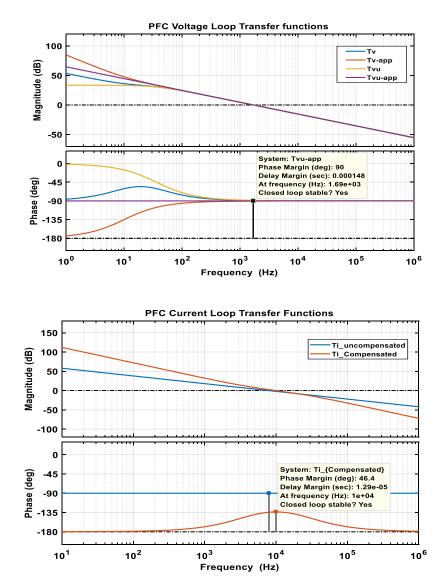

| Figure 3.20. PFC voltage and current controller bode plots                                             |

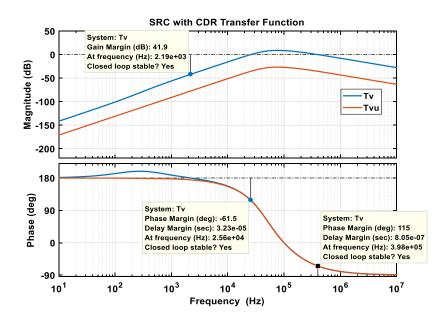

| Figure 3.21. Compensated and uncompensated SRC with CDR bode plots                                     |

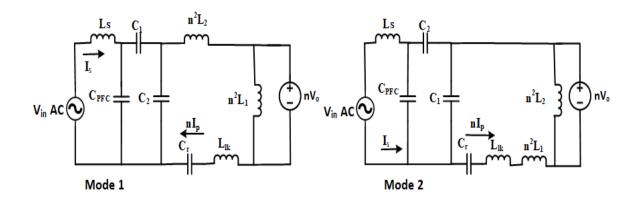

| Figure 3.22. Converter equivalent circuits referred to the HF-XFMR's primary side                      |

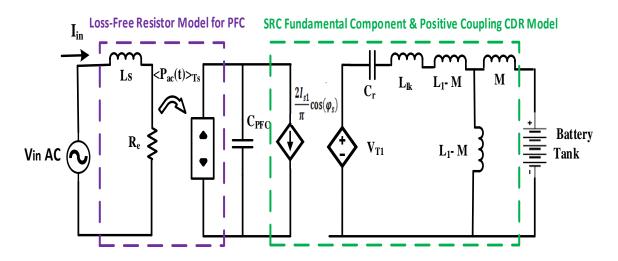

| Figure 3.23. The equivalent model for the proposed converter                                           |

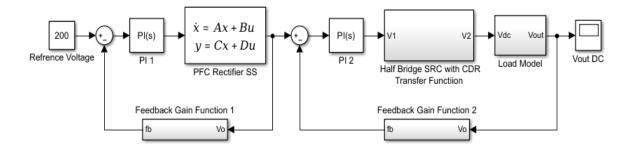

| Figure 3.24. Feedback control simulation for the power supply converter                                |

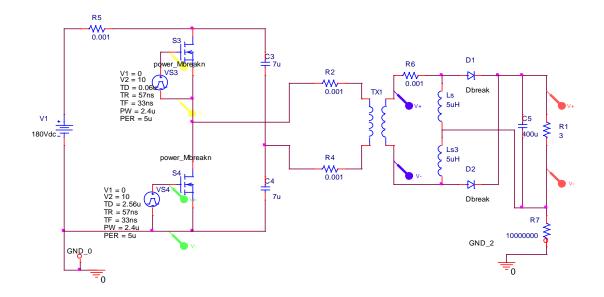

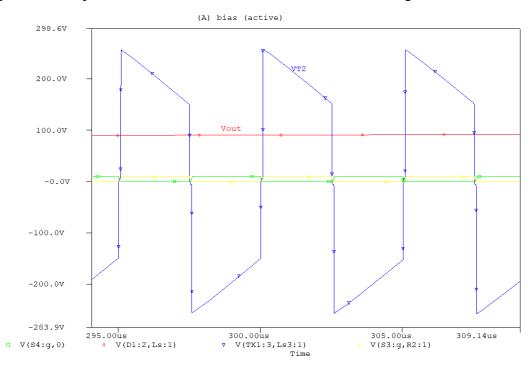

| Figure 3.25. PSpice simulation schematic for an isolated half-bridge inverter with CDR54               |

| Figure 3.26. PSpice simulation waveforms for the half-bridge with CDR topology54                       |

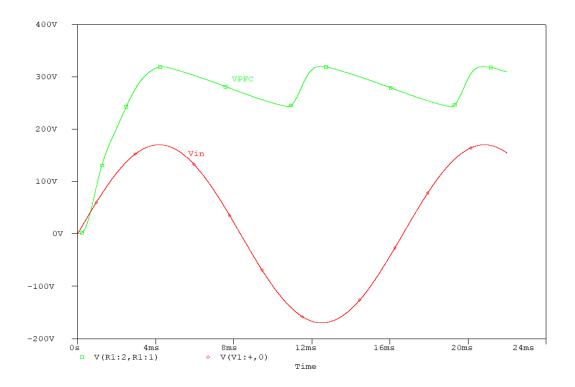

| Figure 3.27. PSpice PFC stage simulation input and output voltages waveforms55                         |

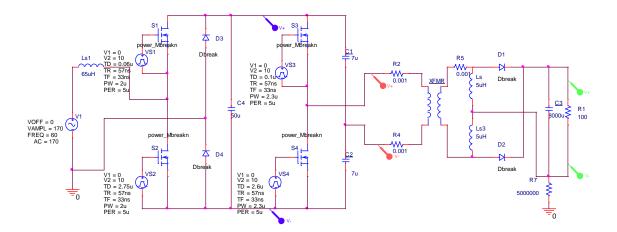

| Figure 3.28. PSpice schematic for a PFC with an isolated half-bridge inverter and CDR55                |

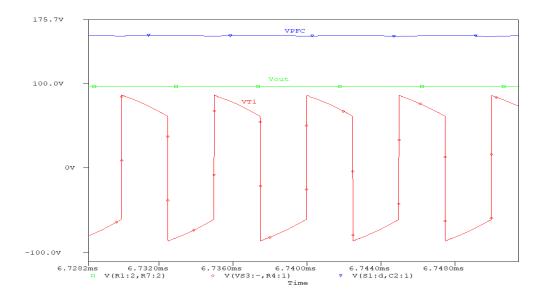

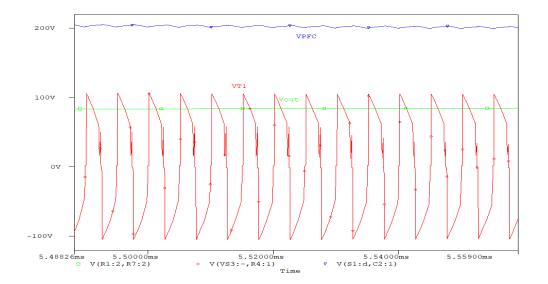

| Figure 3.29. PSpice waveforms ( $V_{PFC}$ , $V_{T1}$ , $V_o$ ) at 200 kHz for low input voltage56      |

| Figure 3.30. PSpice simulation waveforms of $V_{PFC}$ , $V_{T1}$ , $V_o$ for $V_{in} = 120 V \dots 56$ |

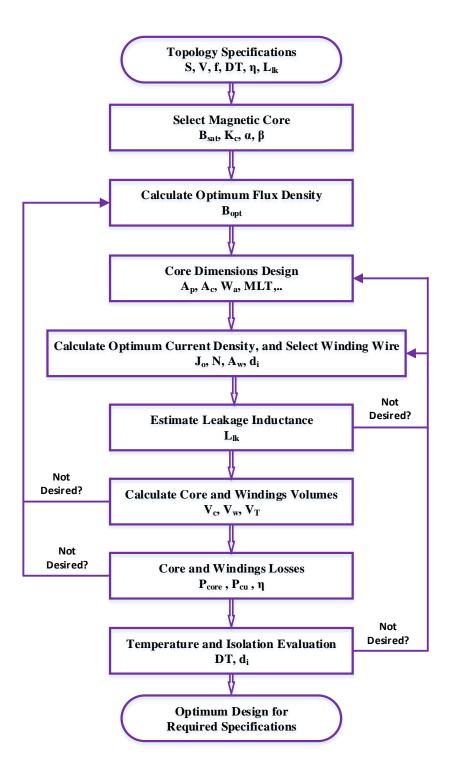

| Figure 4.1. HF Transformer Design Procedure                                                            |

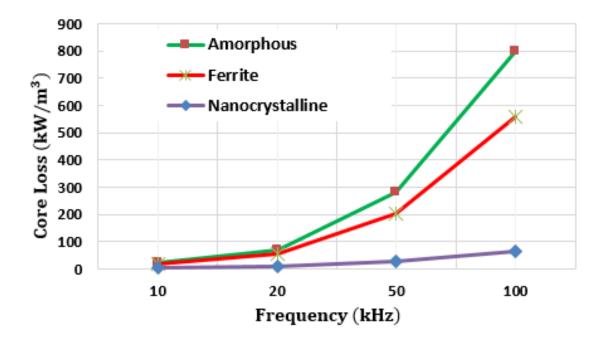

| Figure 4.2. Magnetic materials core losses (kW/m <sup>3</sup> ) versus frequency63                     |

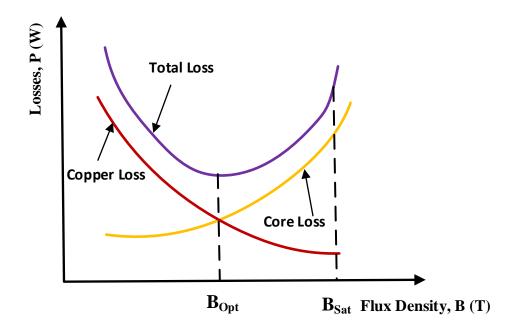

| Figure 4.3. Core, winding, and total loss verses flux density                                          |

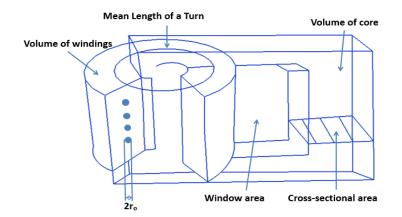

| Figure 4.4. Transformer core and winding typical layout65                                              |

| Figure 4.5. Metglas Amorphous AMCC – 63 laminated core                                                 |

| Figure 4.6. The developed 25 kHz, 5 kVA, 440 V/110 V amorphous transformer71                           |

| Figure 4.7. TMS320F28335 DSP to control the gate drivers of the half-bridge inverter71                 |

| Figure 4.8. Half-bridge inverter and 25 kHz transformer testing setup72                                |

| Figure 4.9. Transformer input voltage for $V_{in} = 20 V$                                              |

| Figure 4.10. Transformer input voltage for $V_{in} = 30 \text{ V} \dots 73$                            |

| Figure 4.11. Example 1 transformer output voltage for $V_{in} = 20 \text{ V}$                          |

| Figure 4.12. Example 1 transformer output voltage for $V_{in} = 46$ V74                                |

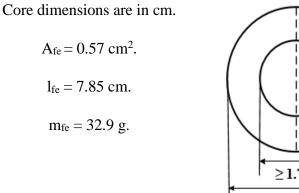

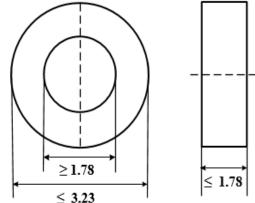

| Figure 4.13. W376-04 nanocrystalline toroid core74                                       |

|------------------------------------------------------------------------------------------|

| Figure 4.14. The fabricated 100 kHz nanocrystalline toroid transformer75                 |

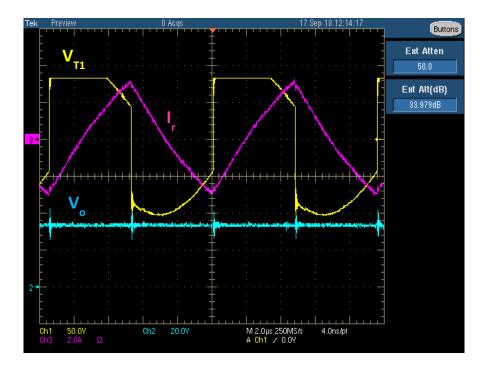

| Figure 4.15. 100 kHz transformer voltages ( $V_{T1}$ , $V_{T2}$ ), and primary current77 |

| Figure 5.1. TMS320F28335 DSP with the USB docking station                                |

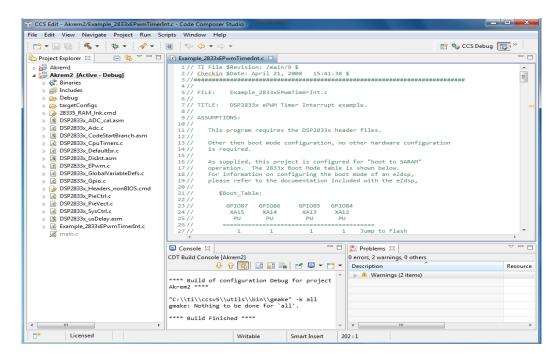

| Figure 5.2. CCS home screen after building the project                                   |

| Figure 5.3. CCS debug home screen                                                        |

| Figure 5.4. MATLAB installed toolboxes                                                   |

| Figure 5.5. Launch new target configuration                                              |

| Figure 5.6. Debugged target configuration                                                |

| Figure 5.7. xMakefile configuration                                                      |

| Figure 5.8. xMakefile configuration tool directories                                     |

| Figure 5.9. xMakefile configuration clone compiler                                       |

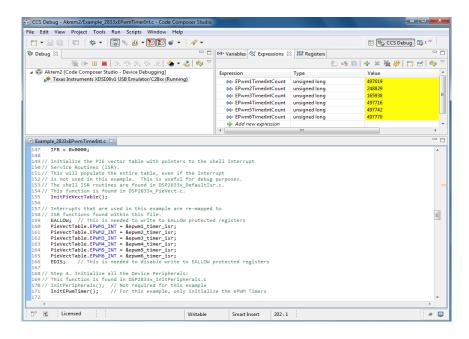

| Figure 5.10. MATLAB checkEnvSetup command for F28335 DSP86                               |

| Figure 5.11. Flash APIs environment variable                                             |

| Figure 5.12. Embedded coder support package                                              |

| Figure 5.13. Code generation parameters configuration                                    |

| Figure 5.14. Stand-alone execution configuration parameters                              |

| Figure 5.15. CCS debug configurations                                                    |

| Figure 5.16. Loading the .out file for the project                                       |

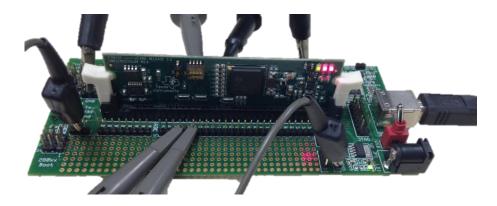

| Fig 5.17. TMS320F28335 DSP board                                                         |

| Figure 5.18. ePWM block parameters                                                       |

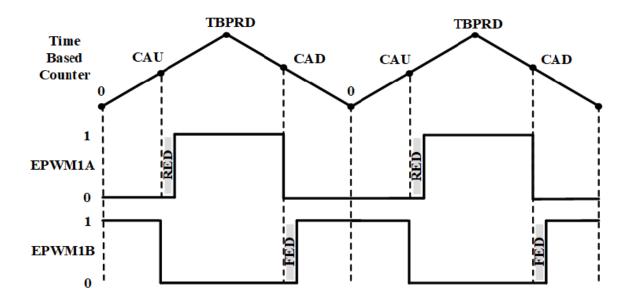

| Figure 5.19. ePWM signal generation                                                      |

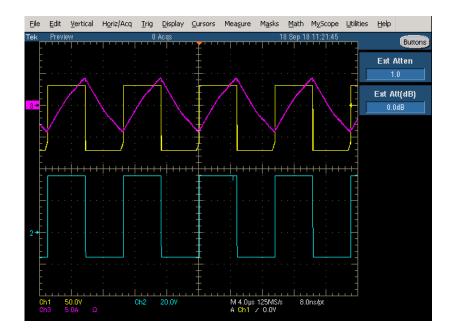

| Figure 5.20. ePWMA and ePWMB deadband93                                                  |

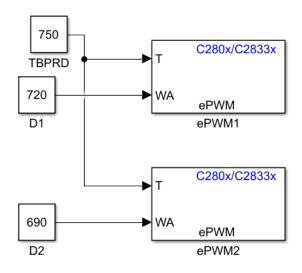

| Figure 5.21. Synchronized two ePWM blocks                                                |

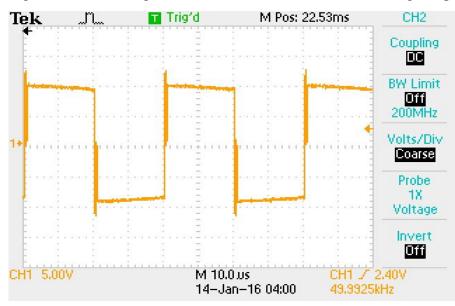

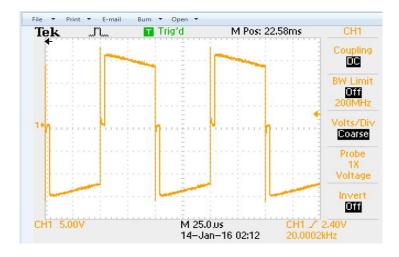

| Figure 5.22. Synchronized ePWM pulses at 100 kHz94                                       |

| Figure 5.23. ePWM parameters for synchronization                                         |

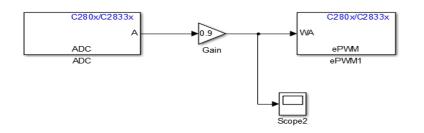

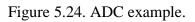

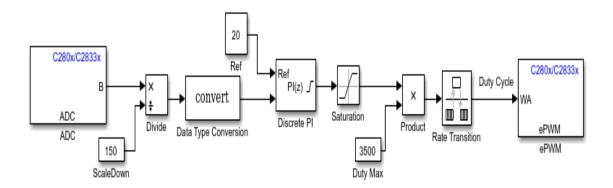

| Figure 5.24. ADC example96                                                               |

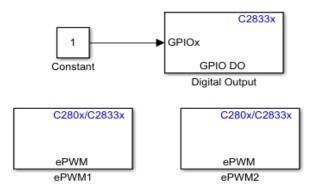

| Figure 5.25. ADC and ePWM blocks parameters96                                            |

| Figure 5.26. PI controller for duty cycle of ePWM output                                 |

| Figure 5.27. TMS320F28335 DSP model for the AC/DC converter prototype                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.28. Designed AC/DC converter closed-loop DSP model                                                                                                              |

| Figure 5.29. Designed SRC PI controller                                                                                                                                  |

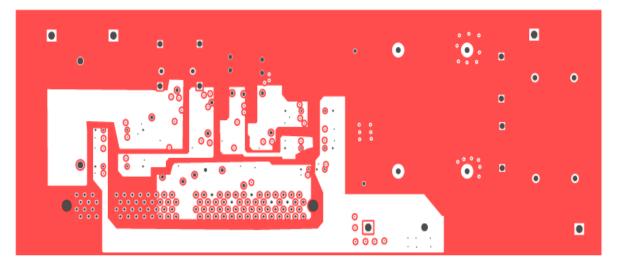

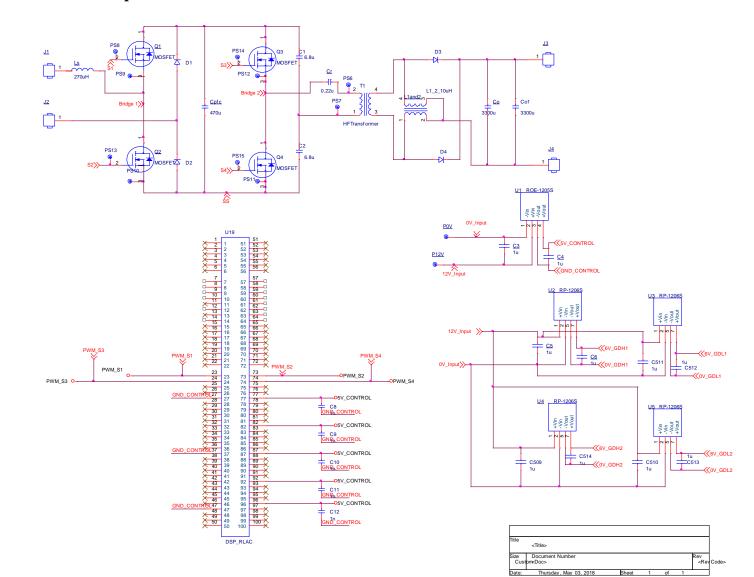

| Figure 6.1. OrCAD Capture schematic of the AC/DC converter                                                                                                               |

| Figure 6.2. 4-Layer converter layout in Cadence Allegro PCB Designer                                                                                                     |

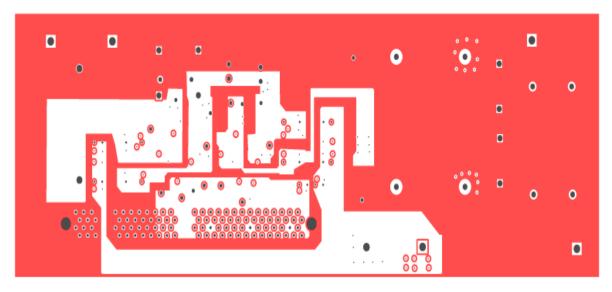

| Figure 6.3. Top Layer PCB Layout                                                                                                                                         |

| Figure 6.4. Bottom Layer PCB Layout                                                                                                                                      |

| Figure 6.5. Layer 2 layout with Drill holes                                                                                                                              |

| Figure 6.6. Layer 3 layout with Drill holes                                                                                                                              |

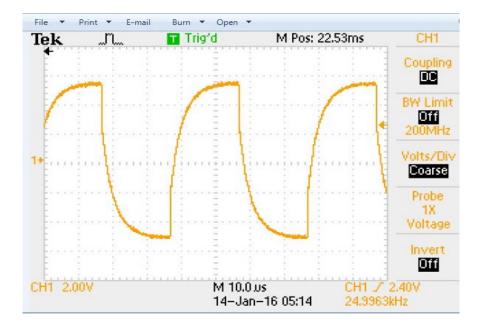

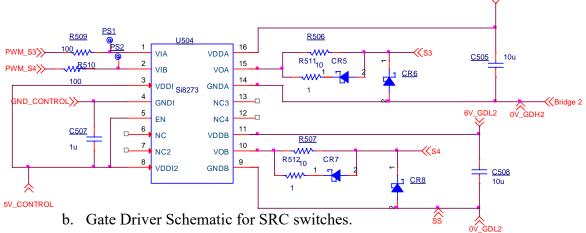

| Figure 6.7. Gate driver for GaN transistor                                                                                                                               |

| Figure 6.8. Designed gate drivers schematic for GaN half-bridge legs                                                                                                     |

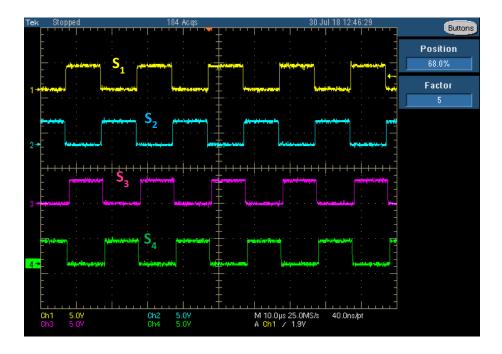

| Figure 6.9. 3.3 V DSP signals for gate drivers at 50 kHz                                                                                                                 |

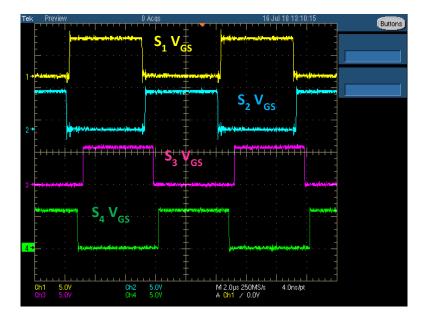

| Figure 6.10. Gate drivers' synchronized signals for GaN switches ( $V_{GS}$ ) at 100 kHz110                                                                              |

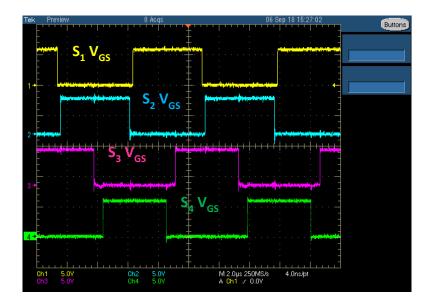

| Figure 6.11. Phase shifted V <sub>GS</sub> signals for switching at 105 kHz110                                                                                           |

| Figure 6.12. The fabricated GaN AC/DC converter prototype board                                                                                                          |

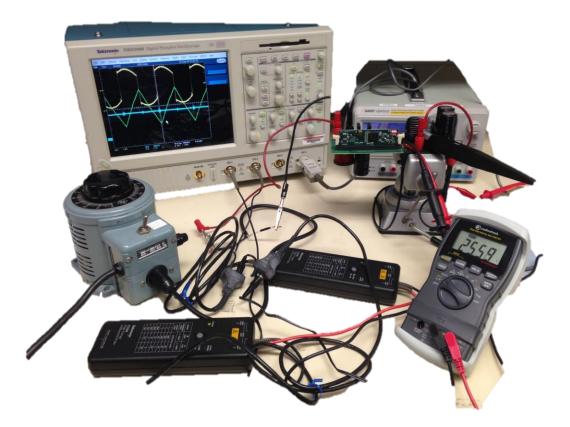

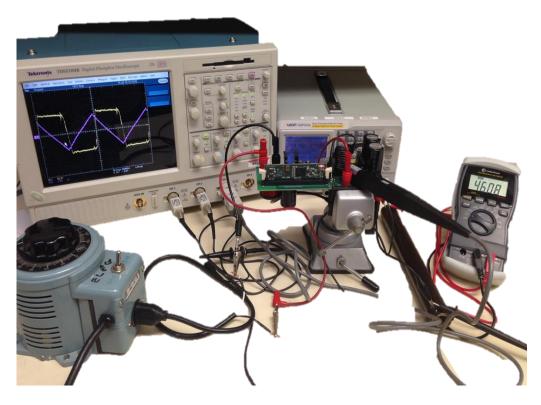

| Figure 6.13. Experimental setup using P5200 isolated voltage differential probes114                                                                                      |

| Figure 6.14. Converter experimental testing setup for DC output voltage of 46 V114                                                                                       |

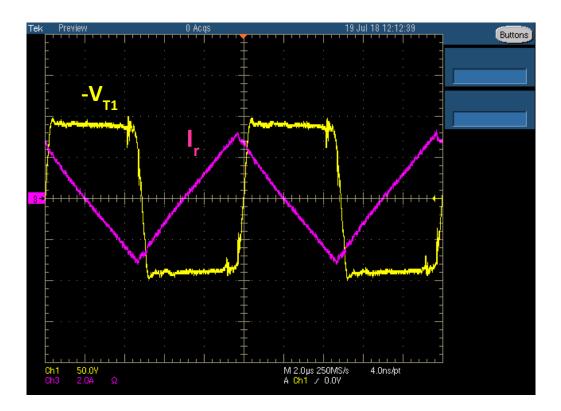

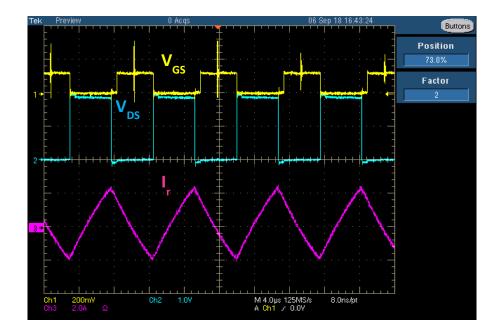

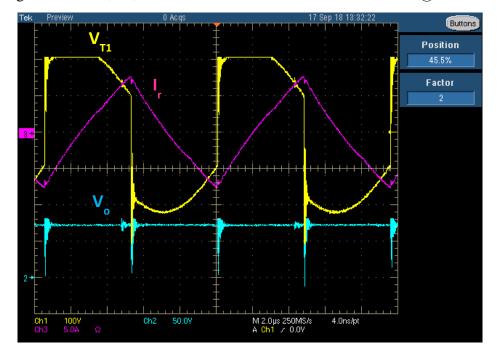

| Figure 6.15V <sub>T1</sub> and I <sub>r</sub> experimental results for $V_{in} = 60$ V and $R_L = 100$ k $\Omega$ 115                                                    |

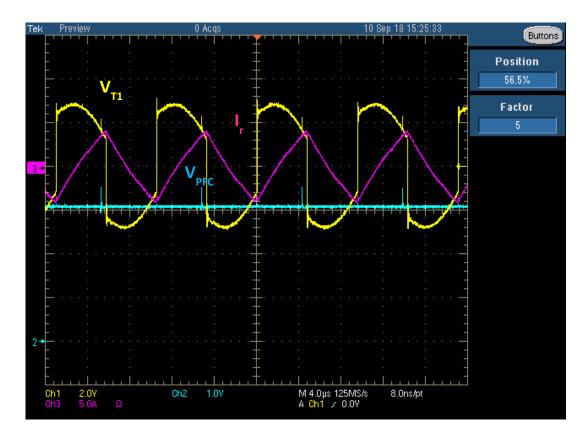

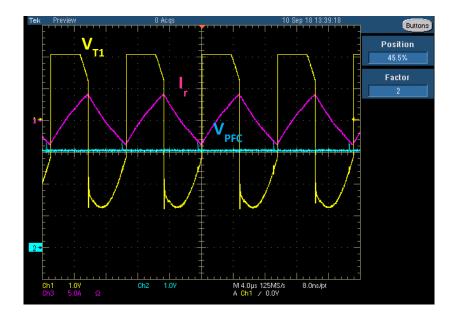

| Figure 6.16. $V_{T1}$ , $V_{PFC}$ , and $I_r$ waveforms for $V_{in} = 70$ V and 1 k $\Omega$ @ 105 kHz116                                                                |

| Figure 6.17. $V_{T1}$ , $V_{PFC}$ , and $I_r$ waveforms for $V_{in} = 70$ V and 2 k $\Omega$ @ 105 kHz117                                                                |

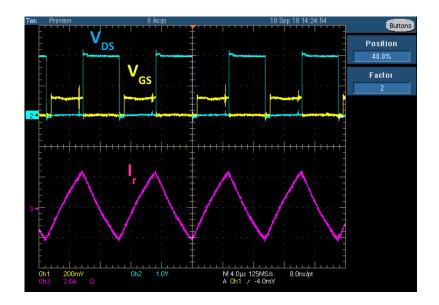

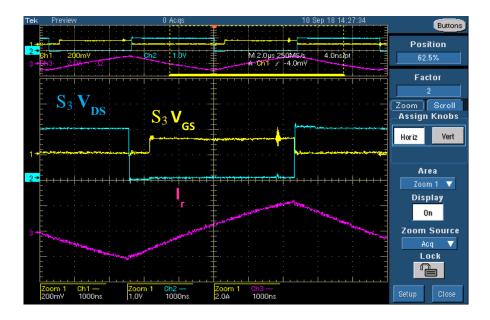

| Figure 6.18. S <sub>3</sub> V <sub>GS</sub> V <sub>DS</sub> , and I <sub>r</sub> waveforms for $R_L = 2 \text{ k}\Omega$ @ 105 kHz117                                    |

| Figure 6.19. S <sub>3</sub> V <sub>GS</sub> V <sub>DS</sub> , and I <sub>r</sub> waveforms for $R_L = 2 \text{ k}\Omega$ @ 105 kHz118                                    |

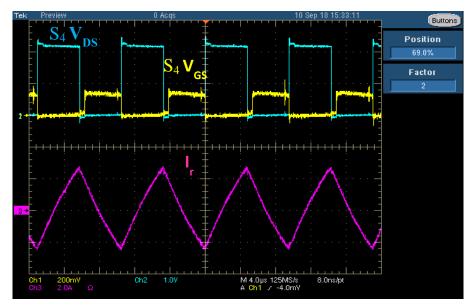

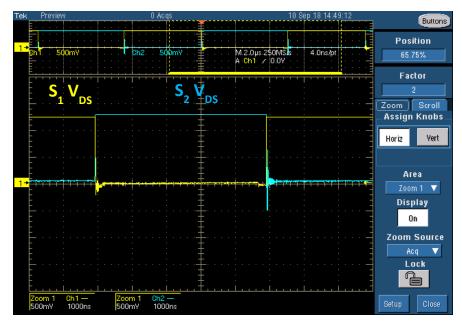

| Figure 6.20. S <sub>4</sub> V <sub>GS</sub> V <sub>DS</sub> , and I <sub>r</sub> waveforms for $R_L = 1 \text{ k}\Omega$ @ 105 kHz118                                    |

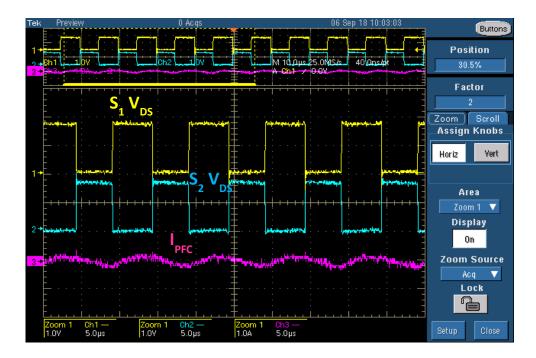

| Figure 6.21. S <sub>4</sub> V <sub>GS</sub> V <sub>DS</sub> , and I <sub>r</sub> waveforms for phase shifted V <sub>GS</sub> @ $R_L = 100 \text{ k}\Omega$ , 105 kHz 120 |

| Figure 6.22. $S_1$ and $S_2 V_{DS}$ waveforms for $V_{in} = 40 V$ and $2 k\Omega$ @ 105 kHz120                                                                           |

| Figure 6.23. S <sub>1</sub> and S <sub>2</sub> V <sub>DS</sub> , and I <sub>PFC</sub> waveforms for V <sub>in</sub> = 35 V and 100 k $\Omega$ @ 100 kHz121               |

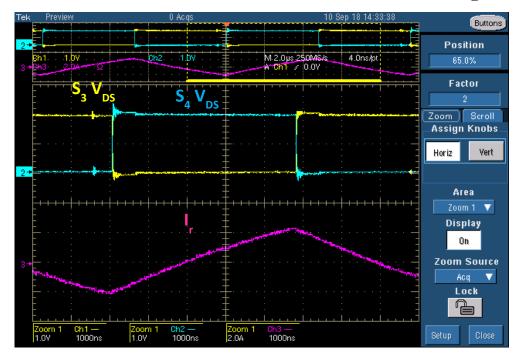

| Figure 6.24. S <sub>3</sub> and S <sub>4</sub> V <sub>DS</sub> and I <sub>r</sub> waveforms for V <sub>in</sub> = 40 V and 2 k $\Omega$ @ 105 kHz121                     |

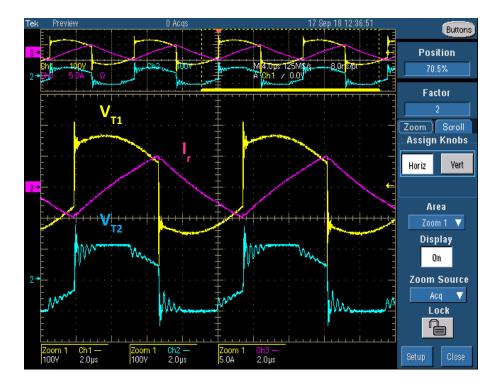

| Figure 6.25. $V_{T1}$ , $V_{T2}$ , and $I_r$ waveforms for $V_{in} = 80$ V and 2 k $\Omega$ @ 105 kHz122                                                                 |

| Figure 6.26. $V_{T1}$ , $V_o$ , and $I_r$ waveforms for $V_{in} = 50$ V and 2 k $\Omega$ @ 105 kHz123                                                                    |

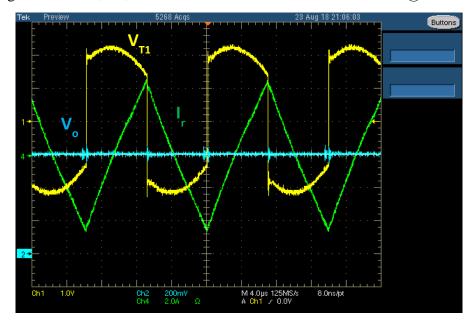

| Figure 6.27. $V_{T1}$ , $V_o$ , and $I_r$ waveforms for $V_{in} = 60$ V and 250 $\Omega$ @ 72 kHz123            |

|-----------------------------------------------------------------------------------------------------------------|

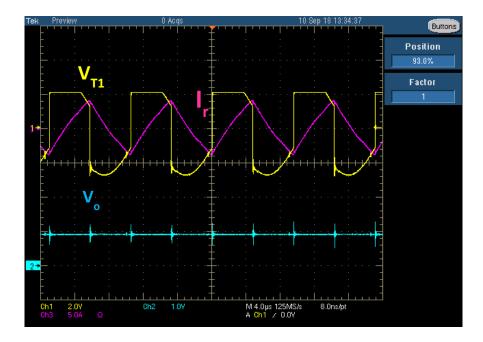

| Figure 6.28. $V_{T1}$ , $V_o$ , and $I_r$ waveforms for $V_{in} = 70$ V and 2 k $\Omega$ @ 105 kHz124           |

| Figure 6.29. $V_{T1}$ , $V_o$ , and $I_r$ waveforms for $V_{in} = 120$ V and $100 \text{ k}\Omega$ @ 105 kHz124 |

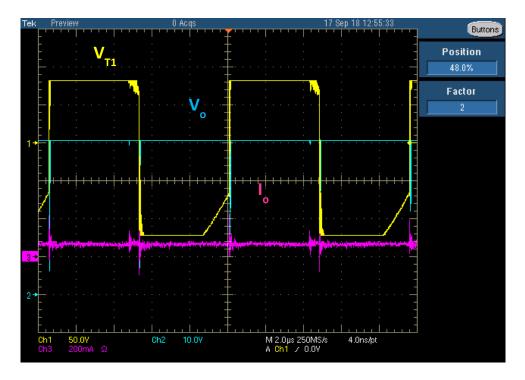

| Figure 6.30. $V_{T1}$ , $V_o$ , and $I_o$ waveforms for $V_{in} = 80$ V and 2 k $\Omega$ @ 105 kHz125           |

## LIST OF TABLES

| Table 2.1. Comparison between four different SST designs.          | .16 |

|--------------------------------------------------------------------|-----|

| Table 3.1. Converter component values.                             | .34 |

| Table 4.1. Selected soft magnetic materials properties parameters. | .63 |

| Table 4.2. Example 1 (25 kHz) transformer specifications.          | .70 |

| Table 4.3. Example 2 (100 kHz) transformer specifications.         | .75 |

| Table 5.1. ePWM output signals.                                    | .96 |

| Table 6.1. Constructed experimental prototype main parts.          | 111 |

#### LIST OF PUBLISHED PAPERS

IEEE published conference papers:

- A. M. Elrajoubi, K. George and S. S. Ang, "Design and analysis of a new GaN-based AC/DC topology for battery charging application," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 2018, pp. 2959-2964.

- A. M. Elrajoubi and S. S. Ang, "Design and evaluation of a high-current gate driver circuit for six paralleled 1.2kV 36A SiC MOSFETs," 2018 IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL, USA, 2018, pp. 1-8.

- A. M. Elrajoubi, K. George and S. S. Ang, "Investigation of a new GaN AC/DC topology for battery charging application," *2018 IEEE Texas Power and Energy Conference (TPEC)*, College Station, TX, USA, 2018, pp. 1-6.

- A. Elrajoubi, S. S. Ang and A. Abushaiba, "TMS320F28335 DSP programming using MATLAB Simulink embedded coder: Techniques and advancements," 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, 2017, pp. 1-7.

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 GaN Based Converters' Features**

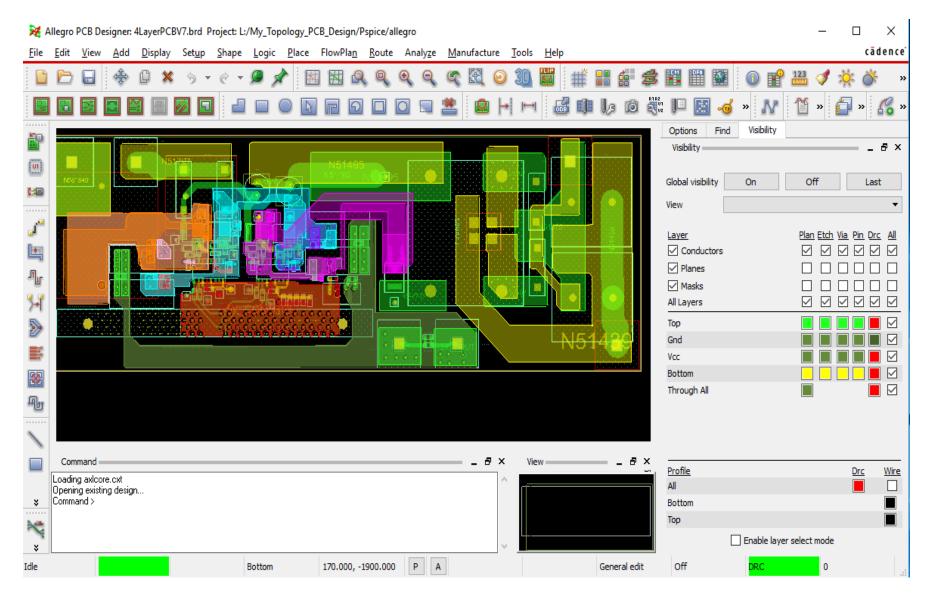

Gallium Nitride (GaN) technology offers higher performance converters with faster switching speed due to reduced switching losses, and so reducing heat sink requirement. Very high efficiency is achievable using GaN technology due to very low on resistance, superior fast switching ability, and zero reverse recovery losses. GaN devices can realize high current capability up to 100's Amperes. It is proven that GaN systems offer extreme benefits to switching power supply designs. Totem-pole power factor correction (TP-PFC) circuit can be improved for closed-loop control, and obtaining higher efficiency AC/DC converters topology. So, an efficient power supply converter can be developed using GaN devices for low and medium power applications. In this research, a low-power battery charging application is proposed for the investigated GaN converter topology which is designed for 120 Vac to 48Vdc/60Vdc conversion, operating at 100 kHz in the 1.3–1.5 kW range. Figure 1.1 shows the advantageous of GaN properties compared to silicon and gallium arsenide (GaAs) [1-1].

Figure 1.1. The Advantageous of GaN properties compared to Si and GaAs [1-1].

Totem-pole bridgeless PFC rectifier is now emerging using 600 V GaN devices as a preferred front end rectifier for low power applications. Since the GaN reverse recovery charge is much less than that of Si MOSFET, hard switching operation is still appropriate. GaN high-electron-mobility-transistor (HEMT) high-frequency capability and significant system advantages have been shown to dramatically reduce the volume of the boost inductor and the electromagnetic interference (EMI) filter. The switching frequency can be above 1 MHz for the totem-pole PFC rectifier, and verified solutions were addressed for significant high frequency issues [1-2]. An efficient power supply converter can be developed using GaN devices for low and medium power applications. High efficiency converters are achievable using GaN technology, superior fast switching ability, and zero reverse recovery losses. GaN device characteristics are especially suitable for hard switched diode bridgeless applications, such as PV inverters, and related totem pole PFCs applications [1-2, 1-3, 1-4]. The cascode GaN HEMT is very suitable for high-frequency operation as zero-voltage switching (ZVS) turn on has been achieved [1-5].

GaN technology is significant for several reasons:

- GaN devices have high energy gap and so yield significantly higher electric field for GaN over Si or SiC. Therefore it allows less channel length of a GaN device which results in smaller on resistance and conduction loss [1-4].

- 2) Low input and output capacitances reduce switching losses in hard-switched converters and allows higher switching frequency in hard-switched and soft-switched converters.

- 3) Near-zero reverse recovery charge losses in hard-switched, half-bridge converters enables new topologies such as totem-pole PFC.

- Greatly reduced switching loss reduces transition period and allows faster switching speeds while reducing or eliminating heat sink.

- 5) It is an ideal solution for applications requiring high frequency, high-efficiency operation in a small form factor [1-3].

- 6) Recently the highest current rating for 650 V GaN HEMTs has exceeds 90 A [1-4].

- 7) GaN HEMTs has been applied to many traditional power converters topologies, and higher efficiency with high power density was demonstrated. A 600 V, 10 kW E-Mode GaN based three phase inverter with targeted power density of 17 kW/L was built and under test [1-4].

The depletion mode (D-Mode) GaN devices are used since the cascode structure can yield positive gate-to-source threshold voltage of 2.1 V [1-4]. The switching losses and sizes of switching power supplies can be reduced by 50% through low on-resistance and high frequency capability of the GaN HEMTs. Hard switching losses occur at both turn-on and turn-off periods of the power switching devices. The total power loss ( $P_{LOSS}$ ) for Si device is the sum of the following losses multiplied by the switching frequency.

$$P_{LOSS} = f x \left( E_{OFF} + E_{RR} + E_{OSS} + E_G + E_{ON} \right)$$

(1.1)

where,

$E_{OFF}$  = Turn-off switching energy loss.  $E_{RR}$  = Diode recovery energy loss.  $E_{OSS}$  = Output charge energy loss.  $E_G$  = Gate charge energy loss.

$E_{ON}$  = Turn-On switching energy loss.

The use of enhancement GaN HEMTs reduces switching losses and increases switching frequency to yield smaller size and improve the performance. GaN HEMTs have near-zero reverse recovery charge ( $Q_{RR}$ ) due to their absence of the minority carriers. The output capacitance ( $C_{OSS}$ ) and its associated charge ( $Q_{OSS}$ ) is also smaller because GaN HEMTs are physically smaller than MOSFETs of comparable  $R_{DS(ON)}$ . Both  $V_{GS}$  and  $Q_G$  are low for GaN HEMTs, as such  $E_G$  is negligible. GaN HEMT can yield 2.5 ns rise time for a hard-switched

device. This switching speed is much faster than that of the silicon power MOSFETs. Softswitching transitions of less than 5 ns are achievable, as parasitic capacitances and inductances are no longer ignored in the GaN HEMT based switching converters [1-3, 1-5].

### **1.2 Solid-State Transformer Functionalities**

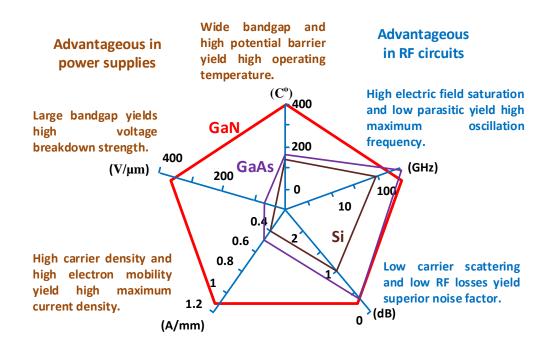

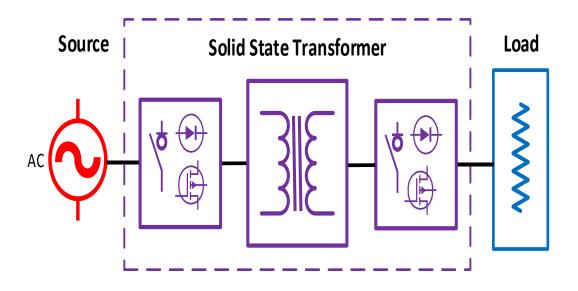

Solid-State Transformer (SST) is a key component with promising features. SST has reduced weight and size and can be utilized for niche applications, with additional voltage regulation and voltage disturbance rejection functionality. It allows bidirectional power flow control, and SST is very convenient for many applications since better automation and control algorithm can be developed. Also, SST will help gaining more advantages for power quality, storage management, and power flow control in addition to the reduction of volume and weight compared to the traditional transformer [1-6, 1-7]. Therefore, utilizing the advantages of SST operation and functionalities to develop a GaN-based power supply topology for low power applications will be investigated. SST demonstrated good structure as it enables superior controllability. Figure 1.2 shows the basic structure of the solid-state transformer topologies. It has been concluded that dual active bridge (DAB) converter with PWM control offers extended ZVS range and improved efficiency at light load [1-8]. Four topologies for SST were investigated in [1-9] by considering cost, number of semiconductor devices, efficiency, and specifications.

Figure 1.2. Solid State Transformer structure [1-6].

The advantages and disadvantages of the selected SST topologies (full or half bridges DAB, Boost Based topology) for emerging distribution system applications were highlighted and compared. The main advantages and promising features of SST are [1-6, 1-7, 1-8]:

- Voltage regulation and voltage disturbance rejection.

- It allows bidirectional power flow control.

- Easier for voltage and frequency adaption.

- Possible reactive power compensation.

- Reduced weight and size potentially.

- Fault current limiting.

- Overall power quality improvement.

- Power factor correction.

The proposed and designed GaN AC/DC topology in this dissertation will be operated to achieve these aforementioned SST features and functionality advantages for low power applications. The basic objective is to pursue an intelligent power electronic transformer to develop the GaN AC/DC converter which achieves SST control features.

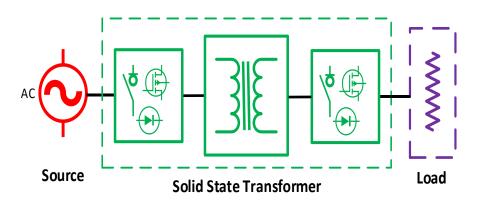

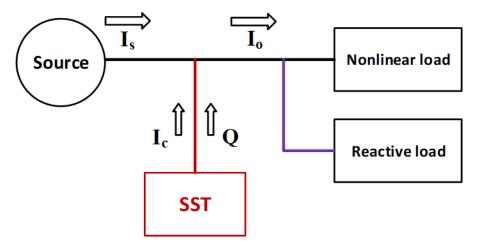

Figure 1.3. SST power management for DC microgrid [1-10].

It is stated and presented in some literatures that the core part of the SST is the isolated DC/DC converter which is operated at a medium or high frequency. Figure 1.3 demonstrates the structure of SST which was adopted in [1-10] as an interface between the distribution grid, AC loads, and DC loads. Therefore SST allows not only AC to AC conversion, but also AC to DC conversions to interact between different grids.

#### **1.3 Dissertation Motivation**

With the current advancement in wide bandgap power semiconductors, power conversion with high-frequency (HF) link has been found very convenient for many applications, and it gives an opportunity to improve power density and efficiency as well as reducing the weight, volume, and cost. GaN technology is significant as GaN HEMT devices have smaller ON resistances and thus smaller conduction losses. Also, near-zero reverse recovery charge losses in hard-switched converters makes totem-pole PFCs feasible [1-2, 1-4]. A 1 MHz bridgeless totem-pole PFC rectifier has been designed in [1-2] using the low-loss 600 V GaN device, which provides a great front-end converter for low power applications. Bridgeless totem-pole PFC has shown several advantages like higher efficiency, less parts count, and bidirectional power flow operation [1-11].

On the other hand, the current doubler rectifier (CDR) reduces RMS current on the transformer secondary (half of the load current, so less copper losses) and the output voltage ripple is reduced. Therefore it is widely used for high current, low voltage applications. Also, CDR yields smaller leakage inductance to obtain ZVS condition [1-12, 1-13], it has bi-directional energy control capability, and offers better thermal performance (good heat dissipation); also, CDR transient response performance is improved [1-14]. Reference [1-15] designed an optimized telecom phase shift full-bridge DC–DC converter with CDR for 400  $V_{dc}$  input voltage, while the proposed topology in this dissertation utilizes the 120  $V_{ac}$  line input and half

bridge series resonant converter (SRC), which is easier to control and yields half of the voltage to the transformer primary side. Most importantly, converter losses in series resonant converters are significantly reduced because of zero-voltage- and zero-current-switching operation of all switching devices compared to hard-switching full-bridge and half-bridge topologies, which increases the overall efficiency of this proposed topology. The combination of the reduced SRC losses with the alleviation of losses in the transformer secondary winding, due to the CDR, makes the proposed topology an attractive high-efficiency AC/DC low power converter.

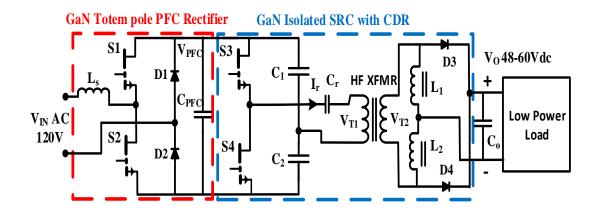

The main target is to develop a power supply converter utilizing SST functionalities for few kilowatts application by using GaN switches and fully utilize their high temperature, high frequency, and low loss characteristics. It is recommended to continue the research on this particular idea in order to solve some issues related to the complex control of these topologies and to achieve the objective of high efficiency and small size with acceptable cost switching converters. The proposed converter will enhance and maintain power quality supply for low power application as well as produce a power supply topology with higher reliability and minimum cost spent in manufacturing it. The proposed GaN power converter shown in Figure 1.4 yields a close-to-unity power factor, low harmonic content (<5%), and high efficiency power supply for 120Vac to 48Vdc/60Vdc conversion, operating at 100 kHz in the 1.3–1.5 kW range.

Figure 1.4. The proposed GaN AC/DC converter topology.

This converter topology includes a totem-pole power-factor-correction (TP-PFC), a half bridge series resonant converter (SRC), and a current doubler rectifier (CDR) at the secondary of the high frequency transformer. The equivalent averaged model for the proposed and investigated topology, state space equations, and transfer function are presented in this dissertation. Analysis, simulation, and experimental prototype are conducted to demonstrate the feasibility of the proposed power supply topology for low power application. MATLAB/Simulink is used for simulation and controller design and to analyze the stability of the proposed switching converter system.

#### **1.4 Dissertation Objectives**

The main objectives for this dissertation research are:

- Investigate, simulate, propose and design a new GaN-based power supply topology utilizing solid-state transformer for low power applications, particularly by combining the advantages of PFC and SRC with CDR utilizing the superior switching characteristics of GaN devices and the reduced size and cost of HF transformer.

- Analyze and synthesize the operation of the proposed GaN topology to yield higher efficiency converter due to zero-voltage- and zero-current-switching operation of all switching devices, GaN performance, and CDR advantages.

- Design the controller algorithm to achieve close to unity power factor, low harmonic contents, and high efficiency power supply for 120V<sub>ac</sub> to 48V<sub>dc</sub>/60V<sub>dc</sub> conversion, operating at 100 kHz in the 1.3–1.5 kW range. Then implement the control algorithm with TMS320F28335 digital signal processor (DSP).

- Design, fabricate and experimentally investigate a scaled down 4-layer printed circuit board (PCB) prototype to demonstrate the feasibility of the designed GaN AC/DC converter topology and its operation.

#### **1.5 Dissertation Organization**

The literature review for the operation and topologies of solid-state transformer, resonant converters soft-switching, and GaN gate drivers design considerations will be covered in Chapter 2. Chapter 3 is about the theoretical operation concepts, modeling and simulation of the proposed GaN AC/DC topology. High-frequency transformer design is documented in Chapter 4. Then TMS320F28335 DSP programming and controller algorithm design are covered in Chapter 5. Experimental prototype results for the investigated GaN converter topology are presented in Chapter 6 with all PCB design and fabrication steps. Finally, the research conclusions and recommendations for future work are explained in Chapter 7.

### **1.6 References**

- [1-1] http://www.gansystems.com/why\_gallium\_nitride\_new.php

- [1-2] Z. Liu, F. C. Lee, Q. Li and Y. Yang, "Design of GaN-Based MHz Totem-Pole PFC Rectifier," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 4, no. 3, pp. 799-807, Sept. 2016.

- [1-3] http://www.ti.com/lsds/ti/power-management/gan-overview.page?DCMP=pwr GaN&HQS=sva-hvps-hpds-GaN-lp-en.

- [1-4] He Li, Chengcheng Yao, Lixing Fu, Xuan Zhang and Jin Wang, "Evaluations and applications of GaN HEMTs for power electronics," 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, 2016, pp. 563-569.

- [1-5] X. Huang, Z. Liu, Q. Li and F. C. Lee, "Evaluation and Application of 600 V GaN HEMT in Cascode Structure," in *IEEE Transactions on Power Electronics*, vol. 29, no. 5, pp. 2453-2461, May 2014.

- [1-6] X. She, X. Yu, F. Wang and A. Q. Huang, "Design and Demonstration of a 3.6-kV–120-V/10-kVA Solid-State Transformer for Smart Grid Application," in *IEEE Transactions* on *Power Electronics*, vol. 29, no. 8, pp. 3982-3996, Aug. 2014.

- [1-7] T. Zhao, G. Wang, J. Zeng, S. Dutta, S. Bhattacharya and A. Q. Huang, "Voltage and power balance control for a cascaded multilevel solid state transformer," *Applied Power Electronics Conference and Exposition (APEC), 2010 Twenty-Fifth Annual IEEE*, Palm Springs, CA, 2010, pp. 761-767.

- [1-8] C. Nan and R. Ayyanar, "Dual active bridge converter with PWM control for solid state transformer application," 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, 2013, pp. 4747-4753.

- [1-9] R. J. G. Montoya, A. Mallela and J. C. Balda, "An evaluation of selected solid-state transformer topologies for electric distribution systems," 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, 2015, pp. 1022-1029.

- [1-10] X. Yu, X. She, X. Zhou and A. Q. Huang, "Power Management for DC Microgrid Enabled by Solid-State Transformer," in IEEE Transactions on Smart Grid, vol. 5, no. 2, pp. 954-965, March 2014.

- [1-11] GS665BTP-REF rev170905 GaN Systems Reference Design "High Efficiency CCM Bridgeless Totem Pole PFC Design using GaN E-HEMT".

- [1-12] P. Jang and B. H. Cho, "Zero-voltage switching analysis of active-clamped forward converter with current-doubler rectifier," 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, 2015, pp. 253-258.

- [1-13] H. I. Hsieh, K. P. Huang and G. C. Hsieh, "Analysis and realization study of a 1-kW phase-shift full-bridge converter with current-doubler rectifier for battery charging," 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, 2016, pp. 439-444.

- [1-14] V. Beldjajev, I. Roasto and D. Vinnikov, "Analysis of current doubler rectifier based high frequency isolation stage for intelligent transformer," 2011 7th International Conference-Workshop Compatibility and Power Electronics (CPE), Tallinn, 2011, pp. 336-341.

- [1-15] U. Badstuebner, J. Biela, D. Christen and J. W. Kolar, "Optimization of a 5-kW Telecom Phase-Shift DC–DC Converter With Magnetically Integrated Current Doubler," in IEEE Transactions on Industrial Electronics, vol. 58, no. 10, pp. 4736-4745, Oct. 2011.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### **2.1 Introduction**

The theoretical fundamentals and concepts of solid-state transformer (SST) operation and topologies are described in this chapter. The resonant converters soft switching, and gallium nitride (GaN) gate drivers design considerations are also described. It is believed that energy crisis could be avoided by improving the necessary infrastructure for renewable energy sources and storage devices. Currently, there are many researches conducted to develop various technologies for the electric distribution system using power electronics as a key technology. It is expected to experience many developments in the near future for solid-state transformer (SST) market because of its advantages. SST can operate using medium and high frequency and its physical size and weight already have been reduced significantly. Using advanced semiconductor devices in addition to the essential diodes and transistors, SSTs become very flexible. So they should be fast switching and manipulate low, medium and high power levels. Also, they can exchange different forms of electric power by changing the voltage and the frequency. Therefore, they connect the power grid to the wind turbines and solar panels using DC and AC power converters. In addition, they utilize some control equipment to communicate with utility operators and consumers. The distributed power generation and smart grid applications are very promising technologies for solid-state transformers. SST size and weight reduction can be accomplished, while the efficiency of the entire electric power system can be improved. Moreover, the characteristic of being a solid-state device is very convenient for smart grid applications as better automation and control are possible [2-1].

In the low and medium voltage power distribution network, power quality (PQ) was affected by the fundamental reasons of PQ issues and the presence of renewable energy sources. There are many products which improved the power quality are serving the sensitive loads. Power electronics (PE) conversion technique is the main base for these important products [2-2]. Power quality solutions have been developed using power electronics systems such as uninterruptible power supply systems and active filters. These improvements are due to the significant decrease in cost, high reliability, and high-frequency switching semiconductors with low losses. Medium-voltage (MV) power distribution systems which were in the last few years dominated by electromechanical and electromagnetic technology are depending significantly on power electronics conversion techniques. Also, SST which is a high-frequency switched transformer and has extended functionality, as such, it is more economical to replace the typical power frequency distribution transformer. This PE transformer can operate on both AC MV input (single or three phase) or DC MV input. In addition it can enable balancing the loads and result in low harmonic distortions [2-2].

Power electronics transformer with high frequency is a "niche product" [2-2], and has higher functionality to serve the future power distribution systems. However, the costs and power losses are still challenges for the wide usage of SST. A medium-voltage distribution grid has been described in [2-2] which contains some DC subsystems and distributed resources, such as wind energy and fuel cell. More importantly the usage of power electronic converters to connect varies forms of electricity. More than fifteen years ago several preferred topologies of SSTs were discussed to replace the typical power frequency distribution transformer. Semiconductor switches with higher blocking capability, lower on state losses, higher switching speed and with smart integrated gate drivers are now available in the market [2-2]. However, SSTs were not popular due to unavailability of high-voltage high-frequency switching power semiconductor devices.

Electricity is generated by power generation plants, then it is transferred to the transmission lines and eventually to the distribution grids to feed the loads. In all these stages, the transformer is an essential part to step up/down the voltage to the desired usage values. Traditional power transformer has achieved high efficiency, but its size and weight are still relatively high and could be improved. Power electronic developments are presenting a very suitable technology to serve the electric power system. High-power and high-frequency converters have been involved in the power transmission and distribution system, especially in the applications related to the utilization of renewable power energy resources. SST was introduced in 1970 and was called the electronic transformer [2-3], while the concept of solidstate transformers or electronic transformers was firstly introduced in 1950 [2-4]. It was defined as an intelligent universal transformer since it is controlled by advanced intelligent controllers and can provide different forms of DC and AC voltages. Power switching devices have been developed to be used in power electronics applications to achieve higher efficiency. The basic structure of solid-state transformer is shown in Figure 2.1. It is clear that SST is containing power electronics converters working as rectifiers and inverters, and in between these there is a high-frequency (tens to hundreds of kHz) transformer to step the voltage up/down. SST is considered as a promising component with great advantages to improve the future electric grid and be a key part especially to help connecting to the new DC microgrid architecture.

Figure 2.1. Solid State Transformer configuration [2-3].

So basically SST is a power electronic converter connected to function as a transformer which is going to replace the traditional power transformer, hence, the volume and weight are significantly decreased. Moreover, SST can provide extra benefits to the distribution network by offering useful functions such as power flow control, protection monitoring, power factor correction, and voltage sag compensation [2-3]. Future electric power distribution systems highly depend on more penetration of power electronic converters, so all efforts to understand, analyze and control the subsystems interactions are significantly valuable. Nowadays there are significant improvements because of the advancements of power electronic converters in electrical power systems. These improvements are clear and very important parts for autonomous power systems, and smart grid components [2-5].

#### 2.2 Solid State Transformer Operation and Functionalities

Figure 2.2 shows the functional configuration of SST which is described as a power electronic converter that does much more than only voltage change (step up/down) task. SST is an important smart device for the electric distribution and delivery system to connect these different parties and transform the electric energy from one another through either AC or DC form [2-6]. It is not easy to implement this basic idea for SST, especially to obtain high efficiency and utilize additional benefits from the SST to the network. Efforts should be made to overcome the challenges for power electronic circuits to work properly in high-voltage and high-power applications. The design must be effective to ensure the reduction in size and weight since SST has extra elements like (control circuits, power devices, and heat sinks). There are many researches conducted to improve the design of SST, but still there is no standard could be followed. So it is important to review the literature and the outcomes of the previous works in order to help design SST for distribution networks considering its volume and efficiency [2-3].

Figure 2.2. SST functional configuration [2-6].

The efficiency of the traditional transformer is already high and it is difficult for power electronic converter to achieve a 97% efficiency. However, a lower efficiency can be compromised to achieve the other functions from SST. Currently, the highest efficiency of SSTs in distribution grid is between 96% and 98%, according to the power ratings [2-3]. By reducing the size and weight of the transformer, the costs of their transportation and the required space will be much less, then both the manufacturers and the customers would gain economic benefits. Special and appropriate design considering the thermal and insulation aspects is really valuable and challenging to obtain a small size high-voltage SST.

The future renewable electric energy delivery and management (FREEDM) system using distributed renewable energy resources (DRERs) and distributed energy storage devices (DESDs) is shown and explained in [2-6]. DRERs include wind, solar, hydro, and fuel cells, while DESDs means the equipment like batteries, hydrogen storage, and hybrid electric vehicles. SST is a fundamental and important element to achieve the suitable operation of this proposed FREEDM system.

Table 2.1 compares four different SST structures: universal and flexible power management (UNIFLEX), Electric Power Research Institute (EPRI), General Electric Global Research

(GE), and FREEDM [2-3]. Si power devices and multilevel converter topologies are used in UNIFLEX, EPRI, and FREEDM in the high-voltage rectifiers for their SSTs, to achieve VAR compensation and voltage sag compensation capabilities. The highest SST efficiency is that of GE because of the customized SiC MOSFET line frequency commutation in the high-voltage rectifier [2-3].

#### 2.3 Solid State Transformer Components and Topologies

High-voltage and high-frequency power devices are necessary for SST to be inserted into the distribution system which operate in voltages from 2.3 kV to 35 kV. Because of the switching loss limitations, silicon power devices (IGBT, IGCT, and ETO) are not able to operate at high switching frequencies. So the practical switching frequency is usually less than 1 kHz, which is not convenient for SST to obtain significant reduction in size and weight. One of the possible solutions for high-voltage is to series connect low voltage power devices. For future high-voltage applications, wide band gap materials (like 4H-silicon carbide) will be adopted. SiC material can operate at high temperature since it has a larger energy band gap.

| SST Functionality        | UNIFLEX | EPRI    | GE   | FREEDM  |

|--------------------------|---------|---------|------|---------|

| Eliminates oil           | No      | Yes     | Yes  | Yes     |

| VAR compensation         | Yes     | Yes     | No   | Yes     |

| Voltage sag compensation | Yes     | Yes     | No   | Yes     |

| Voltage regulation       | Yes     | Yes     | Yes  | Yes     |

| Harmonic isolation       | Yes     | Yes     | Yes  | Yes     |

| Common DC link           | No      | Yes     | Yes  | Yes     |

| Energy storage option    | Yes     | Yes     | Yes  | Yes     |

| Fault isolation          | Yes     | Yes     | Yes  | Yes     |

| Bidirectional power flow | Yes     | No      | Yes  | Yes     |

| Control complexity       | Complex | Average | Easy | Complex |

| Efficiency               | Average | Average | High | Average |

Table 2.1. Comparison between four different SST designs [2-3].

Also, the larger breakdown electric field enable SiC devices to switch at higher voltage, higher current, and higher frequencies. These features are suitable for SST applications. High voltage SiC devices have been investigated and it was found that 10 kV SiC MOSFETs are the best option for applications with higher than 20 kHz. However, IGBTs can operate for higher current than MOSFET at lower frequencies. For compact SST SiC MOSFETs are preferred for voltages less than 10 kV, rather than SiC IGBT, SiC GTO, and SiC ETO because of their switching speed [2-3].

SST replaces the 50/60 Hz transformer with a high-frequency transformer as the main circuit component in SST. There are several challenges needed to be investigated carefully to obtain the desired requirements for SST operation. First, to achieve high saturation flux density and less losses in the transformer, the magnetic material should be critically selected. Secondly, the efficiency at high frequencies is affected by the transformer winding method, so it should be studied sufficiently. Also, high-voltage and high-power applications must consider the thermal breakdown issue when designing the SST. Finally, for small SST size and when oil is eliminated the insulation requirement for SST is very difficult for high voltage applications. Many magnetic materials may be considered like: ferrite, nanocrystalline, silicon steel, and amorphous. Optimization must be done to evaluate these magnetic materials by considering cost, permeability, losses, and saturation flux density. In general nanocrystalline core is the best option to satisfy the efficiency and power density requirement as well. Recent studies mentioned that the efficiency can be improved up to 99.99% for different core types. Solenoidal and coaxial windings are the two main structures of transformers. Solenoidal structure is more popular and preferred because of its advantages in more flexible design, lower cost, and easier manufacture. In SST it is much more difficult to design the thermal and insulation aspects since it is desired to have less space and oil-free operation [2-3].

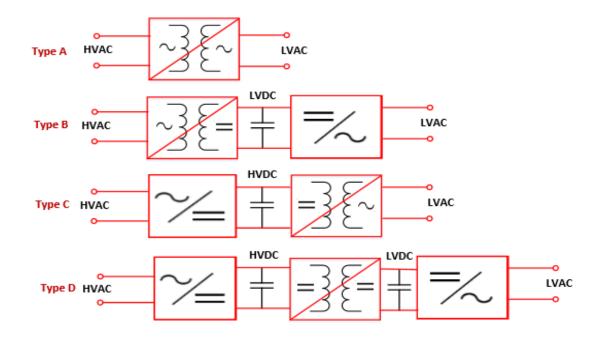

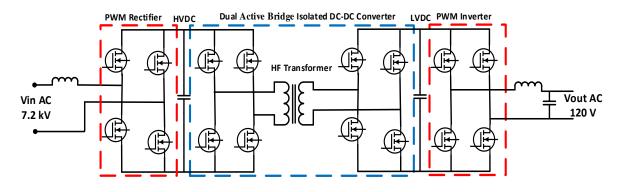

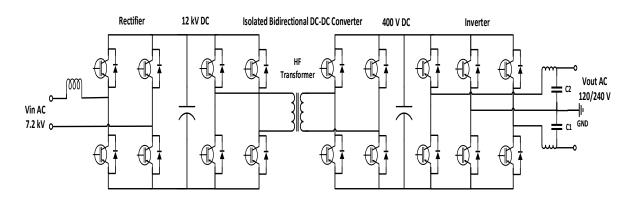

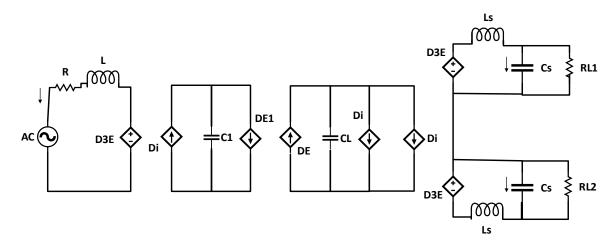

Figure 2.3 shows four different configurations for SST. Type A is a one stage converter that contains the high-frequency isolation transformer. Type B and Type C are both two-stage conversion topologies but they contain different DC voltage levels. Type D has a rectifier to produce HVDC, then there is a high-frequency isolation transformer to give LVDC, and finally, the inverter to provide the LVAC output. Type D is the most used topology for SST field application [2-3]. The future distribution grid requires an intelligent controller to provide the electric energy to the loads and fulfill the stability requirement. SST can present an essential element since it uses power electronic converters to integrate all those renewable sources with storage devices. The idea of energy router is mentioned in [2-6] and it is mainly built on SST and how it enables the plug-and-play of renewable resources, distributed storages, and loads. A 15 kV SiC MOSFET single phase SST circuit topology in which there are three voltage levels (7.2 kV AC, 120/240 V AC, and 400 V DC) is depicted in [2-6]. Figure 2.4 shows the three stages SST structure. This contains PWM rectifier, dual active bridge (DAB) DC/DC converter, and PWM inverter. As can be noticed the isolation in DAB is through a high-frequency transformer.

Figure 2.3. Topology classification of SST [2-3].

Figure 2.4. Three stages SST configuration [2-7].

This topology is providing HVDC, LVDC, and transforming from 7.2 kV AC to 120/240 V AC. This feature has enabled the SST superior controllability. It has been concluded in [2-7] that DAB converter with PWM control has extended ZVS range to improve its efficiency at very light load [2-7]. Figure 2.5 shows the basic topology of a single-phase SST which presents the values of the voltages at all stages, while figure 2.6 presents its average model [2-8].

Figure 2.5. Gen-I SST single phase topology [2-8].

Figure 2.6. Single phase Gen-I SST average model [2-8].

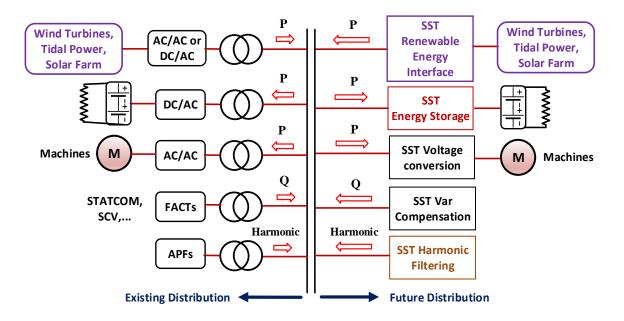

#### 2.4 Solid State Transformer Applications and Emerging Research Directions

Figure 2.7 shows the desired future distribution network by adopting SSTs instead of the 60 Hz transformer and the necessary converters for renewable energy resources and traction system. Obviously, SST can operate as an isolated AC/DC topology with power electronics converters operating at high frequency. Figure 2.8 presents the concept of using SST for reactive power compensation and harmonics filtering [2-5]. The SST plays a significant role for traction systems and it can effectively replace the low-frequency transformer and some power electronics converters since it is able to regulate the voltage as presented in [2-10].

Figure 2.7. Future distribution network utilizing SSTs [2-3, 2-9].

Figure 2.8. SST compensates reactive power and filters harmonics [2-9].

It is recommended to continue the research in order to solve some issues related to the complex control of SST topologies and to achieve the objectives of high-efficiency and small size with acceptable cost. For future work, the stability issues need more investigations, and it is recommended to gain more experience in future distribution systems utilizing SST. Power electronics technology is entering the electric power grid especially for the penetration of renewable energy resources. In addition SST is promising to function like an energy router to integrate smart grid applications [2-3].

The microgrid concept has been studied recently, and by adopting power electronic technology it can be proposed to replace the bulky and uncontrollable networks and solve some power quality issues [2-10]. As can be seen from Figure 2.7 and explained in [2-9], the SST can interface both the DC and AC grids in the distribution network. An interleaved configuration topology has been suggested in [2-4] for high-voltage applications to reduce the number of SiC MOSFETS and their switching losses.

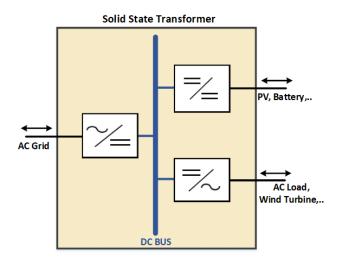

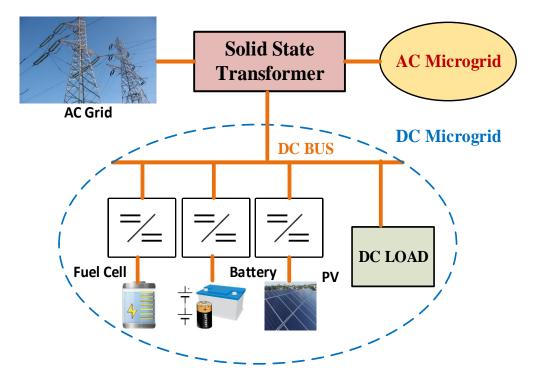

The TMS312F28335 digital signal processor (DSP) is used for the experimental prototype. Experimental and simulation results showed the feasibility of proper SST operation for the proposed system [2-4]. Figure 2.9 shows the diagram to adopt SST in a DC Microgrid [2-11]. This proposed system concerns the DC load and DC renewable energy sources (PV, fuel cell, and battery) with the advantages of SST to operate the system. It is confirmed that SST has many useful features and it can work bi-directionally. When the microgrid provides more power than the loads' demand, the extra power will be re-distributed to the utility grid, and vice versa. The battery can take in or give the energy according to its state of charge (SOC) while the PV and fuel cell are only alternative sources [2-11]. SST can be utilized as a smart plugand-play interface to exchange the electricity among different subsystems, so it is the key enabling technology for the distribution system and smart grid.

Figure 2.9. SST for DC Microgrid [2-10].

FREEDM system diagram has been described in [2-6, 2-9, 2-12] and it shows the fundamental concept for using SST to provide 120V AC and 400V DC from the 12 kV AC bus. Intelligent energy management (IEM) is performing energy flow control using SST and distributed grid intelligence (DGI) unit. So IEM will fulfill the bidirectional power flow and distributed power management. The local loads are supplied initially from DRER and DESD, and if the demand is more than the supply then SST will draw the needed electricity from the grid. Also, when the loads are less than the supply SST will send the extra power to the grid [2-12]. SST technology needs an efficient high-voltage and high-frequency transformer. FREEDM research center has compared and reviewed the theoretical concepts for the magnetic core materials, and winding layout options. They reported the test results for the 6.7 kVA high voltage high-frequency transformer prototype [2-8]. SST is established and implemented in [2-13] for the smart grid to improve the system performance and integrate the alternative energy sources and storage devices. So eventually mitigate the energy crisis by developing an efficient electric network infrastructure for controlling the entire system.

### 2.5 Resonant Conversion Concepts and Soft Switching Operation

Zero-voltage-switching and zero-current-switching topologies are designed to gain higher efficiency power conversion by minimizing switching losses for the switches. That is typically obtained by utilizing the resonant operating condition for the switching frequency. Resonant converters are different from typical PWM converters as they include resonant L-C networks and their voltage and current sinusoidal waveforms are depending on each subinterval switching period conditions. By changing the switching frequency, the magnitudes of the resonant tank current and voltage can be controlled as desired for the topology under consideration [2-14]. The resonant switch concepts are not discussed in this chapter, which are thoroughly explained in the literature for several resonant converters. In these resonant switch topologies the PWM converter has switch network contains resonant elements, therefore they result in a resonant switch network with the properties of the original PWM converter. Common quasi-square wave methods for soft switching converters achieves zero voltage switching without having high voltage stress on the transistor [2-14].

The main feature of the resonant converters is minimizing the switching loss by the mechanism of turning on and off transitions at the zero crossing of the waveforms. This phenomena has been widely implemented in switching converters to let the transistors switching transitions coincide the zero crossing of the voltage and current waveforms. Typically for a full-bridge topology, zero-voltage-switching (ZVS) occur when it operates below resonance, while zero-current-switching (ZCS) occur at above resonance operation. These are because the circuit causes the transistor current become zero before it turns off, likewise it causes the voltage across the transistor to be zero before the turn-on transition is done. In addition, diodes reverse-recovery charge losses are mitigated by ZVS, whereas ZCS is applied to eliminate current tailing and stray inductances switching losses. ZVS is preferred when diode reverse-recovery losses and semiconductor output capacitors are causing major switching losses [2-14].

Considering the efficiency and losses in any switching converter is an important step during the equivalent circuit operation analysis. Many references described the sinusoidal approximation to investigate and analyze the operation of resonant converters. Sinusoidal approximation approach is very useful to have great insight for many properties of the resonant converters such as the output characteristics, load current dependence, and zero-voltage and zero-current-switching transitions. It is accurate for large Q factor and close to resonant switching frequency operation [2-14].

Zero-voltage-switching has been discussed and analyzed in [2-15] for an isolated forward converter with current doubler rectifier (CDR) on the secondary side of the high frequency transformer. CDR has been utilized for high-current low-voltage applications due to the smaller current in the transformer secondary windings, and CDR can maintain ZVS with its reduced leakage inductance [2-15]. Soft switching has been achieved for the analyzed topology by adjusting the desired leakage inductance of the CDR topology to meet the resonant frequency condition.

### **2.6 GaN Gate Drivers Design Considerations**

Gate driver circuitry is designed to provide the required voltage and current levels to drive a transistor in a safe and an efficient way. At the same time it protects the digital signal processor (DSP) from voltage spikes or any noise as well as operates to minimize conduction and switching losses. The gate capacitance is charged as fast as possible to minimize the switching time, hence, a driver IC with sufficient current capability should be used. Also the stray inductances in drive circuits have to be eliminated or minimized to avoid the presence of unwanted oscillation during device turn-off. This is typically employed using a four terminals (Kelvin) connection to have the transistor source connected separately to the gate driver terminals. Meanwhile, the length of all unshielded terminals should be minimized to reduce the

over-voltages at turn-off transients. Therefore, the layouts of gate drivers and power electronic converter printed circuit boards are crucial to mitigate the effects of parasitic inductances and reduce switching noises to obtain satisfactory operation [2-16, 2-17].

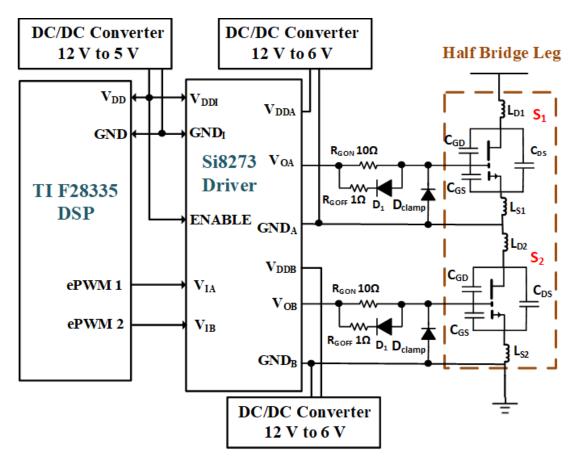

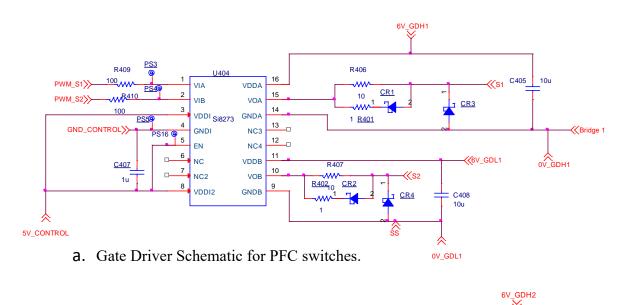

Bootstrap capacitance effect for high speed non isolated gate driver circuitry is addressed in [2-18] for driving the top switch of a half-bridge converter, or for driving two MOSFETs in a synchronous buck converter. The voltage level of the gate pulse is shifted to switch on the upper switch by using a bootstrap bias circuit comprising of a bootstrap capacitor, diode, and resistor. The bootstrap capacitor is charging when the bottom switch is ON and it is discharging to turn the top-switch off. Bootstrap circuits use a single pulse width modulation (PWM) input signal to drive both the low-side and high-side switches through the charge storage bootstrap capacitor, resistor and diode [2-16, 2-18]. However, in this dissertation, gate driver isolation is obtained by utilizing separated power supply for each opto-coupler and gate driver IC of any of the GaN transistors. Silicon Labs half-bridge isolated gate drivers for E mode GaN FETs (SI8273) are used to drive both the top and bottom switches of the proposed AC/DC converter. The SI8273 isolated gate driver has several features such as high dv/dt immunity, low propagation delay, and high DC bus voltage level (1500 V) [2-19].

A quasi-Kelvin source connection is employed for the GaN transistors and their gate drivers' return loops to eliminate the deleterious effects of common source inductances. It is called quasi-Kelvin because the GaN HEMTs used in this research work have only three terminals. As such, a small amount of source parasitic inductance is present within the package. Also minimizing the layout parasitics for the prototype is taken into account for the 4 layer printed-circuit-board (PCB). Designing an appropriate layout is extremely critical for GaN converters to minimize the noise and avoid any false switching for the GaN transistors, which is a high priority. It has been recommended in [2-20] for driving GaN switches to minimize noise coupling, mitigate gate ringing or oscillations, and control Miller effects by optimizing the 4

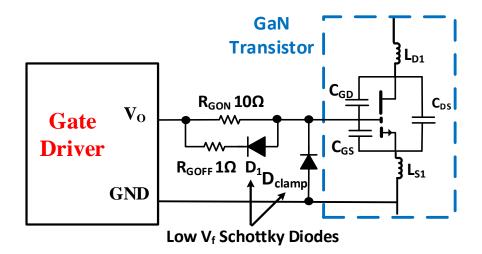

layer PCB layout. Therefore, 4 layer PCB has been designed for the converter described in Chapter 6. It is essential to apply quasi-Kelvin connections for the driver return loops, and minimize the pull-down and pull-up loops by locating the components (gate resistances, capacitors, and diodes) as close as possible to minimize the parasitics. Also, isolating and preventing gate, drain, and control traces from overlapping among each others are performed [2-20]. The converter utilizes gate resistors of 10  $\Omega$  for R<sub>G(ON)</sub>, and 1  $\Omega$  for R<sub>G(OFF)</sub> with low forward voltage Schottky diode as depicted in Figure 2.10. Gate-to-source spike clamping diodes are employed in the gate drivers circuitry.

Figure 2.10. The gate driver for the GaN half-bridge structure.

# 2.7 Conclusion

SST is considered one of the most significant enabling technologies for future electric systems especially to the distribution system. This chapter presents an overview of SST previous researches and to provide useful information to review this technology and its main features.

Also, it presents several application topics of SST in the future smart electrical system. In addition, interfacing SST with some renewable energy sources is addressed. The literature for SST has been reviewed and summarized to provide the fundamental background and concepts. Different topologies have been applied to operate SST for different applications and different voltage levels. Several selected SST topologies have been reviewed and evaluated for the desired functionalities. SST offers extra benefits to the distribution grid by enabling significant function such as power flow control, power factor correction, voltage sag compensation, and significant reduction in volume and weight. Moreover, resonant conversion concepts and soft switching operation for solid state converters have been briefly addressed. Finally, GaN gate drivers design considerations for the proposed converter are highlighted and described.

## **2.8 References**

- [2-1] http://www.marketsandmarkets.com/Market-Reports/solid-state-transformer-market-774.html

- [2-2] L. Heinemann and G. Mauthe, "The universal power electronics based distribution transformer, an unified approach," 2001 IEEE 32nd Annual Power Electronics Specialists Conference (IEEE Cat. No.01CH37230), Vancouver, BC, 2001, pp. 504-509 vol.2.

- [2-3] X. She, R. Burgos, G. Wang, F. Wang and A. Q. Huang, "Review of solid state transformer in the distribution system: From components to field application," 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, 2012, pp. 4077-4084.

- [2-4] A. Abedini and T. Lipo, "A novel topology of solid state transformer," 2010 1st Power Electronic & Drive Systems & Technologies Conference (PEDSTC), Tehran, Iran, 2010, pp. 101-105.

- [2-5] D. Boroyevich, I. Cvetković, D. Dong, R. Burgos, F. Wang and F. Lee, "Future electronic power distribution systems a contemplative view," 2010 12th International Conference on Optimization of Electrical and Electronic Equipment, Basov, 2010, pp. 1369-1380.

- [2-6] A. Q. Huang, M. L. Crow, G. T. Heydt, J. P. Zheng and S. J. Dale, "The Future Renewable Electric Energy Delivery and Management (FREEDM) System: The Energy Internet," in Proceedings of the IEEE, vol. 99, no. 1, pp. 133-148, Jan. 2011.

- [2-7] C. Nan and R. Ayyanar, "Dual active bridge converter with PWM control for solid state transformer application," 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, 2013, pp. 4747-4753.

- [2-8] P. Tatcho, H. Li, Y. Jiang and L. Qi, "A Novel Hierarchical Section Protection Based on the Solid State Transformer for the Future Renewable Electric Energy Delivery and Management (FREEDM) System," in IEEE Transactions on Smart Grid, vol. 4, no. 2, pp. 1096-1104, June 2013.

- [2-9] X. She and A. Huang, "Solid state transformer in the future smart electrical system," 2013 IEEE Power & Energy Society General Meeting, Vancouver, BC, 2013, pp. 1-5.

- [2-10] X. Yu, X. She, X. Zhou and A. Q. Huang, "Power Management for DC Microgrid Enabled by Solid-State Transformer," in IEEE Transactions on Smart Grid, vol. 5, no. 2, pp. 954-965, March 2014.

- [2-11] F. Wang, X. Lu, W. Wang and A. Huang, "Development of distributed grid intelligence platform for solid state transformer," 2012 IEEE Third International Conference on Smart Grid Communications (SmartGridComm), Tainan, 2012, pp. 481-485.

- [2-12] Y. Du, S. Baek, S. Bhattacharya and A. Q. Huang, "High-voltage high-frequency transformer design for a 7.2kV to 120V/240V 20kVA solid state transformer," IECON 2010 - 36th Annual Conference on IEEE Industrial Electronics Society, Glendale, AZ, 2010, pp. 493-498.

- [2-13] X. Yu, X. She, X. Ni and A. Q. Huang, "System Integration and Hierarchical Power Management Strategy for a Solid-State Transformer Interfaced Microgrid System," in IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 4414-4425, Aug. 2014.

- [2-14] Erickson and Maksimovic, Fundamentals of Power Electronics, Kluwer, 2nd edition, 2000.

- [2-15] P. Jang and B. H. Cho, "Zero-voltage switching analysis of active-clamped forward converter with current-doubler rectifier," 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia), Seoul, 2015, pp. 253-258.

- [2-16] A. M. Elrajoubi and S. S. Ang, "Design and evaluation of a high-current gate driver circuit for six paralleled 1.2kV 36A SiC MOSFETs," 2018 IEEE Power and Energy Conference at Illinois (PECI), Champaign, IL, USA, 2018, pp. 1-8.

- [2-17] Mohan, N., Undeland, T.M., Robbins, W.P.: 'Power electronics: converters, applications, and design' 3th edition (John Wiley & Sons, 2007).

- [2-18] Fairchild AN-6076 Application Notes, "Design and Application Guide of Bootstrap Circuit for High-Voltage Gate-Drive IC" @ 2008 Fairchild semiconductor Corporation.

- [2-19] Silicon Labs Si827x Isolated Gate Drivers Data Sheet available at:

- https://www.silabs.com/documents/public/data-sheets/Si827x.pdf

- [2-20] GaN Systems, GN001 Application Guide, Design with GaN Enhancement mode HEMT, Updated on Feb. 28 2018.

### **CHAPTER 3**

### SIMULATION AND MODELING OF THE PROPOSED GaN TOPOLOGY

# **3.1 Introduction**