University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

12-2018

# Automatic Performance Optimization on Heterogeneous Computer Systems using Manycore Coprocessors

Chenggang Lai University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Computer and Systems Architecture Commons, Graphics and Human Computer Interfaces Commons, OS and Networks Commons, Power and Energy Commons, and the Systems Architecture Commons

#### Citation

Lai, C. (2018). Automatic Performance Optimization on Heterogeneous Computer Systems using Manycore Coprocessors. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3060

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

## Automatic Performance Optimization on Heterogeneous Computer Systems using Manycore Coprocessors

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

by

Chenggang Lai Shandong University Bachelor of Science in Electronic Engineering, 2012 University of Arkansas Master of Science in Computer Engineering, 2014

## December 2018 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council

Miaoqing Huang, Ph.D. Dissertation Director

John Gauch, Ph.D. Committee Member

Merwin Gordon Beavers, Ph.D. Committee Member Xuan Shi, Ph.D Committee Member

#### Abstract

Emerging computer architectures and advanced computing technologies, such as Intel's Many Integrated Core (MIC) Architecture and graphics processing units (GPU), provide a promising solution to employ parallelism for achieving high performance, scalability and low power consumption. As a result, accelerators have become a crucial part in developing supercomputers. Accelerators usually equip with different types of cores and memory. It will compel application developers to reach challenging performance goals. The added complexity has led to the development of task-based runtime systems, which allow complex computations to be expressed as task graphs, and rely on scheduling algorithms to perform load balancing between all resources of the platforms. Developing good scheduling algorithms, even on a single node, and analyzing them can thus have a very high impact on the performance of current HPC systems. Load balancing strategies, at different levels, will be critical to obtain an effective usage of the heterogeneous hardware and to reduce the impact of communication on energy and performance. Implementing efficient load balancing algorithms, able to manage heterogeneous hardware, can be a challenging task, especially when a parallel programming model for distributed memory architecture.

In this paper, we presents several novel runtime approaches to determine the optimal data and task partition on heterogeneous platforms, targeting the Intel Xeon Phi accelerated heterogeneous systems.

©2018 by Chenggang Lai All Rights Reserved

## Acknowledgements

I would like to extend my thanks to my thesis committee, especially my advisor Dr. Miaoqing Huang for providing the tools necessary for my research.

## Contents

| 1 | Intr | oduction                                                                          | 1      |  |  |  |

|---|------|-----------------------------------------------------------------------------------|--------|--|--|--|

| 2 | Bac  | Background                                                                        |        |  |  |  |

|   | 2.1  |                                                                                   | 5<br>5 |  |  |  |

|   |      |                                                                                   | 5      |  |  |  |

|   |      |                                                                                   | 7      |  |  |  |

|   | 2.2  |                                                                                   | 9      |  |  |  |

|   | 2.3  |                                                                                   | 9      |  |  |  |

|   |      | 1 E                                                                               | 9      |  |  |  |

|   |      | 2.3.2 GPU                                                                         |        |  |  |  |

|   |      | 2.3.3 MIC                                                                         |        |  |  |  |

|   | 2.4  | Programming models                                                                |        |  |  |  |

|   |      | 2.4.1 MPI+CPU                                                                     |        |  |  |  |

|   |      | 2.4.2 MPI+GPU                                                                     |        |  |  |  |

|   |      | 2.4.3 MIC Native mode                                                             |        |  |  |  |

|   |      | 2.4.4 MIC offload mode                                                            |        |  |  |  |

|   |      |                                                                                   |        |  |  |  |

| 3 |      | ly of parallel programming models with Intel MIC coprocessors 1                   |        |  |  |  |

|   | 3.1  | Introduction                                                                      |        |  |  |  |

|   | 3.2  | Intel MIC architecture and programming models                                     |        |  |  |  |

|   | 3.3  | Experiment setup                                                                  |        |  |  |  |

|   |      | 3.3.1 Benchmarks                                                                  |        |  |  |  |

|   |      | 3.3.2 Experiment Platform                                                         |        |  |  |  |

|   | 3.4  | Experiments and results on a single device                                        |        |  |  |  |

|   |      | 3.4.1 Scalability on a single MIC processor                                       |        |  |  |  |

|   |      | 3.4.2 Performance comparison of single devices                                    |        |  |  |  |

|   | 3.5  | Experiments and results using multiple MIC processors                             |        |  |  |  |

|   |      | 3.5.1 Comparison among five execution modes                                       |        |  |  |  |

|   |      | 3.5.2 Experiments on the MPI@MIC_Core+OpenMP execution mode 3                     |        |  |  |  |

|   |      | 3.5.3 Experiments on the Offload-1 execution mode                                 |        |  |  |  |

|   |      | 3.5.4 Experiments on the distribution of MPI processes                            |        |  |  |  |

|   |      | 3.5.5 Hybrid MPI vs native MPI                                                    | 7      |  |  |  |

|   | 3.6  | Related work                                                                      | 8      |  |  |  |

|   | 3.7  | Conclusions                                                                       | 9      |  |  |  |

| 4 | Tow  | ards Optimal Task Distribution on Computer Clusters with Intel MIC Coproces-      |        |  |  |  |

|   | sors | 4                                                                                 | 1      |  |  |  |

|   | 4.1  | Introduction                                                                      | 1      |  |  |  |

|   |      | The Benchmark: Sparse coding                                                      | 3      |  |  |  |

|   |      | Parallelization using MIC                                                         | 8      |  |  |  |

|   | 4.4  | Results and discussion                                                            | 9      |  |  |  |

|   |      | 4.4.1 Performance scalability of the native modes                                 | 0      |  |  |  |

|   |      | 4.4.2 Performance improvement of dynamic task distribution on a single MIC card 5 | 1      |  |  |  |

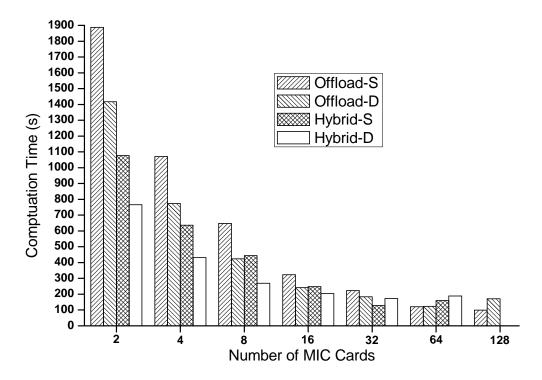

|   |       | 4.4.3  | Performance improvement of dynamic task distribution on multiple MIC        |

|---|-------|--------|-----------------------------------------------------------------------------|

|   | 4.5   | Conclu | cards                                                                       |

| _ |       |        |                                                                             |

| 5 |       |        | ce Optimization on Intel MIC Through Load Balancing 55                      |

|   | 5.1   |        | uction                                                                      |

|   | 5.2   |        | d Work                                                                      |

|   | 5.3   | •      | umming models                                                               |

|   |       | 5.3.1  | Native Model (MPI-based implementation)                                     |

|   |       | 5.3.2  | Symmetric Model                                                             |

|   |       | 5.3.3  | Hybrid Model                                                                |

|   | 5.4   | Data I | Distribution Model (DDM)                                                    |

|   |       | 5.4.1  | DDM Analysis                                                                |

|   |       | 5.4.2  | Determining profiling size                                                  |

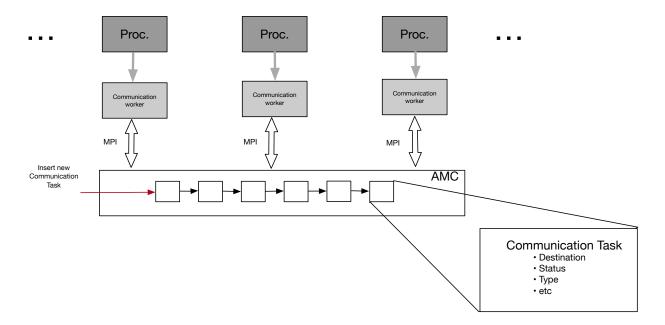

|   |       | 5.4.3  | Asynchronous Management Controller(AMC) 64                                  |

|   |       | 5.4.4  | Asymmetric scheduling                                                       |

|   | 5.5   | The in | plementation of Game of Life by different models on heterogeneous clusters  |

|   |       | with N | IIC coprocessors                                                            |

|   | 5.6   | Result | and discussion                                                              |

|   | 5.7   | Accele | erating Urban Sprawl Simulation                                             |

|   |       | 5.7.1  | Urban Sprawl Simulation                                                     |

|   |       | 5.7.2  | Implementation and Results                                                  |

|   | 5.8   | Conclu | usion                                                                       |

| 6 | A 114 | omotio | Performance Improvement on Heterogeneous Platforms: A Machine Learn-        |

| U |       |        | Approach 78                                                                 |

|   | 6.1   |        | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ $$ |

|   | 6.2   |        | round and Overview                                                          |

|   | 0.2   | 6.2.1  | Related work   80                                                           |

|   |       | 6.2.2  | Problem Scope                                                               |

|   |       | 6.2.3  | Motivating Examples                                                         |

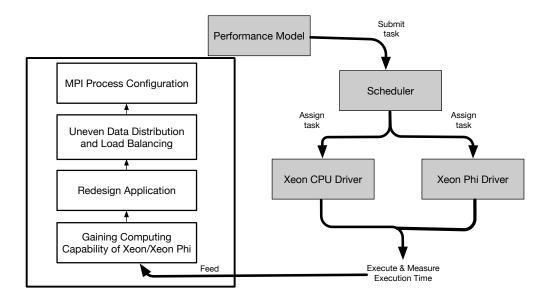

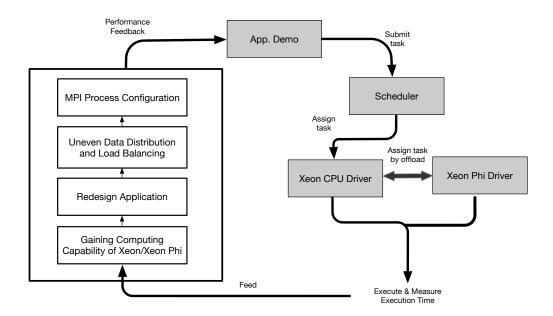

|   |       | 6.2.4  | Overview         86                                                         |

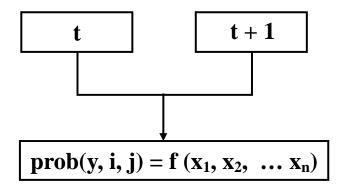

|   | 6.3   |        | tive Modeling                                                               |

|   | 0.5   | 6.3.1  | Generating training data                                                    |

|   |       | 6.3.2  | Generating training data                                                    |

|   |       | 6.3.3  | Training model         91                                                   |

|   |       | 6.3.4  |                                                                             |

|   | 61    |        | 1 9                                                                         |

|   | 6.4   | 1      |                                                                             |

|   |       | 6.4.1  | Experiment setup                                                            |

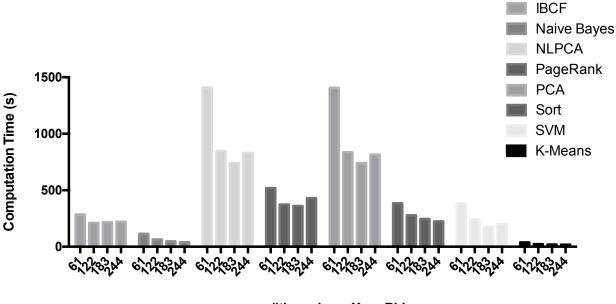

|   | ( =   | 6.4.2  | Result                                                                      |

|   | 6.5   | Conclu | usion                                                                       |

| 7 Conclusion |     |             |                |

|--------------|-----|-------------|----------------|

|              | 7.1 | Summary     | <del>)</del> 9 |

|              | 7.2 | Future Work | )0             |

| References   |     |             | 01             |

## List of Figures

| 2.1  | Serial Processing.                                                              | 6  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Parallel Processing.                                                            | 6  |

| 2.3  | Parallel Processing.                                                            | 7  |

| 2.4  | Spectrum of Programming Models                                                  | 11 |

| 2.5  | The software architecture of Intel Xeon Phi coprocessor.                        | 12 |

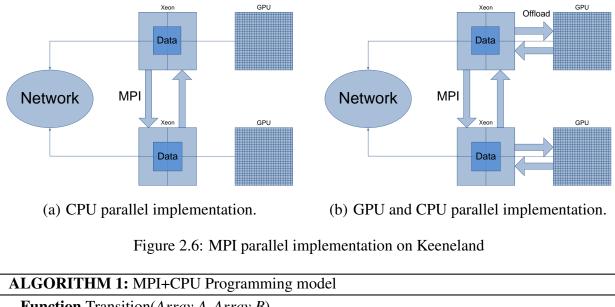

| 2.6  | MPI parallel implementation on Keeneland                                        | 13 |

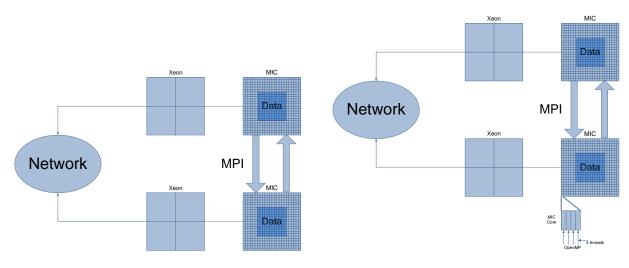

| 2.7  | MIC native parallel implementation on Beacon                                    | 15 |

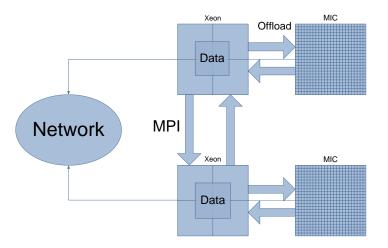

| 2.8  | Offload parallel implementation on Beacon                                       | 16 |

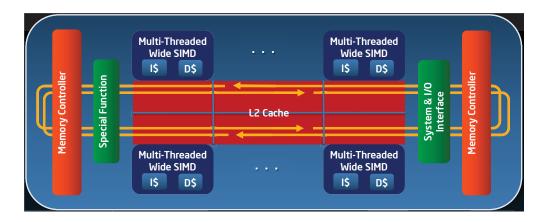

| 3.1  | The architecture of Intel Xeon Phi coprocessor (MIC) [5]                        | 19 |

| 3.2  | Data partition and communication in two benchmarks.                             | 21 |

| 3.3  | Pseudocode of Kriging interpolation                                             | 23 |

| 3.4  | Pseudocode of Game of Life                                                      | 24 |

| 3.5  | Performance of Kriging interpolation on a single MIC processor                  | 27 |

| 3.6  | Performance of Game of Life on a single MIC processor.                          | 28 |

| 3.7  | Performance of Kriging interpolation on single devices                          | 29 |

| 3.8  | Performance of Kriging interpolation on multiple MICs                           | 32 |

| 3.9  | Performance of Game of Life on multiple MIC processors                          | 33 |

| 3.10 | Performance of Game of Life                                                     | 35 |

| 3.11 | Performance of Game of Life with different configurations.                      | 36 |

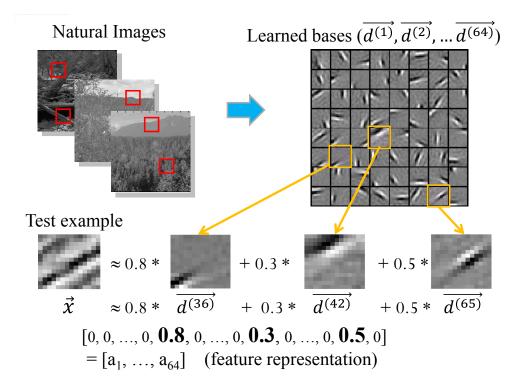

| 4.1  | Illustration of sparse coding applied to natural images.                        | 44 |

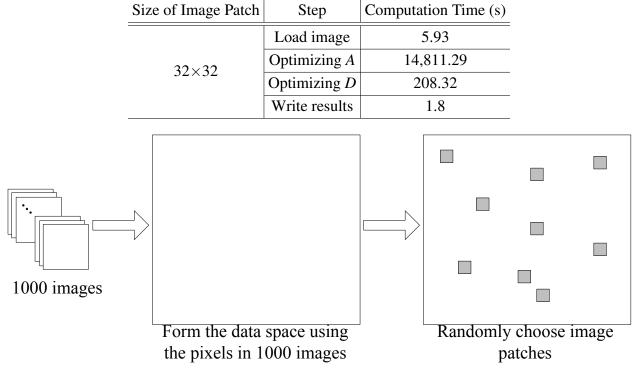

| 4.2  | The process to form the source data space and randomly choose several data sets | 45 |

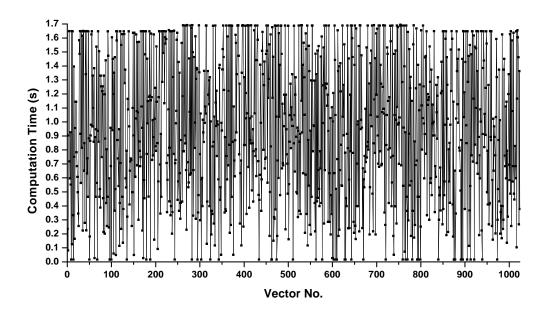

| 4.3  | The computation times of 1,024 coefficient vectors                              | 46 |

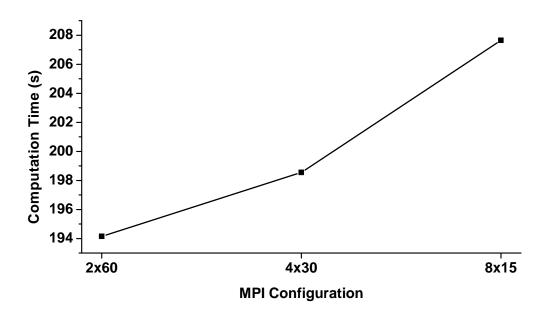

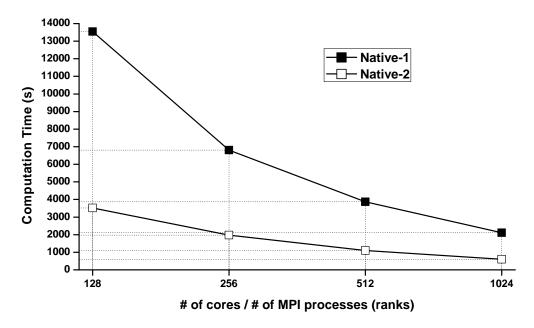

| 4.4  | Performance scalability under the native execution modes                        | 50 |

| 4.5  | Performance comparison on single MIC                                            | 51 |

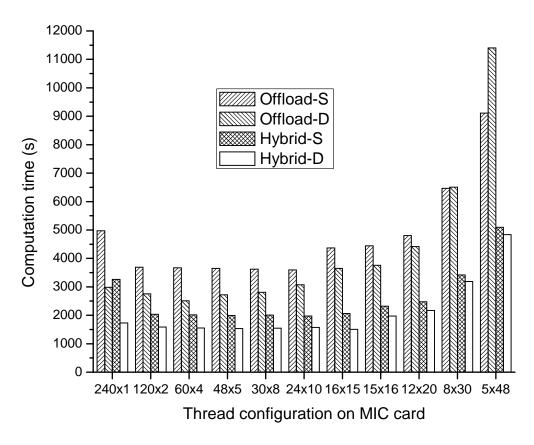

| 4.6  | Performance comparison on multiple MICs.                                        | 53 |

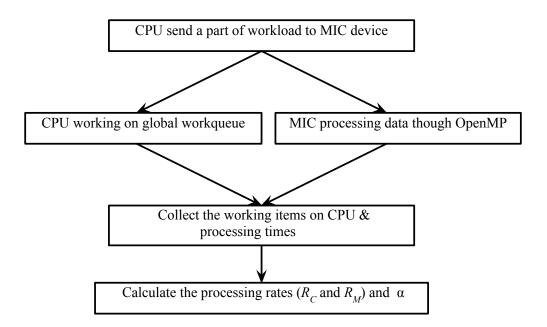

| 5.1  | DDM workflow.                                                               | 60 |

|------|-----------------------------------------------------------------------------|----|

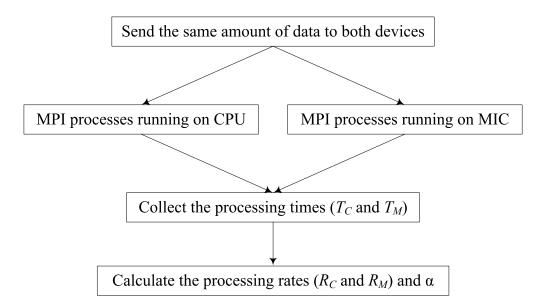

| 5.2  | The process to calculate $\alpha$ in the DDM model                          | 61 |

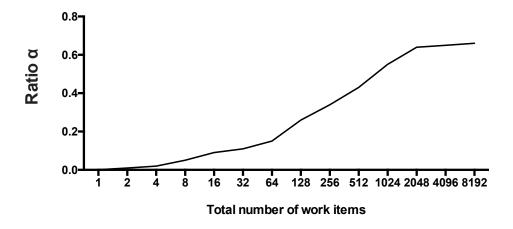

| 5.3  | Changes in ratio $\alpha$ with increasing number of work items              | 63 |

| 5.4  | AMC Structure.                                                              | 65 |

| 5.5  | Symmetric model                                                             | 66 |

| 5.6  | The process to calculate $\alpha$ in the Asymmetric model                   | 67 |

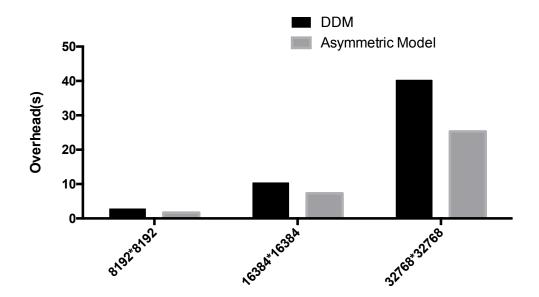

| 5.7  | The overhead to calculate $\alpha$ in the DDM and Asymmetric model          | 68 |

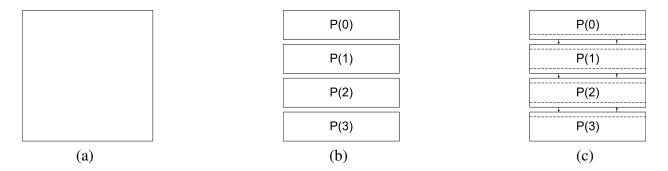

| 5.8  | Data distribution among MPI processes                                       | 68 |

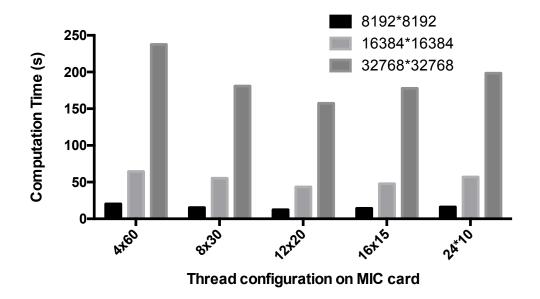

| 5.9  | Performance comparison among different MPI/OpenMP configurations            | 70 |

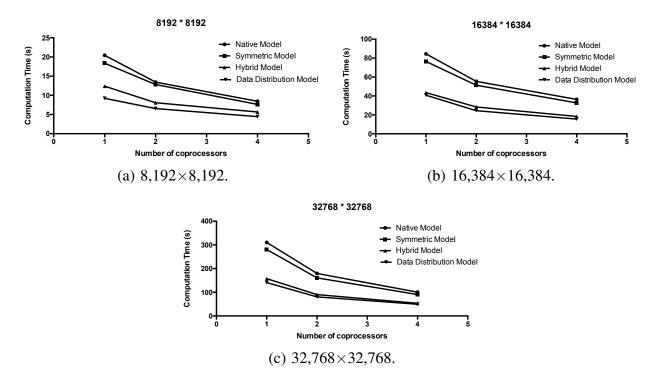

| 5.10 | Performance of Game of Life on three different configurations               | 71 |

| 5.11 | Calibration of the global probability surface from sequential land use data | 73 |

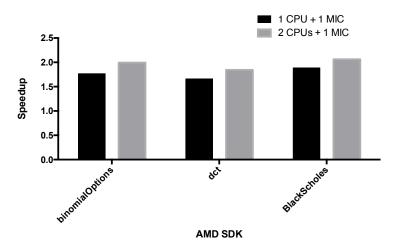

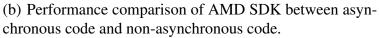

| 6.1  | Asynchronous code example.                                                  | 82 |

| 6.2  | Running times for different numbers of threads [62]                         | 83 |

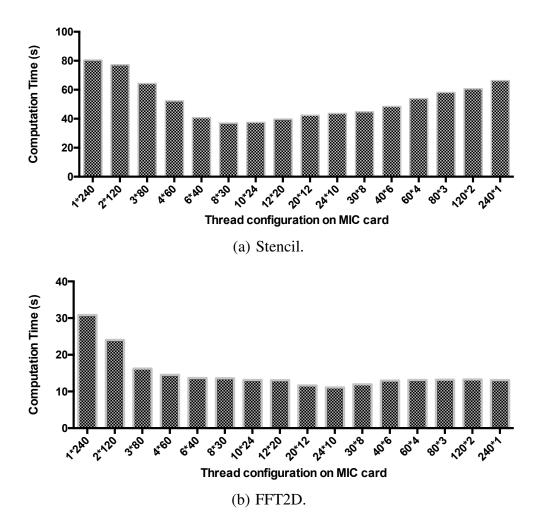

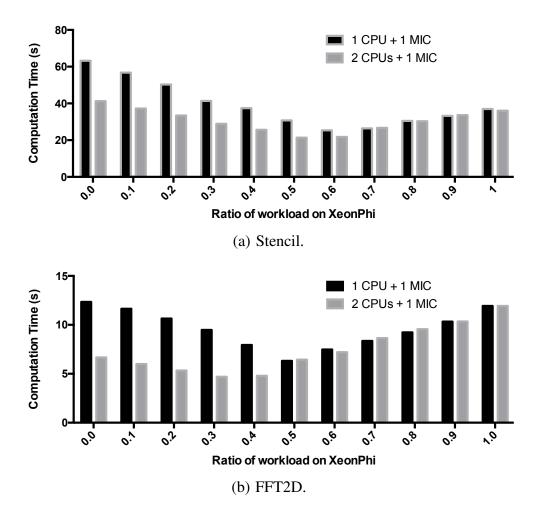

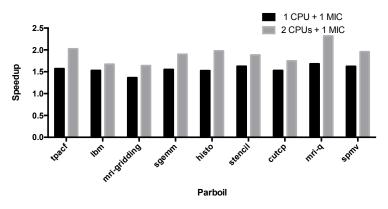

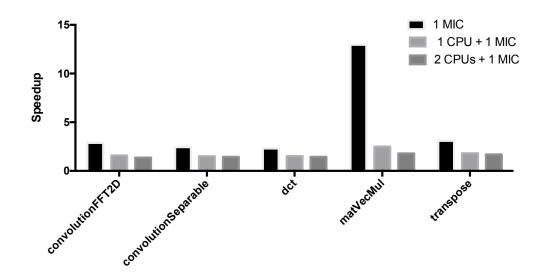

| 6.3  | Computation time of Stencil and FFT2D under different thread configurations | 84 |

| 6.4  | Performance based on different ratios of workload distribution              | 85 |

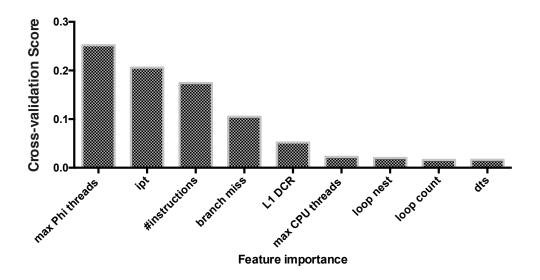

| 6.5  | Feature importance according to Forward Feature Selection and Random Forest | 90 |

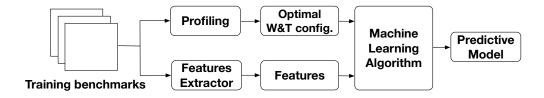

| 6.6  | Training process (W&T: workload distribution and thread configuration)      | 91 |

| 6.7  | Predicting process (W&T: workload distribution and thread configuration).   | 92 |

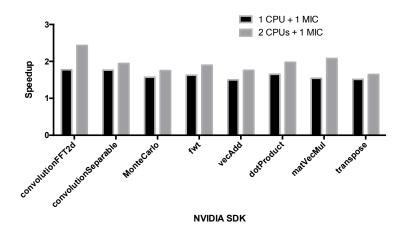

| 6.8  | Comparison of overall performance.                                          | 94 |

| 6.9  | Performance difference between the worst and the best thread configurations | 95 |

## List of Tables

| 3.1 | Performance of Kriging interpolation on a single MIC processor (unit: second)       | 26 |

|-----|-------------------------------------------------------------------------------------|----|

| 3.2 | Performance of Game of Life on a single MIC processor (unit: second)                | 27 |

| 3.3 | Performance of Kriging interpolation on single devices (unit: second)               | 28 |

| 3.4 | Performance of Game of Life on single devices                                       | 29 |

| 3.5 | Performance of Kriging interpolation under various execution modes                  | 30 |

| 3.6 | Performance of Game of Life under various execution modes                           | 31 |

| 3.7 | Performance of Game of Life using MPI@MIC_Core+OpenMP execution mode                | 34 |

| 3.8 | Performance of Game of Life (32,768 $\times$ 32,768) using Offload-1 execution mode | 35 |

| 4.1 | Computation time of four steps in a sequential implementation                       | 45 |

| 4.2 | Thread configuration in multiple-MIC implementations                                | 52 |

| 5.1 | Performance of Game of Life using a single MIC coprocessor(unit: second)            | 72 |

| 5.2 | Performance of Game of Life (unit: second)                                          | 72 |

| 5.3 | Performance of Urban Sprawl Simulation (unit: <u>second</u> )                       | 75 |

| 6.1 | Benchmarks list.                                                                    | 87 |

| 6.2 | Nested Thread Configuration.                                                        | 88 |

| 6.3 | Seleted Features.                                                                   | 90 |

| 6.4 | Compare to the different learning models.                                           | 97 |

### **Terms and Definitions**

- MIC Many Integrated Core architecture. A manycore processor architecture by Intel.

- CPU Central Processing Unit.

- GPU Graphic Processing Unit.

- MPI Message-passing Interface. A library for parallel programming on computer clusters.

- **OpenMP** Open Multi-Processing. A library that supports multi-platform shared memory multiprocessing programming.

- CUDA Compute Unified Device Architecture. A parallel programming language on GPU.

## **List of Published Papers**

This dissertation is based on the following four papers:

**Chapter 3 Comparison of Parallel Programming Models on Intel MIC Computer** Cluster Chenggang Lai, Zhijun Hao, Miaoqing Huang, Xuan Shi, and Haihang You in Proceedings of Fourth International Workshop on Accelerators and Hybrid Exascale Systems (AsHES) as part of IPDPS, May 2014. **Towards Optimal Task Distribution on Computer Clusters with Intel MIC** Chapter 4 Coprocessors Chenggang Lai, Miaoqing Huang, and Genlang Chen in Proceedings of 2015 International Conferences on High Performance Computing and Communications (HPCC), August 2015. Chapter 5 Performance Optimization on Intel Xeon Phi Through Load Balancing Chenggang Lai, Xuan Shi, and Miaoqing Huang in Proceedings of 24th International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA), July 2018. Chapter 6 **Performance Improvement on Heterogeneous Platforms: A Machine** Learning Based Approach

Chenggang Lai, Yirong Chen, Xuan Shi, Miaoqing Huang, Genlang Chen International Conference on Computational Science and Computational Intelligence, Dec. 2018.

#### Chapter 1

#### Introduction

High-performance computing is critical to process large volumes of data in the big data area. With the advancement of technologies, high-resolution data become available. For example, satellites can generate high-quality images with a resolution less than 0.5 meter. However, high-resolution data bring lots of challenges and complexities. Traditional desktop-based software have become inefficient and impossible to process large-scale data. While the computer provides a large memory for data processing, some software has limitations to usage of computer memory.

People has to partition the source data into many parts for analyzing. Given the growing quantity of available data and finite resources to analyze them, it is expected that data can be exploited effectively for timely delivery of accurate information and for knowledge discovery. High performance computing (HPC) can allow people to solve complicated big data problems in various regions, such as engineering, science and business. Many top supercomputers are hybrid systems including both multicore CPUs and accelerators. Performance optimization mechanisms are critical for large-scale applications to achieve the best performance on these hybrid systems. These techniques include optimal workload distribution between the host processors and the accelerators, overlapping computation and communication to reduce the communication overhead, among others. As a part of high-performance computing, accelerators are becoming popular. Compared with traditional CPUs, accelerators can provide an orders-of-magnitude improvement in performance. Many computer architectures have been implemented. They provide good platforms to employ parallelism for achieving performance and scalability.

Emerging computer architectures and advanced computing technologies, such as Intel's Many Integrated Core (MIC) Architecture [5] (brand-named Xeon Phi) and graphics processing units (GPUs) [28], provide a promising solution to employ parallelism for achieving high performance, scalability and low power consumption. The combination of host processors and accelerators<sup>1</sup>, such as GPUs and Intel Xeon Phi coprocessors, has been applied in many cases to achieve orders of magnitude performance improvement.

With the development of graphic processing unit (GPU), it is becoming normal to use GPU as a modified form of stream processor for general purposes. GPU can get several orders of magnitude higher performance than CPU when processing massive vector operations. Therefore, high performance computers that are based on GPUs become a significant role in large scale modeling. GPUs are typically used as accelerators in high-performance computer clusters. However, it should be clear now that GPUs are designed as numeric computing engines, and they will not perform well on some tasks on which CPUs are designed to perform well. If different threads in a warp(parallel units) need to do different things, all threads will compute a logical predicate and several predicated instructions. This is called warp divergence. All threads execute conditional branches, so execution cost is sum of both branches. Warp divergence can lead to a big loss of parallel efficiency. Another problem are arising in learning and development on domain-specific-languages (DSLs) of GPU. For example, CUDA, implemented by NVIDIA, is a DSL for parallel programming on GPU. A  $40 \times$  speedup can be achieved in comparison to CPU solutions, but a  $11 \times$  learning curve is needed on CUDA study.

Intel MIC provides another option for augmenting the computer clusters for high performance and low power consumption. The MIC has demonstrated the high performance, the scalability, and the high memory bandwidth. The current Intel MIC architecture has up to 61 processing cores. These cores are connected through a high-speed ring bus. Because every core is a low-weight classic processor, the MIC can support traditional parallel programming models, such as OpenMP and MPI. The Xeon Phi coprocessors typically co-exist with multicore CPUs, such as Intel Xeon processors, in a heterogeneous computer platform. One of classic programming models on such multicore/manycore heterogeneous architectures is to use host processors to manage the execution context while the computation is offloaded to the accelerators. Effectively leverag-

<sup>&</sup>lt;sup>1</sup>In this work, we use accelerator and coprocessor interchangeably.

ing such platforms not only achieves high performance and good scalability, but also increases the energy efficiency. Although it is easy to implement application on MIC, traditional parallel programming models has their own bottlenecks.

The heterogeneous platform provides the potential for high performance and energy efficiency, but the classic offload model on GPU or MIC platforms leaves the host processors unutilized. This means this approach does not take advantage of the computing capacity of the host processors and is likely to give away too much performance potential of the whole system. Asynchronous data transfer and computation have been proposed as a solution to decrease the hostdevice<sup>2</sup> communication cost and to increase the utilization of host processors [19, 34]. In asynchronous mode, the host processor sends workload to the accelerator. Then the host processor continues the execution of other workload until it is requested to wait for a kernel running on the accelerator to finish. In this case, both host processors and accelerators can work in parallel to undertake a computation task.

Ideally, the scheduler should partition work between host processors and accelerators automatically and efficiently without any input from the application developer. However, it is hard to determine the right data partition and task parallelism on heterogeneous platforms given a new application. There are some evidences showing that choosing the right configurations, i.e., the number of for-loops needed to be parallelized and the number of concurrent tasks in for-loops, has a significant impact on the application's performance on Xeon Phi coprocessors [23, 14, 33]. However, exhaustive manual search would be ineffective to find the optimal workload partition between host CPU and the accelerator and the optimal task distribution on accelerators, because the range of the possible configurations is huge. Therefore, we need to design a technique that is capable of automatically determining the optimal configurations for any application in an efficient manner. This thesis focuses on asynchronous calculation and efficiently utilizing all available resources to achieve performance improvement, targeting the Xeon Phi coprocessor. Besides, a novel runtime approaches to determining the optimal data and task partition automatically would be proposed in

<sup>&</sup>lt;sup>2</sup>host: host processor; device: accelerator/coprocessor.

this work.

The thesis consists of 7 chapters. It is organized based on the specific accelerators that are used to accelerate some applications. The first two chapters give an introduction and related work to high-performance computing and accelerators. A detailed study of parallel programming models are discussed in Chapter 3. Chapter 4 and Chapter 5 demonstrate performance optimization through load balancing by using different methods. A novel runtime approach to determining the optimal data and task partition automatically is discussed in Chapter 6. Chapter 7 concludes the whole thesis.

#### Chapter 2

#### Background

#### 2.1 Parallel Programming

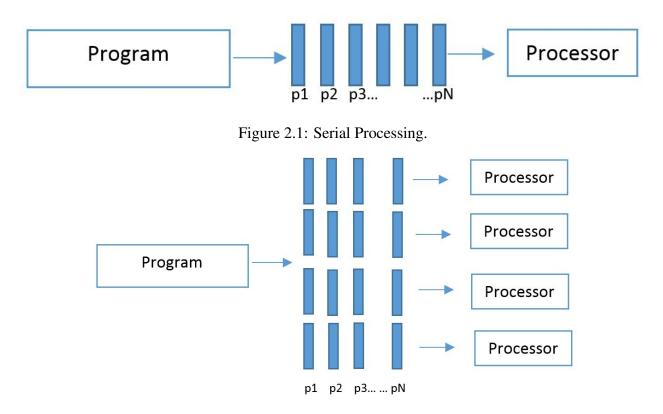

Traditional software code, such as C and C++, is written for sequential computation. It is normal for people to break a problem and solve it step by step. Only one instruction is executed at a particular moment and those instructions are executed in a sequence [8]. Figure 2.1 shows a simple serial process.

Nowadays, parallelism is becoming ubiquitous, and parallel programming is becoming mainstream in the programming world. Parallelism at multiple levels is the driving force of architecture design. There are two fundamental types of parallelism in applications: Task parallelism and Data parallelism Task parallelism arises when there are many tasks or functions that can be operated independently and largely in parallel. Task parallelism focuses on distributing functions across multiple cores. Data parallelism arises when there are many data items that can be operated on at the same time. Data parallelism focuses on distributing the data across multiple cores.

In parallel computing, multiple pieces of data will be processed simultaneously using different processing resources. It means that the problem will be partitioned to several parts and these parts can be executed concurrently. Figure 2.2 demonstrates a parallel processing scenario. When using parallel model to break down a problem, it is necessary to consider the accuracy of result. Sometimes, processors need to share results among each other, therefore introducing communications among processors.

#### 2.1.1 MPI

Message Passing is a parallel programming model where communication between processes is done by interchanging messages. This is a natural mode for a distributed memory system,

Figure 2.2: Parallel Processing.

where communication cannot be achieved by sharing variables. Message Passing Interface (MPI) processes executed in parallel have separate memory address spaces. The same program runs on all processes (Single Program Multiple Data, or SPMD). This is no restriction compared to the more general MPMD (Multiple Program Multiple Data) model as all processes taking part in a parallel calculation can be distinguished by a unique identifier.

The program is written in a sequential language like Fortran, C or C++. Data exchange, i.e., sending and receiving of messages, is done via calls to an appropriate library. Communication occurs when part of the address space of one process is copied into the address space of another process. This operation is cooperative and occurs only when the first process executes a send operation and the second process executes a receive operation.

The workload partitioning and task mapping have to be done by the programmer. The programmer need to know how to utilize hardware resource efficiently for performance and scalability to unveil any problems connected to parallelization. Besides, some issues still need to be addressed,

Figure 2.3: Parallel Processing.

such as serial execution (Amdahls Law), load imbalance, unnecessary synchronization, and other effects that impact all parallel performance.

In summary, MPI is well suited for applications where portability, both in space (across different systems existing now) and in time (across generations of computers), is important. MPI is also an excellent choice for task-parallel computations and for applications where the data structures are dynamic.

#### 2.1.2 OpenMP

OpenMP is a shared memory application programming interface (API) [15] whose aim is to ease shared memory parallel programming. Shared memory opens the possibility to have immediate access to all data from all processors without explicit communication. Unfortunately, POSIX threads are not a comfortable parallel programming model for most scientific software, which is typically loop-centric. For this reason, a joint effort was made by compiler vendors to establish a standard in this field, called OpenMP.

The OpenMP multithreading interface is specifically designed to support high performance computing (HPC) programs. It is also portable across shared memory architectures. OpenMP is a set of directives to a compiler. When a compiler recognizes OpenMP directives, then the directives are interpreted to give direction on how to create parallel tasks in order to speed execution of a program through parallelism.

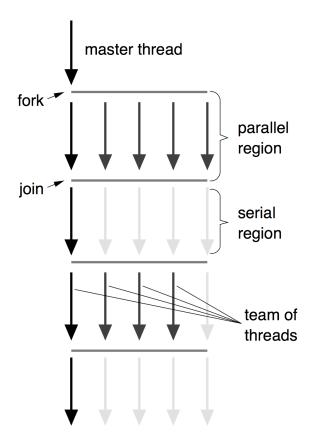

In any OpenMP program, a single thread, the master thread, runs immediately after startup. Truly parallel execution happens inside parallel regions, of which an arbitrary number can exist in a program. Between two parallel regions, no thread except the master thread executes any code. This is also called the fork-join model, as shown in Figure 2.3.

Inside a parallel region, a team of threads executes instruction streams concurrently. The number of threads in a team may vary among parallel regions [46, 47]. For example, omp\_get\_thread\_num() can fork a specified number of threads and system can allocate these threads to a task. OpenMP can assign the number of threads on environment variable, or can use function of OpenMP to assign threads' number at the code. Each thread has an ID. Every ID is integer type and the ID of master thread is 0. These threads can execute concurrently. For example, there is a "for" loop for addition operations (sum[i]=a[i]+b[i]). Each thread can do a part of addition at the same time.Working-sharing constructs can allocate part of task to different threads so that they can execute the work concurrently. Each thread cannot be disturbed by others. So if the code is not independent, there will be a problem when using working-sharing constructs. When the execution of parallelized code is done, these threads join back to master thread. And the master thread will continue executing the rest of program until it meets next parallel section or the end of program.

#### 2.2 CUDA

CUDA stands for Compute Unified Device Architecture. It is a specific parallel programming language implemented by NVIDIA. CUDA is a parallel programming model and computing platform. When using CUDA for programming, the developers can access the memory of computational elements, such as global memory, shared memory and local memory. Like OpenCL, CUDA has its own application programming interfaces. This approach is known as Stream Processing. GPU has a different architecture than CPU. It contains hundreds to thousands of processing cores for parallel processing. CUDA supports both C/C++ and Fortran. CUDA also supports other computing interfaces such as OpenCL and OpenGL. CUDA provides two levels of API, lowlevel API and high-level API. Usually it is enough for programmers to only use high-level API to allocate memory of GPU and launch a kernel to GPU. When you need more specific function to your program, you need to use low-level API to allocate and run your program. Basically, CUDA supports most of GPUs provided by NVIDIA, such as GeForce, Quadro and Tesla series. CUDA is supported on multiple operating systems, such as Windows and Linux system.

CUDA programming is especially well-suited to address problems that can be expressed as data parallel computations. Many applications that process large data sets can use a data-parallel model to speed up the computations. Data-parallel processing maps data elements to parallel threads.

#### 2.3 Parallel Computing Hardware

#### 2.3.1 Multi-core Processor

A multi-core processor is a processor with multiple independent processing cores. With the development of computer architecture, central processing unit has changed a lot, such as design technology and the implementation of CPU. However, the basic operation keeps much the same. Most computers have multi-core processors, such as 8-core CPU and 16-core CPU. It is better for

multi-core processor to use different cores to deal with different processing. Multi-core processor can run faster and bring a better performance to users. Programmers can use parallel library such as OpenMP and MPI to take full advantage of all cores and get a better performance. Of course, not all of computing system only depend on multi-core processor. A number of hardware accelerators are provided, such as GPU, FPGA and MIC in the distributed architecture, but multi-core processor still plays an important role.

#### 2.3.2 GPU

GPU architecture has been developed for many years and different companies have gone through many generations. For example, NVIDIA generates different architecture of GPU, such as  $G80 \rightarrow GT200 \rightarrow Fermi \rightarrow Kepler \rightarrow Pascal$ . With the development of graphic processing unit, it is becoming normal to use GPU as a modified form of stream processor for general purposes. This concept changes GPU from a modern graphics accelerators into a general purpose accelerator.

Therefore, high performance computers that are based on GPUs become a significant role in large scale modeling [49]. Nowadays, the two major GPU designers are NVIDIA and AMD. NVIDIA develops CUDA to support GPU programming.

OpenCL [58] is also supported by NVIDIA's GPU. OpenCL is designed to work for architectures of multiple types, such as CPUs, GPU and DSP. Both programming languages allow a program to launch a kernel on GPU and run the parallel program on its stream processors. And programmer can make a decision about which part is running on GPU or CPU. It can take advantage of the ability of GPU and CPU to perform their own appropriate work.

#### 2.3.3 MIC

Intel demonstrated a new hardware architecture called Many Integrated Core(MIC) [4] as accelerators for high-performance computing domain. It provides another option for augmenting the computer clusters for high performance and low power consumption [42, 57, 26]. The MIC

Figure 2.4: Spectrum of Programming Models.

has demonstrated the high performance, the scalability, and the high memory bandwidth. An evaluation of the scalability on the Intel MIC based graph algorithms shows that MIC can be programmed easily and scaled gracefully on graph algorithm [54].

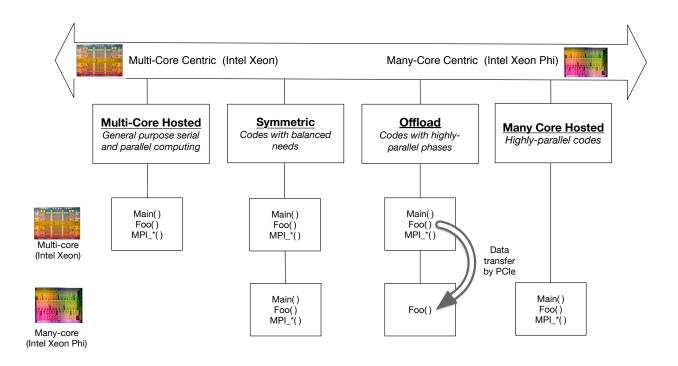

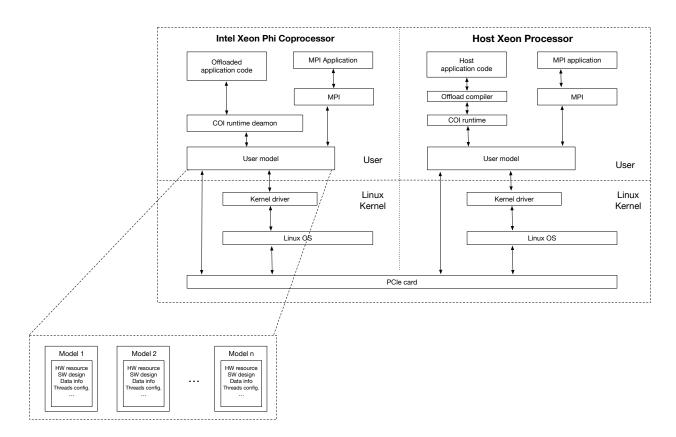

The commercially available Intel coprocessor based on the MIC architecture is Xeon Phi. Xeon Phi contains up to 61 scalar processing cores with vector processing units. Further, each core can execute four threads in parallel. The communications between the cores can be realized through the shared memory programming models, e.g. OpenMP. In addition, each core can run MPI to realize communication. Direct communication between MIC processors across different nodes is also supported through MPI. And Intel coprocessors supports several programming models to meet application needs, as shown in Figure 2.4.

Figure 2.5: The software architecture of Intel Xeon Phi coprocessor.

#### 2.4 Programming models

#### 2.4.1 MPI+CPU

MPI-based parallel implementation is shown in Figure 2.6(a). The Intel Xeon CPU works for data processing. The resource used on CPU is a single-thread process. Each MPI process runs on a single CPU. If m MPI processes are established in the parallel application, m CPU processors are used. A sample code is shown in Algorithm 1.

#### 2.4.2 MPI+GPU

GPU-based parallel implementation on high performance system is shown in Figure 2.6(b). Each MPI process runs on Intel Xeon CPU. Every Xeon CPU offloads data to one GPU processor. If m MPI processes are used in application, m CPU processors and m GPU processors are allocated.

Function Transition(Array A, Array B) $MPI\_Init();$  $MPI\_Comm\_rank();$  $MPI\_Comm\_size();$  $for i = 0 \rightarrow k - 1$ do $\lfloor A[i] \leftarrow B[i];$  $MPI\_Finalize();$

The host CPU works for the MPI communication and collecting results. The GPU is responsible for data processing. A sample code is shown in Algorithm 2.

#### 2.4.3 MIC Native mode

The native model runs the calculation procedures entirely on an Intel Xeon Phi coprocessor. The Intel Xeon Phi coprocessor has its own operation system, such as Linux, IP address, a highperformance network connection and memory domain. The coprocessor is an x86-based SMP-ona-chip with over many cores. Some MICs have 59 cores, and others may have more than 60 cores. Each MIC core has multiple hardware threads, and 512-bit SIMD instructions. The Intel Xeon Phi looks like an independent compute node. Users can log into any Xeon Phi installed in production system by a terminal window and compile programs with the mmic switch to target launch and

#### ALGORITHM 2: MPI+GPU Programming model

**Function** Transition(*Array A*, *Array B*)

$MPI\_Init();$   $MPI\_Comm\_rank();$   $MPI\_Comm\_size();$  Allocate GA and GB on GPU memory; Copy A and B to GA and GB; Launch GPU kernel;  $for i = 0 \rightarrow k - 1 do$   $\lfloor A[i] \leftarrow B[i];$  Copy GA back to A;  $MPI\_Finalize();$

ALGORITHM 3: MPI@MIC+OpenMP Programming model

Function Transition(Array A, Array B)

MPI\_Init();

MPI\_Comm\_rank();

MPI\_Comm\_size();

#pragma omp parallel for omp\_set\_num\_threads(4);

for  $i = 0 \rightarrow k - 1$  do

$\lfloor A[i] \leftarrow B[i];$

MPI\_Finalize();

execution directly on the coprocessors, as shown in Figure 2.5.

Supercomputer provides a heterogeneous environment, including host Xeon CPUs and Xeon Phi coprocessors. MIC-based parallel implementation on high performance system is shown in Figure 2.7. Applications that are already implemented by MPI can use this model by distributing MPI ranks across the coprocessors natively. In the native model, MPI can be run natively on the coprocessors without any modification on the original source code. Each MIC core directly hosts n (up to 4) MPI processes. Therefore, if m Xeon Phi coprocessors are used, m n 60 MPI processes are created in the parallel implementation. However, no job is dispatched on the host Xeon CPU. Besides, each MPI process create 4 threads to run OpenMP program as shown in Algorithm 3.

(a) MPI native parallel implementation.

(b) MPI and OpenMP native parallel implementation.

Figure 2.7: MIC native parallel implementation on Beacon

#### 2.4.4 MIC offload mode

The offload mode, as shown in Figure 2.8, provides an alternative approach to utilize the MIC coprocessors. In this case, a MPI program running on the host CPU can optionally launch part of work to a MIC coprocessor on the same platform. The developer just identifies lines or sections of code that are best suited for the many cores on MIC coprocessor by inserting commands to invoke the parallel capability.

The offload model uses the keyword pragma to specify code sections and to offload data to the MIC.In this model, the application starts on the host CPU. When an offload region is encountered, the offload region and data are transferred to run on the target device (MIC).The MPI processes are allocated on the host CPU cores, while the data and computation are dispatched to the MIC coprocessors. The MPI process specifies the number of threads to the MIC that uses OpenMP to handle data and calculation.

The code is just compiled for the host processor. When offload commands are encountered and the coprocessor is running and available, the required data and code is automatically transferred between the host and coprocessor as needed. If no MIC coprocessor is running or available, the

Figure 2.8: Offload parallel implementation on Beacon

command line or block of code will be executed on the host. This means that even though MIC may not work properly (such as connection problem between MIC and host CPU), the program still works on the host.

Offloading could simply be thought of an inline code that may be run on a coprocessor, as shown in Algorithm 4. The program executes the first pragma offload command to initialize all MIC devices. This initialization will load the MIC program on to each device, set up a data transfer between CPU and the device, and create a MIC thread to handle offload requests from the CPU thread. The host CPU processor and MIC coprocessors do not share the same system memory. As a result, the variables used by the code must be duplicated so that distinct copies exist on both the host processor and coprocessor. As shown in the following example, the pragma command uses specifiers to define the variables to copy between the host processor and coprocessor. The in specifier defines a specific variable as an input to the coprocessor. The value is not copied back to the host processor does not copy the variable to the coprocessor. The inout specifier defines a specific variable that is both copied from the host processor to the coprocessor and back from the coprocessor to the host processor.

## ALGORITHM 4: MPI@MIC+OpenMP Programming model

**Function** <u>Transition(Array A, Array B)</u>

$\begin{array}{l} MPI\_Init();\\ MPI\_Comm\_rank();\\ MPI\_Comm\_size();\\ \#pragma \ of \ fload \ target(mic) \ in(var) \ out(Out \ put1: length(Out \ put1.size) \\ inout(Out \ put2: length(Out \ put2.size);\\ \#pragma \ omp \ parallel \ for \ omp\_set\_num\_threads(4);\\ \textbf{for } \ i=0 \rightarrow k-1 \ \textbf{do} \\ \lfloor \ A[i] \leftarrow B[i];\\ \\ Memory \ copy \ back \ to \ host;\\ MPI\_Finalize(); \end{array}$

#### Chapter 3

#### Study of parallel programming models with Intel MIC coprocessors

In this chapter, we conduct a detailed study regarding the performance and scalability of 5 execution modes on Intel MIC processors. In the first mode, the MPI process is directly run on each MIC core. In the second mode, we try to take advantage of the internal processing parallelism on each MIC core. Therefore, we launch 4 threads in each MPI process using OpenMP. Each MPI process is still run on a MIC core. In the third mode, only one MPI process is issued onto each MIC processor. Then OpenMP is used to launch threads to MIC cores. In the fourth mode, the MPI processes are run on the CPUs. The data processing is offloaded to the MIC processors using OpenMP. Only one thread is scheduled to one MIC core. The fifth mode is a variant of the fourth one. Four threads are scheduled to one MIC core in the fifth mode. We use two geospatial applications, i.e., Kriging interpolation and Cellular Automata, to test the performance and scalability of a single MIC processor and a computer cluster with hybrid nodes.

#### 3.1 Introduction

The Intel MIC architecture contains many low-weight processing cores, as shown in Figure 3.1. These cores are connected through a high-speed ring bus. Each core can run 4 threads in parallel. Because each core alone is a classic processor, traditional parallel programming models, such as MPI and OpenMP, are supported on each core. The MIC processors typically co-exist with multicore CPUs, such as Intel Xeon CPU, in a hybrid computer node as coprocessors/accelerators. In the remainder of this chapter, a single MIC card or device will be called a MIC processor or MIC coprocessor. The constituent processing core on a MIC card will be called a MIC core.

Through this study, we have the following findings. (1) The native MPI programming model on the MIC processors is typically better than the offload programming model, which offloads the

Figure 3.1: The architecture of Intel Xeon Phi coprocessor (MIC) [5].

workload to MIC cores using OpenMP. (2) On top of the native MPI programming model, multithreading inside each MPI process can further improve the performance for parallel applications on computer clusters with MIC coprocessors. (3) Given a fixed number of MPI processes, it is a good strategy to schedule these MPI processes to as few MIC processors as possible to reduce the cross-processor communication overhead when the capacity of the on-board memory is not a limiting factor. (4) We also evaluate a hybrid MPI programming model, which is not officially supported by the Intel MPI compiler. In this hybrid model, the data processing is distributed to both the MIC cores and the CPU cores. The benchmarking results show that the hybrid model outperforms the native model.

The remainder of this chapter is organized as follows. The Intel MIC architecture and the two major programming models are discussed in Section 3.2. We discuss the details of the benchmarks and the experiment platform in Section 3.3. In Section 3.4, we show the experiment results on a single MIC device. We also compare the performance of a single MIC device with a single Xeon CPU and the latest GPUs. Then we expand the experiment on two geospatial benchmarks to the Beacon cluster using many computer nodes in Section 3.5. We discuss some related work in Section 3.6. Finally, we give the concluding remarks in Section 3.7.

#### **3.2** Intel MIC architecture and programming models

The commercially available Intel coprocessor based on Many Integrated Core architecture is Xeon Phi, as shown in Figure 3.1. Xeon Phi contains more than 50 scalar processing cores with vector processing units. These cores are connected through a high-speed bi-directional, 1024-bit-wide ring bus (512 bits in each direction). In addition to the scalar unit inside each core, there is a vector processing unit to support wide vector processing operations. Further, each core can execute 4 threads in parallel. The communications between the cores can be realized through the shared memory programming models, e.g., OpenMP. Additionally, each core can run MPI to realize communication. Direct communication between MIC processors across different nodes is also supported through MPI.

This work uses two approaches to parallelizing applications on computer clusters equipped with MIC processors. The first approach is the native model. In this model, the MPI processes directly run on the MIC processors. There are two variants under this model. (1) Let each MIC core directly host one MPI process. In this way, the 60 cores on the Xeon Phi 5110P, which is used in this work, are treated as 60 independent processors while sharing the 8 GB on-board memory. (2) Only issue one MPI process on one MIC card. This single MPI process then spawns threads running on many cores using OpenMP. The second approach is to treat the MIC processors as clients to the host CPUs. The MPI processes will be hosted by CPUs, which will offload the computation to the MIC processors. Multithreading programming models such as OpenMP can be used to allocate many MIC cores for data processing in the offload model.

In this work there are 5 different parallel implementations in these 2 models as follows.

- Native model: In this model, MPI processes directly execute on MIC processors. There are further 3 implementations.

- Native-1 (N-1): Issue one MPI process onto each MIC core. If *n* MIC cores are allocated, then *n* MPI processes are issued. Each MPI process contains only one thread.

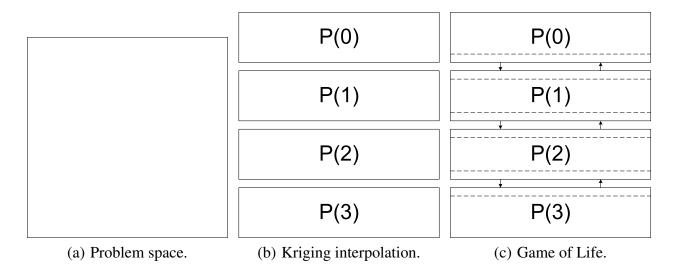

Figure 3.2: Data partition and communication in two benchmarks. In Kriging interpolation there is no communication among MPI processes (i.e., P(I) in the figure) during computation. In Game of Life, MPI processes need to communicate with each other in the computation.

- Native-2 (N-2): Issue one MPI process onto each MIC core. Each MPI process contains 4 threads.

- Native-3 (N-3): Issue only one MPI process onto each MIC card. Then allocate many MIC cores using OpenMP. On each MIC core, issue 4 threads.

- Offload model: In this model, the CPU offloads the work to the MIC processor using OpenMP. There are further 2 implementations.

- Offload-1 (O-1): Issue one thread onto each MIC core. If *n* MIC cores are allocated, then *n* threads are issued.

- Offload-2 (O-2): Issue 4 threads onto each MIC core. If *n* MIC cores are allocated, then  $4 \times n$  threads are issued.

#### **3.3** Experiment setup

#### 3.3.1 Benchmarks

Two geospatial applications are chosen to represent two types of benchmarks in high-performance computing: the embarrassingly parallel case and the intense communication case.

#### **Embarrassingly parallel case – Kriging Interpolation**

Kriging is a geostatistical estimator that infers the value of a random field at an unobserved location [24]. Kriging is based on the idea that the value at an unknown point should be the average of the known values of its neighbors.

Kriging can be viewed as a point interpolation that reads input point data and returns a raster grid with calculated estimations for each cell. Each input point is in the form  $(x_i, y_i, Z_i)$  where  $x_i$ and  $y_i$  are the coordinates and  $Z_i$  is the value. The estimated values in the output raster grid are calculated as a weighted sum of input point values as in (3.1).

$$\hat{Z}(x,y) = \sum_{i=1}^{k} w_i Z_i,$$

(3.1)

where  $w_i$  is the weight of the *i*-th input point. Theoretically the estimation can be calculated by the summation through all input points. In general, users can specify a number *k* so that the summation is over *k* nearest neighbors of the estimated point in terms of distance. This decrease of computation is due to the fact that the farther the sampled point is from the estimated point, the less impact it has in the summation. For example, the commercial software ArcGIS [2] uses the 12 nearest points (i.e., k = 12) in the Kriging calculation by default. In this benchmark, embarrassing parallelism can be realized since the interpolation calculation over each cell has no dependency on the others.

In the Kriging interpolation benchmark, the problem space as shown in Figure 5.8(a) is evenly

```

for(each data set in the 4 data sets) {

/*The following for loop can be parallelized*/

for(each point in the 1,440x720 output grid) {

Scan the whole data set to find the 10 closest

sampled points;

Use Equation (1) to estimate the value of the

unsampled point;

}

}

```

Figure 3.3: Pseudocode of Kriging interpolation. The inner for loop can be parallelized while the 4 data sets in the out for loop are processed in sequence.

partitioned among all MPI processes as shown in Figure 5.8(b), in which we use 4 processes as an example. The computation in each MPI process is purely local, i.e., there is no cross-process communication.

The input size of this benchmark is 171 MB, consisting of 4 data sets with the respective sizes of 29 MB, 37 MB, 48 MB, and 57 MB. Each data set has 2,191, 4,596, 6,941, and 9,817 sample points, respectively. The output raster grid for each data set has a consistent dimension of 1,440×720. In other words, each data set will generate a 1,440×720 grid. The value of each point in the output grid needs to be estimated using those sample points in the corresponding input data set. In our experiments, the value of an unsampled point will be estimated using the values of the 10 closest sample points, i.e., k = 10. These 4 data sets are processed in a sequence. For each data set, the generation of its corresponding output grid is evenly distributed among all MPI processes. In order to generate the value of a point in the output grid, all the sampled points in the data set need to be scanned to find the 10 closest sample points. The pseudocode of Kriging interpolation is illustrated in Figure 3.3.

#### Intense communication case - Cellular Automata

Cellular Automata (CA) are the foundation for geospatial modeling and simulation. Game of Life (GOL) [22], invented by British mathematician John Conway, is a well-known generic Cellular Automaton. It consists of a collection of cells that can live, die or multiply based on a few mathematical rules.

```

for(iteration=0; iteration <100; iteration++) {

/*The following for loop can be parallelized*/

for(all cells in the universe) {

Update the status of cell[i,j] based on the

statuses of cell[i,j] and its 8 neighbors;

}

}</pre>

```

Figure 3.4: Pseudocode of Game of Life.

The universe of the Game of Life is a two-dimensional square grid of cells, each of which is in one of two possible states, alive ('1') or dead ('0'). Every cell interacts with its eight neighbors, which are the cells that are horizontally, vertically, or diagonally adjacent. At each step in time, the following transitions occur:

- Any live cell with fewer than two live neighbors dies, as if caused by under-population.

- Any live cell with two or three live neighbors lives on to the next generation.

- Any live cell with more than three live neighbors dies, as if by overcrowding.

- Any dead cell with exactly three live neighbors becomes a live cell, as if by reproduction.

In this benchmark, the status of each cell in the grid will be updated for 100 iterations. In each iteration, the statuses of all cells are updated simultaneously. The pseudocode is illustrated in Figure 3.4. In order to parallelize the updating process, the cells in the square grid are partitioned into stripes along the row-wise order. Each stripe is handled by one MPI process. At the beginning of each iteration, each MPI process needs to send the statuses of the cells along the boundaries of each stripe to its neighbor MPI processes and receive the statuses of the cells of two adjacent rows as shown in Figure 5.8(c).

# 3.3.2 Experiment Platform

We conduct our experiments on the NSF sponsored Beacon supercomputer [3] hosted at the National Institute for Computational Sciences (NICS), University of Tennessee.

The Beacon system (a Cray CS300-AC Cluster Supercomputer) offers access to 48 compute

nodes and 6 I/O nodes joined by FDR InfiniBand interconnect, which provides a bi-directional bandwidth of 56 Gb/s. Each compute node is equipped with 2 Intel Xeon E5-2670 8-core 2.6-GHz processors, 4 Intel Xeon Phi (MIC) 5110P coprocessors, 256 GB of RAM, and 960 GB of SSD storage. Each I/O node provides access to an additional 4.8 TB of SSD storage. Each Xeon Phi 5110P coprocessor contains 60 1.053-GHz MIC cores and 8-GB GDDR5 on-board memory. Altogether Beacon contains 768 conventional cores and 11,520 accelerator cores that provide over 210 TFLOP/s of combined computational performance, 12 TB of system memory, 1.5 TB of coprocessor sor memory, and over 73 TB of SSD storage.

The compiler used in this work is Intel 64 Compiler XE, Version 14.0.0.080 Build 20130728, which supports OpenMP. The MPI library is intel-mpi 4.1.0.024.

#### **3.4** Experiments and results on a single device

Since a single Intel Xeon Phi 5110P processor is a 60-core processor, it is worthwhile to investigate the performance and scalability of a single MIC processor alone.

### 3.4.1 Scalability on a single MIC processor

When MPI programming model is used to implement the Kriging interpolation application, the workload is evenly distributed among MPI processes. In this benchmark, there are 4 data sets. For each data set, the output is a  $1,440 \times 720$  raster grid. In the MPI implementation, we increase the number of MPI processes from 10 to 60 with a stride of 10 processes. The computation of 720 columns of the output grid is evenly distributed. The 50-process configuration is skipped because 720 columns cannot be distributed among 50 processes equally. For the offload programming model, we use OpenMP to parallelize the for loops in the program. The OpenMP APIs will automatically distribute workload to the MIC cores evenly.

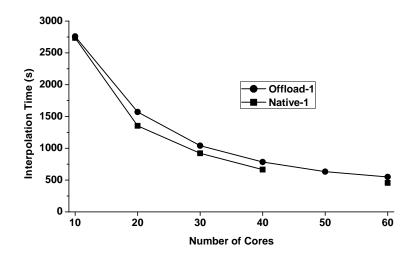

The detailed execution times of the Kriging interpolation benchmark under both program-

| Execution mode: Native-1 |         |                     |             |           |        |        |  |  |  |  |

|--------------------------|---------|---------------------|-------------|-----------|--------|--------|--|--|--|--|

|                          |         | Number of MIC cores |             |           |        |        |  |  |  |  |

|                          | 10      | 20                  | 30          | 40        | 50     | 60     |  |  |  |  |

| Read                     | 0.65    | 0.60                | 0.66        | 0.72      |        | 0.79   |  |  |  |  |

| Interpolation            | 2734.45 | 1353.48             | 921.76      | 664.74    | NA*    | 455.34 |  |  |  |  |

| Write                    | 9.44    | 9.21                | 11.04       | 8.04      | INA    | 7.95   |  |  |  |  |

| Total                    | 2744.54 | 1363.30             | 933.46      | 673.50    |        | 464.09 |  |  |  |  |

|                          | Ex      | xecution m          | ode: Offloa | ad-1      |        |        |  |  |  |  |

|                          |         | N                   | umber of N  | /IC cores |        |        |  |  |  |  |

|                          | 10      | 20                  | 30          | 40        | 50     | 60     |  |  |  |  |

| Read                     | 0.04    | 0.05                | 0.04        | 0.04      | 0.04   | 0.04   |  |  |  |  |

| Interpolation            | 2758.22 | 1570.75             | 1040.44     | 784.30    | 632.65 | 548.15 |  |  |  |  |

| Write                    | 1.77    | 1.99                | 1.65        | 1.44      | 1.45   | 1.57   |  |  |  |  |

| Total                    | 2760.03 | 1572.78             | 1042.12     | 785.78    | 634.14 | 549.75 |  |  |  |  |

Table 3.1: Performance of Kriging interpolation on a single MIC processor (unit: second).

E

\*The workload could not be distributed among 50 cores evenly.

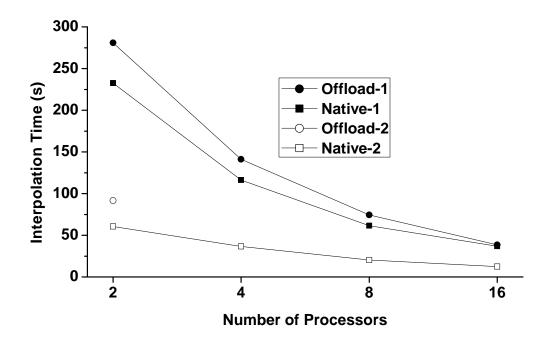

ming models while each MIC core hosts only one thread are listed in Table 3.1. By looking at the time curves in Figure 3.5, we can find that both models show a good strong scalability for this application. Their performance in terms of interpolation time is very close too. The reason we do not include the write time in Figure 3.5 is that the write time may become dramatically lengthy when the number of MPI processes increases. In the Kriging interpolation application, each output raster grid is written into a file. When many MPI processes try to write to the same file, their writes need to be serialized. Further, the arbitration takes a lot of time. This effect is not very significant when one MIC processor is used. Later, we will find that the write time can become extremely significant when many MIC processors are allocated.

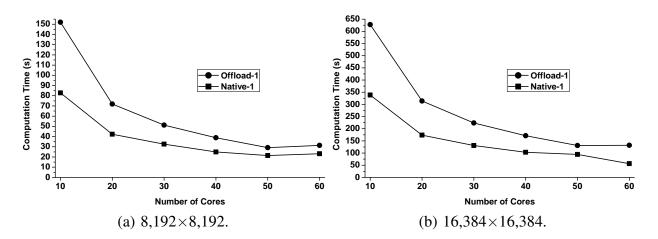

For Game of Life three different grid sizes are tested, i.e.,  $8,192 \times 8,192$ ,  $16,384 \times 16,384$ , and  $32,768 \times 32,768$ . However, we encounter either out-of-memory error or runtime error for the  $32,768 \times 32,768$  case when only one MIC processor is used. From the results in Table 3.2, it can be found that the native model consistently outperforms the offload model for this intense communication case. By looking at the performance curves in Figure 3.6, we can find that both programming

Figure 3.5: Performance of Kriging interpolation on a single MIC processor. For both implementation, only one thread runs on a MIC core. The native implementation outperforms the offload one with a small margin.

| Execution mode: Native-1 |                     |                     |          |        |        |        |  |  |  |  |

|--------------------------|---------------------|---------------------|----------|--------|--------|--------|--|--|--|--|

| Problem Size             |                     | Number of MIC cores |          |        |        |        |  |  |  |  |

|                          | 10                  | 20                  | 30       | 40     | 50     | 60     |  |  |  |  |

| 8192×8192                | 82.85               | 42.27               | 32.56    | 24.91  | 21.37  | 23.15  |  |  |  |  |

| 16384×16384              | 338.57              | 173.57              | 131.10   | 103.30 | 94.41  | 56.31  |  |  |  |  |

|                          | Execu               | ution mo            | de: Offl | oad-1  |        |        |  |  |  |  |

| Problem Size             | Number of MIC cores |                     |          |        |        |        |  |  |  |  |

| I IODICIII SIZC          | 10                  | 20                  | 30       | 40     | 50     | 60     |  |  |  |  |

| 8192×8192                | 152.06              | 71.9                | 51.23    | 38.88  | 29.1   | 31.33  |  |  |  |  |

| 16384×16384              | 627.94              | 313.88              | 223.54   | 171.33 | 131.14 | 131.72 |  |  |  |  |

Table 3.2: Performance of Game of Life on a single MIC processor (unit: second).

models show strong scalability when the number of cores increases from 10 to 20. Beyond that, both models lose the strong scalability although the total computation time still decreases. For both problem sizes, the reduction of workload is gradually offset by the increase of communication overhead when the number of cores increases. Further, when more cores are allocated, the memory access demand increases as well. Eventually, the communication and memory bandwidth become the limiting factors for the performance.

Figure 3.6: Performance of Game of Life on a single MIC processor. The native model outperforms the offload model with a big margin when only a few cores are used. The performance gap decreases as more cores are allocated.

|       |        |        | MIC      |            |         | C        | PU        | Nvidia |       |

|-------|--------|--------|----------|------------|---------|----------|-----------|--------|-------|

|       |        | (      | 60 cores | )          | (Xeon I | E5-2670) | GPU       |        |       |

|       | N-1    | N-2    | N-3      | <b>O-1</b> | O-2     | 8-thread | 16-thread | C2075  | K20   |

| Read  | 0.79   | 1.03   | 0.45     | 0.04       | 0.42    | 0.01     | 0.01      | 0.01   | 0.01  |

| Intp. | 455.34 | 173.89 | 5147.95  | 548.15     | 225.93  | 330.11   | 182.60    | 23.87  | 10.90 |

| Write | 7.95   | 8.57   | 16.71    | 1.57       | 1.38    | 9.85     | 10.27     | 1.68   | 1.68  |

| Total | 464.09 | 183.49 | 5165.11  | 549.75     | 227.72  | 339.96   | 192.86    | 25.55  | 11.77 |

Table 3.3: Performance of Kriging interpolation on single devices (unit: second).

# 3.4.2 Performance comparison of single devices

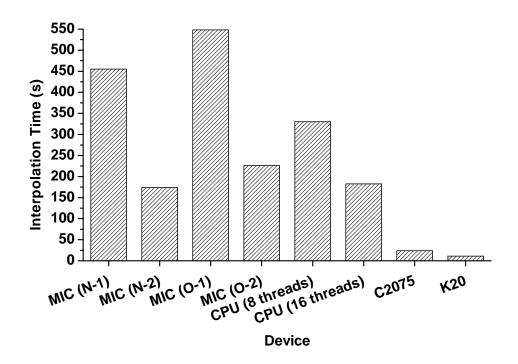

As an emerging new technology, it is worthwhile to compare the performance of the Intel MIC processor with the other popular accelerator, i.e., GPU. Furthermore, it is a routine to include very powerful multicore CPUs in supercomputers. Therefore, we conduct a comparison among these three technologies at the full capacity of a single device. For Intel Xeon Phi 5110P, we use all 60 cores under two programming models for 5 different implementations. For the 8-core Xeon E5-2670 CPU on Beacon cluster, we use OpenMP to issue either 8 threads or 16 threads. For GPU, we test two devices, the Nvidia Tesla C2075 based on Fermi architecture [43] and the Tesla K20 based on Kepler architecture [44]. The CUDA version is 5.5.

The execution times of Kriging interpolation on various devices are listed in Table 3.3. It

Figure 3.7: Performance of Kriging interpolation on single devices (excluding Native-3 implementation on Intel MIC device).

|                    |       |       | MIC    |            |       | C        | PU        | Nvidia |       |  |

|--------------------|-------|-------|--------|------------|-------|----------|-----------|--------|-------|--|

|                    |       | (6    | 60 cor | es)        |       | (Xeon I  | E5-2670)  | GPU    |       |  |

|                    | N-1   | N-2   | N-3    | <b>O-1</b> | O-2   | 8-thread | 16-thread | C2075  | K20   |  |

| 8192 <sup>2</sup>  | 23.15 | 18.22 | 11.23  | 31.33      | 19.53 | 12.03    | 8.13      | 15.36  | 3.25  |  |

| $16384^2$          | 56.31 | 82.66 | 41.12  | 131.72     | 79.93 | 48.22    | 32.65     | 58.44  | 12.58 |  |

| 32768 <sup>2</sup> |       |       | NA     |            |       | 217.33   | 114.98    | 274.03 | 46.99 |  |

Table 3.4: Performance of Game of Life on single devices (unit: second).

can be found that the performance of the MIC processor and the CPU is at the same order of magnitude. When running at the full capacity, the performance of the Intel Xeon Phi 5110P is equivalent to the Xeon E5-2670. By increasing the number of threads in an MPI process to 4, the Native-2 implementation is able to improve the performance by 3 times compared with Native-1 implementation. However, the Native-3 implementation, i.e., one MPI process with 240 threads, has the much worse performance. We varied the number of threads in the MPI process and found that the performance did not change significantly. We speculate that the OpenMP library does not work well with the Kriging interpolation under Native-3 programming model. For Xeon CPU the 16-thread CPU implementation is almost 2 times faster than the 8-thread implementation because

| Number of  |      | Nat                | tive-1 |        | Native-2 |                     |        |        | Native-3 |                     |       |         |

|------------|------|--------------------|--------|--------|----------|---------------------|--------|--------|----------|---------------------|-------|---------|

| Processors | Read | Inter.*            | Write  | Total  | Read     | Inter. <sup>1</sup> | Write  | Total  | Read     | Inter. <sup>1</sup> | Write | Total   |

| 2          | 1.24 | 232.43             | 12.24  | 245.90 | 0.57     | 60.43               | 8.82   | 69.82  | 0.33     | 2563.07             | 12.53 | 2575.97 |

| 4          | 1.27 | 116.34             | 16.44  | 134.05 | 0.51     | 36.54               | 122.53 | 159.59 | 0.33     | 1284.93             | 10.04 | 1305.35 |

| 8          | 1.23 | 61.48 <sup>†</sup> | 54.43  | 117.14 | 0.50     | $20.43^2$           | 240.33 | 261.26 | 0.33     | 730.58              | 9.37  | 740.29  |

| 16         | 1.31 | 36.74 <sup>2</sup> | 300.23 | 338.28 | 0.52     | 12.33 <sup>2</sup>  | 210.45 | 223.30 | 0.34     | 377.95              | 9.10  | 387.39  |

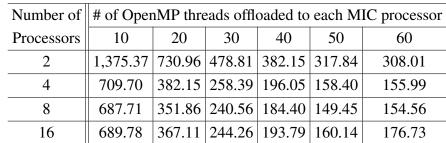

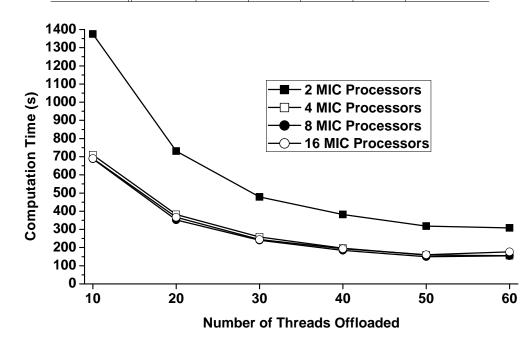

Table 3.5: Performance of Kriging interpolation under various execution modes on multiple MIC processors(unit: second).

| Number of  |      | Offload        | -1    |        | Offload-2                      |                |       |       |  |  |

|------------|------|----------------|-------|--------|--------------------------------|----------------|-------|-------|--|--|

| Processors | Read | Interpolation* | Write | Total  | Read                           | Interpolation* | Write | Total |  |  |

| 2          | 0.18 | 280.83         | 1.60  | 282.61 | 0.39                           | 91.65          | 1.88  | 95.79 |  |  |

| 4          | 0.04 | 141.03         | 1.27  | 142.33 | System does not return result. |                |       |       |  |  |

| 8          | 0.04 | 74.30          | 1.19  | 75.53  |                                |                |       |       |  |  |

| 16         | 0.04 | 38.54          | 5.94  | 44.51  | 1                              |                |       |       |  |  |

\*The interpolation time includes both the time spent on data processing and the time spent on communication.

<sup>†</sup>Only 360 or 720 MIC cores are used in the computation with 8 or 16 processors, respectively.

each CPU core can execute two threads simultaneously. Both GPUs are able to improve the performance by one order of magnitude. Further, K20 is more than 2 times faster than C2075, as shown in Figure 3.7.

The performance results of Game of Life on three different types of processors are listed in Table 3.4. The performance of both models on the MIC processor is at the same order of magnitude as the implementations on the CPU and the C2075. All 5 implementations work quite well on MIC and the native model is typically better than offload model. The Native-3 implementation has the best performance compared with other 4 implementations on MIC. Overall the K20 implementation is generally one order of magnitude better in terms of performance compared with other implementations.

| Number of  | 8,192×8,192 |      |       |       |       | 16,384×16,384 |       |        |       | 32,768×32,768 |        |        |        |        |        |

|------------|-------------|------|-------|-------|-------|---------------|-------|--------|-------|---------------|--------|--------|--------|--------|--------|

| Processors | N-1         | N-2  | N-3   | O-1   | O-2   | N-1           | N-2   | N-3    | O-1   | O-2           | N-1    | N-2    | N-3    | O-1    | O-2    |

| 2          | 14.56       | 7.99 | 92.94 | 20.40 | 13.66 | 48.39         | 33.11 | 275.87 | 78.71 | 48.59         | 194.15 | 149.43 | 964.62 | 308.01 | 184.72 |

| 4          | 11.63       | 8.04 | 44.41 | 11.57 | 8.58  | 46.31         | 24.06 | 172.04 | 42.65 | 26.31         | 169.54 | 104.14 | 544.44 | 155.99 | 96.75  |

| 8          | 7.84        | 9.28 | 23.26 | 12.32 | 8.08  | 39.78         | 22.98 | 108.01 | 42.08 | 28.86         | 157.73 | 106.24 | 317.24 | 154.56 | 99.26  |

| 16         | 7.18        | 8.74 | 21.46 | 13.52 | 9.39  | 35.30         | 23.60 | 107.01 | 47.91 | 34.19         | 128.40 | 110.99 | 300.68 | 176.73 | 105.82 |

Table 3.6: Performance of Game of Life under various execution modes on multiple MIC processors (unit: second).

#### 3.5 Experiments and results using multiple MIC processors

We also conduct the experiments using multiple MIC processors to demonstrate the scalability of the parallel implementations for those two geospatial applications. For both benchmarks we have 5 parallel implementations on the Beacon computer cluster using multiple nodes.

We want to show the strong scalability of the parallel implementations as the case on the single device. Therefore, the problem size is fixed for each benchmark while the number of participating MPI processes is increased.

#### **3.5.1** Comparison among five execution modes

# **Kriging Interpolation**

We allocate 2, 4, 8, and 16 MIC processors for 4 different implementation cases. For the Native-1 and the Native-2 implementations,  $m \times 60$  MPI processes are created if m MIC processors are used. For the Native-3, Offload-1, and Offload-2 execution modes, m MPI processes are created if m MIC processors are used. As mentioned before, for each output raster grid, the generation of the 720 columns is evenly distributed among the MPI processes. Therefore, only 360 or 720 MPI processes, which execute on 360 or 720 MIC cores, are created when 8 or 16 MIC processors are allocated, respectively, for both Native-1 and Native-2 cases.

The detailed results of the five execution modes for Kriging interpolation are listed in Table 3.5. It is noticed that the system does not return results when more than 2 MIC processors are

Figure 3.8: Performance of Kriging interpolation under various execution modes on multiple MIC processors (excluding Native-3 execution mode).

used for Offload-2 execution mode. We can find that the write time grows dramatically when more MIC processors are used for both Native-1 and Native-2 execution modes. As mentioned before, the serialization of the write and the arbitration among the numerous MPI processes contribute to the lengthy write process. Therefore, we only include the interpolation time, which includes both the time spent on data processing and the time spent on cross-processor communication, when comparing the performance of the four execution modes in Figure 3.8. We do not include Native-3 in Figure 3.8 because its interpolation time is significantly larger than other execution modes although it obeys the strong scalability. It can be found that the Native-1 and the Offload-1 execution modes have the very close performance for this benchmark. When the multithreading is applied in each MPI process on the native MPI programming model, the performance can be improved by roughly 3 times. This case shows that it is not enough to only parallelize application to all the cores on MIC processors. It is equally important to increase the parallelism on each MIC core to further improve the performance.

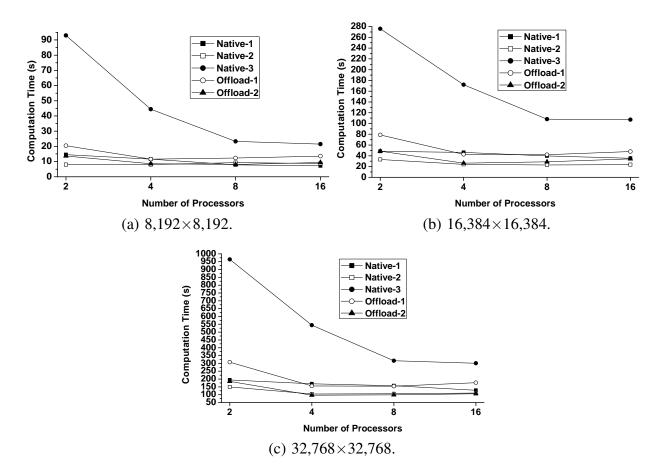

Figure 3.9: Performance of Game of Life under various execution modes on multiple MIC processors.

# **Conway's Game of Life**

For Game of Life on multiple MIC processors, three different grid sizes are tested, i.e.,  $8,192 \times 8,192, 16,384 \times 16,384$ , and  $32,768 \times 32,768$ . By observing the performance results in Table 3.6 and Figure 5.10, it can be found that the behavior is quite different from the performance behavior of Kriging interpolation. First, the strong scalability does not hold for all five execution modes. Although the offload execution modes are still able to reduce the computation time to half when moving from 2-processor implementation to 4-processor implementation, the performance plateaus afterwards. For Native-1 and Native-2 execution modes, it almost stops scaling when more processors are allocated. Apparently, for this communication dense application, there is not much performance gain when increasing the number of MIC processors from 4 to 8 and 16. When

| Number of  | 8,192>    | <8,192    | 16,384>   | <16,384   | 32,768×32,768 |           |  |

|------------|-----------|-----------|-----------|-----------|---------------|-----------|--|

| Processors | 4 threads | 8 threads | 4 threads | 8 threads | 4 threads     | 8 threads |  |

| 2          | 7.99      | 10.94     | 33.11     | 32.92     | 149.43        | 110.37    |  |

| 4          | 8.04      | 9.03      | 24.06     | 27.94     | 104.14        | 109.79    |  |

| 8          | 9.28      | 8.39      | 22.98     | 25.69     | 106.24        | 100.79    |  |

| 16         | 8.74      | 10.77     | 23.60     | 27.11     | 110.99        | 110.67    |  |

Table 3.7: Performance of Game of Life using MPI@MIC\_Core+OpenMP execution mode (unit: second).