# University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

12-2021

# Design, Extraction, and Optimization Tool Flows and Methodologies for Homogeneous and Heterogeneous Multi-Chip 2.5D Systems

MD Arafat Kabir University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Data Storage Systems Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Citation

Kabir, M. (2021). Design, Extraction, and Optimization Tool Flows and Methodologies for Homogeneous and Heterogeneous Multi-Chip 2.5D Systems. *Graduate Theses and Dissertations* Retrieved from <a href="https://scholarworks.uark.edu/etd/4382">https://scholarworks.uark.edu/etd/4382</a>

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact uarepos@uark.edu.

# Design, Extraction, and Optimization Tool Flows and Methodologies for Homogeneous and Heterogeneous Multi-Chip 2.5D Systems

# A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Engineering

by

# MD Arafat Kabir Bangladesh University of Engineering and Technology Bachelor of Science in Electrical and Electronic Engineering, 2017

# December 2021 University of Arkansas

| his thesis is approved for recommendation to the Graduate Council. |                                       |  |  |  |  |

|--------------------------------------------------------------------|---------------------------------------|--|--|--|--|

|                                                                    |                                       |  |  |  |  |

| Yarui Peng, Ph.D. Thesis Director                                  |                                       |  |  |  |  |

|                                                                    |                                       |  |  |  |  |

| Alexander H. Nelson, Ph.D.<br>Committee Member                     | David Andrews, Ph.D. Committee Member |  |  |  |  |

#### **Abstract**

Chip and packaging industries are making significant progress in 2.5D design as a result of increasing popularity of their application. In advanced high-density 2.5D packages, package redistribution layers become similar to chip Back-End-of-Line routing layers, and the gap between them scales down with pin density improvement. Chiplet-package interactions become significant and severely affect system performance and reliability. Moreover, 2.5D integration offers opportunities to apply novel design techniques. The traditional die-by-die design approach neither carefully considers these interactions nor fully exploits the cross-boundary design opportunities.

This thesis presents chiplet-package cross-boundary design, extraction, analysis, and optimization tool flows and methodologies for high-density 2.5D packaging technologies. A holistic flow is presented that can capture all parasitics from chiplets and the package and improve system performance through iterative optimizations. Several design techniques are demonstrated for agile development and quick turn-around time. To validate the flow in silicon, a chip was taped out and studied in TSMC 65nm technology. As the holistic flow cannot handle heterogeneous technologies, in-context flows are presented. Three different flavors of the in-context flow are presented, which offer trade-offs between scalability and accuracy in heterogeneous 2.5D system designs. Inductance is an inseparable part of a package design. A holistic flow is presented that takes package inductance into account in timing analysis and optimization steps. Custom CAD tools are developed to make these flows compatible with the industry standard tools and the foundry model. To prove the effectiveness of the flows several design cases of an ARM Cortex-M0 are implemented for comparitive study.

### Acknowledgements

First, I would like to express my great appreciation to my research and thesis advisor,

Dr. Yarui Peng, for his mentorship, direction, and encouragement. He has spent more than three

years teaching me through discussion, offering me challenges, and pushing me beyond my limits.

I want to thank him for the knowledge I have gained from his teaching, making me actively

participate in his research and academic work, the advice on the development of my research, and

the completion of this thesis.

I would like to thank Dr. David Andrews and Dr. Alexander Nelson, for taking time out of their schedules to participate in the committee for this thesis. I would like to thank Dr. Nelson for advising me during the preparation of this thesis; teaching me when I took his course; for his communication, cooperation, and understanding the problems of a graduate student when I was serving as a teaching assistant for his course. I would like to thank Dr. Andrews for teaching and helping me in the completion of the required courses for this degree. I am grateful for all the help and cooperation I have received from them when I need them most.

I want to express my gratitude to the National Science Foundation (NSF) for supporting the project that led to this thesis. NSF provided with the funding and work that allowed me to pursue my graduate degree. I also want to thank Dr. Dusan Petranovic for all his support and advice in my research. His industry affiliation, experience, and insights have helped come up with better approaches and solutions in my research. I would like to thank my colleague, Imam Al Razi, for supporting me and working with me throughout the time of this research. Imam is one of the hardest working and most persistent students I have ever worked with. He has been a mentor, an elder brother, and mostly a caring friend, who has helped make my journey easier.

Finally, I would like to thank my family and friends who have all supported me in every step of the way to achieving this goal. It would not have been possible for me to finish this degree without all of them. With far too many names to list, I would like to tell them how thankful I am for their care, support, and motivation during this journey.

# **Dedication**

To my mother, who always supported me to pursue my dreams

To my father, who always believed in me

To my brother, who showed me how not to lose hope in difficult times

To my wife, who has been by my side supporting me whenever I stumbled

This thesis and all of my achievements are the results of the care and support I have received from you all. Without your continued belief in me to succeed, I would not be where I am today.

I LOVE YOU ALL

# **Table of Contents**

| 1 | Intr | oduction | n                                                 | 1  |

|---|------|----------|---------------------------------------------------|----|

|   | 1.1  | Introdu  | action to 2.5D Systems                            | 1  |

|   | 1.2  | Need f   | For a Cross-Boundary Flow                         | 2  |

|   | 1.3  | Existin  | ng Work                                           | 4  |

|   |      | 1.3.1    | Flows for IP-reuse and Active Interposer          | 4  |

|   |      | 1.3.2    | RDL Routing Methodologies                         | 5  |

|   |      | 1.3.3    | Power Delivery and Thermal Aware Methodologies    | 6  |

|   |      | 1.3.4    | Design Flows for Security                         | 6  |

|   | 1.4  | Contri   | butions of This Work                              | 7  |

|   |      | 1.4.1    | Holistic Flow for Homogeneous Systems             | 7  |

|   |      | 1.4.2    | In-Context Flows for Homogeneous Systems          | 8  |

|   |      | 1.4.3    | Inductance-Aware System-Level Timing Optimization | 8  |

| 2 | Holi | stic Me  | thodologies                                       | 10 |

|   | 2.1  | Design   | Settings and CAD Flow                             | 11 |

|   |      | 2.1.1    | Architecture and Chiplet Partitions               | 11 |

|   |      | 2.1.2    | Technology Settings                               | 12 |

|   |      | 2.1.3    | Overall CAD Flow                                  | 13 |

|   | 2.2  | Chiple   | t-Package Co-Planning and Modeling                | 15 |

|   |      | 2.2.1    | Top-Level Planning                                | 16 |

|   |      | 2.2.2    | Pin Fan-Out and RDL Track Assignment              | 17 |

|   |      | 2.2.3    | Package Floorplan and Routing                     | 18 |

|   |      | 2.2.4    | Signal Assignment                                 | 19 |

|   |      | 2.2.5    | Package Wireload Estimation                       | 20 |

|   | 2.3  | Physic   | al Design                                         | 21 |

|   |      | 2.3.1    | Hierarchical Implementation                       | 22 |

|   |            | 2.3.2                                                     | Holistic Extraction                                                                                                                                                                                                       | 23                               |

|---|------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |            | 2.3.3                                                     | Iterative Optimizations                                                                                                                                                                                                   | 25                               |

|   | 2.4        | Two-w                                                     | yay Partition Design Study                                                                                                                                                                                                | 26                               |

|   |            | 2.4.1                                                     | Design Case Variants                                                                                                                                                                                                      | 27                               |

|   |            | 2.4.2                                                     | Holistic Analysis and Optimization                                                                                                                                                                                        | 28                               |

|   | 2.5        | Agile l                                                   | Multiway Design Techniques                                                                                                                                                                                                | 30                               |

|   |            | 2.5.1                                                     | Three-way Partition Design                                                                                                                                                                                                | 30                               |

|   |            | 2.5.2                                                     | Drop-In Approach                                                                                                                                                                                                          | 31                               |

|   |            | 2.5.3                                                     | Pay-as-You-Use Approach                                                                                                                                                                                                   | 32                               |

|   | 2.6        | Silicon                                                   | Validation with Tape-Out                                                                                                                                                                                                  | 33                               |

|   |            | 2.6.1                                                     | 2D and 2.5D System Designs                                                                                                                                                                                                | 34                               |

|   |            | 2.6.2                                                     | Shared IO Design                                                                                                                                                                                                          | 35                               |

|   |            | 2.6.3                                                     | Sign-off Verifications                                                                                                                                                                                                    | 36                               |

|   |            | 2.6.4                                                     | Chip Testing and Flow Validation                                                                                                                                                                                          | 36                               |

| 3 | In-C       | context                                                   | Methodologies                                                                                                                                                                                                             | 38                               |

|   |            |                                                           |                                                                                                                                                                                                                           | •                                |

|   | 3.1        | Design                                                    | and Technology Settings                                                                                                                                                                                                   | 39                               |

|   | 3.1<br>3.2 |                                                           | ic Reference Designs                                                                                                                                                                                                      |                                  |

|   |            | Holisti                                                   |                                                                                                                                                                                                                           | 40                               |

|   | 3.2        | Holisti                                                   | ic Reference Designs                                                                                                                                                                                                      | 4(<br>4(                         |

|   | 3.2        | Holisti<br>Per-Ch                                         | ic Reference Designs                                                                                                                                                                                                      | 40<br>40<br>42                   |

|   | 3.2        | Holisti<br>Per-Ch<br>3.3.1<br>3.3.2                       | ic Reference Designs                                                                                                                                                                                                      | 40<br>40<br>42<br>43             |

|   | 3.2        | Holisti<br>Per-Ch<br>3.3.1<br>3.3.2                       | ic Reference Designs                                                                                                                                                                                                      | 40<br>40<br>42<br>43             |

|   | 3.2        | Holisti<br>Per-Ch<br>3.3.1<br>3.3.2<br>Per-Te             | ic Reference Designs                                                                                                                                                                                                      | 40<br>40<br>42<br>43<br>45       |

|   | 3.2        | Holisti<br>Per-Ch<br>3.3.1<br>3.3.2<br>Per-Te<br>3.4.1    | ic Reference Designs  hiplet In-Context Flow  Chiplet-Package Co-Design Flow  Experimental Study  chnology In-Context Flow  Chiplet-Package Co-Design Flow                                                                | 40<br>42<br>43<br>45<br>46       |

|   | 3.2        | Holisti Per-Ch 3.3.1 3.3.2 Per-Te 3.4.1 3.4.2             | ic Reference Designs  hiplet In-Context Flow  Chiplet-Package Co-Design Flow  Experimental Study  chnology In-Context Flow  Chiplet-Package Co-Design Flow  In-Context Extraction and Post-Processing                     | 40<br>42<br>43<br>45<br>46<br>49 |

|   | 3.2        | Holisti Per-Ch 3.3.1 3.3.2 Per-Te 3.4.1 3.4.2 3.4.3 3.4.4 | ic Reference Designs  hiplet In-Context Flow  Chiplet-Package Co-Design Flow  Experimental Study  chnology In-Context Flow  Chiplet-Package Co-Design Flow  In-Context Extraction and Post-Processing  Experimental Study | 40<br>42<br>43<br>45<br>46<br>49 |

| 6 |

|---|

| - |

| 0 |

| 0 |

| 1 |

| 3 |

| 4 |

| 4 |

| 6 |

| 9 |

| 9 |

| 0 |

| 4 |

| 6 |

| 9 |

| 7 |

|   |

# **List of Figures**

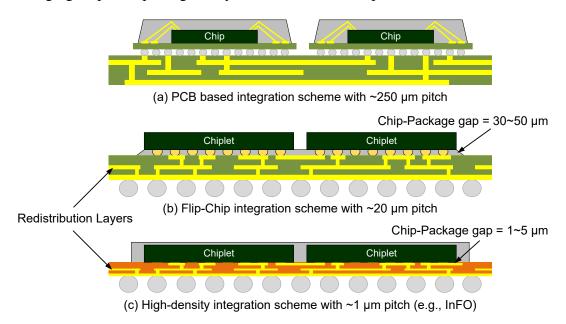

| 1  | 2.5D integration schemes: (a) PCB based system, (b) flip-chip with an organic          |    |

|----|----------------------------------------------------------------------------------------|----|

|    | interposer, (c) high-density integration scheme such as wafer-level-packaging          | 2  |

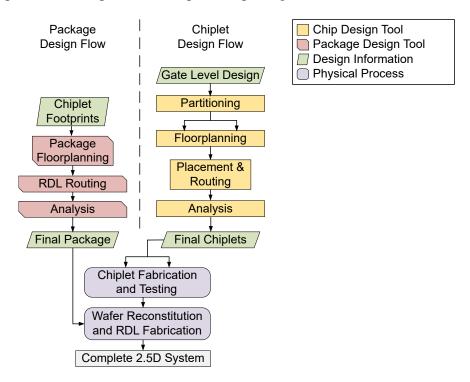

| 2  | The traditional Die-by-Die design flow of a 2.5D system                                | 3  |

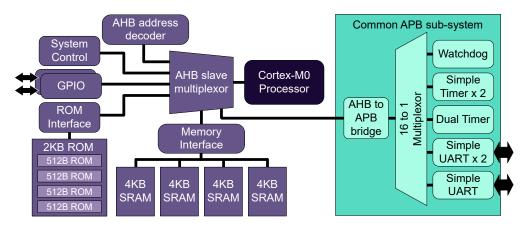

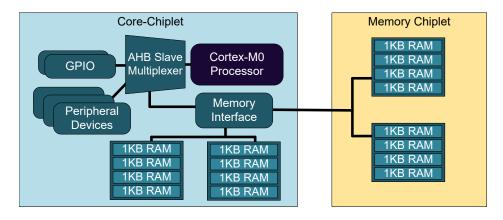

| 3  | System architecture of the ARM Cortex-M0-based microcontroller                         | 12 |

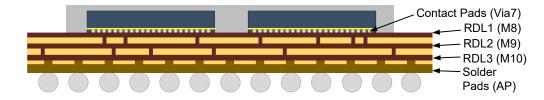

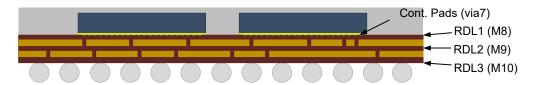

| 4  | Package redistribution layer stack of the modified 65nm PDK                            | 13 |

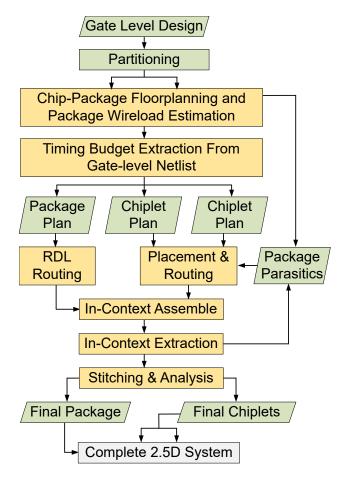

| 5  | The traditional Die-by-Die (DbD) design flow of a 2.5D system versus the holistic      |    |

|    | iterative optimization flow                                                            | 15 |

| 6  | Illustration of pin fan-out and track assignment of a chiplet with 6×6 pin grid and    |    |

|    | two RDLs                                                                               | 16 |

| 7  | Illustration of the floorplanning strategy: (a) A selected solution that satisfies the |    |

|    | pin connectivity requirement, (b) a rejected floorplan while finding the relative      |    |

|    | location                                                                               | 19 |

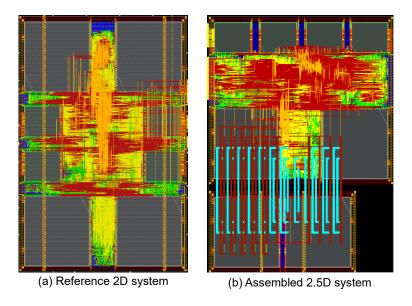

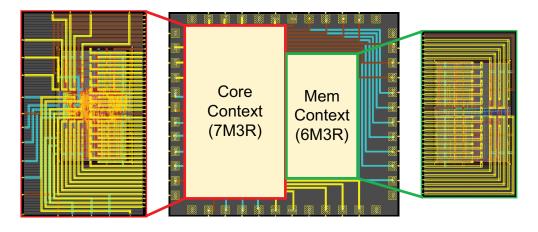

| 8  | Design layouts of (a) reference 2D system, (b) assembled 2.5D system with chiplet      |    |

|    | and package layers, (c) designs of Core-Chiplet (top) and Mem-Chiplet (bottom),        |    |

|    | and (d) Zoomed-in view of the assembled design                                         | 22 |

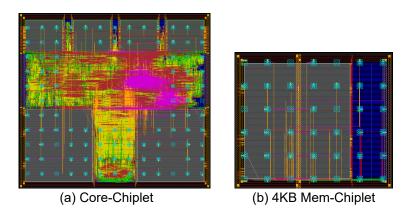

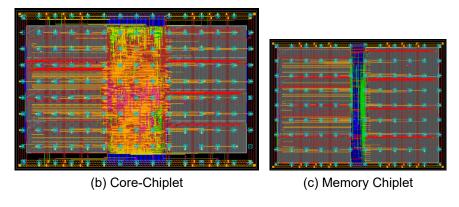

| 9  | Layouts of the chiplets for the three-way partition design study                       | 31 |

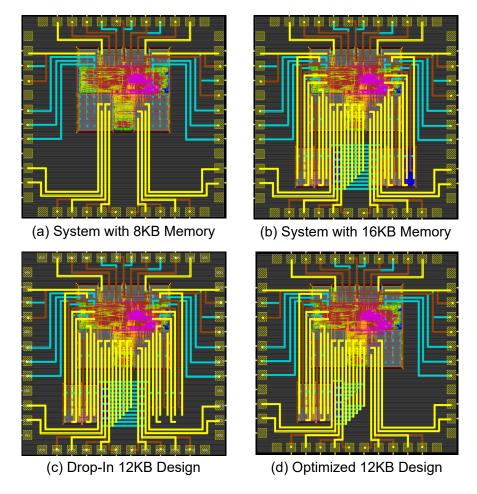

| 10 | Design layouts of (a) Core-only system with 8KB memory, (b) optimized full sys-        |    |

|    | tem with 16KB memory, (b) 12KB design using the Drop-in approach, and (d)              |    |

|    | Optimized 12KB design using Pay-as-You-Use approach                                    | 32 |

| 11 | System designs for tape-out: (a) Reference 2D system, (b) assembled 2.5D system.       | 34 |

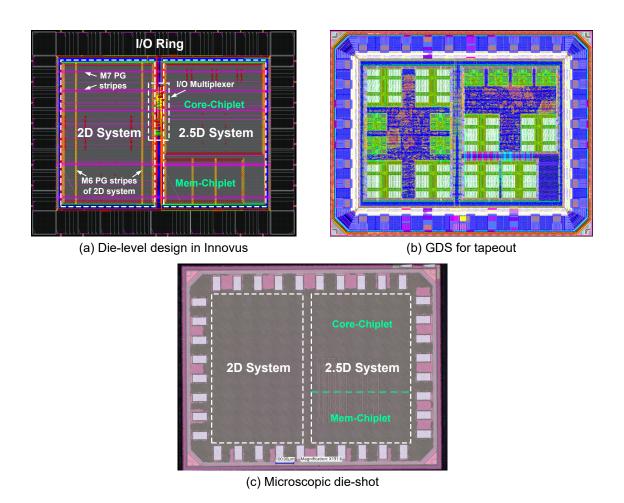

| 12 | Final design for tape-out and the fabricated die: (a) Die-level design, (b) combined   |    |

|    | GDS for tape-out, (c) microscopic image of the taped-out die                           | 35 |

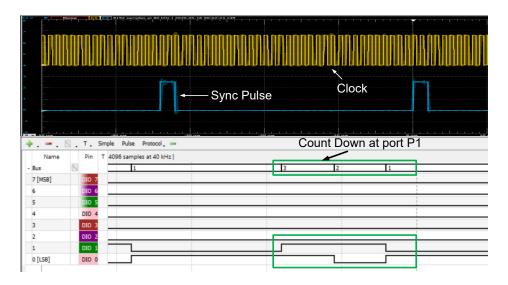

| 13 | Chip testing waveforms from the logic analyzer                                         | 36 |

| 14 | Package redistribution layer stack of the modified Nangate45 PDK                       | 39 |

| 15 | System architecture and chiplet partitions of the Cortex-M0-based reference design     | 39 |

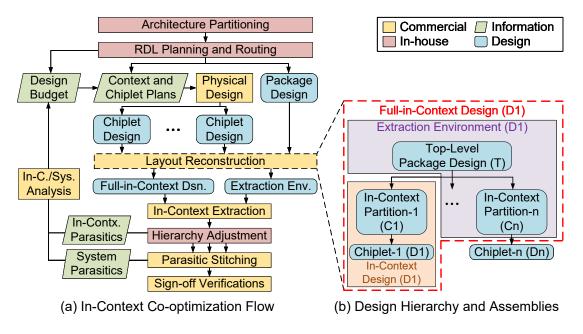

| 16 | Per-chiplet in-context flow for heterogeneous systems                                 | 43 |

|----|---------------------------------------------------------------------------------------|----|

| 17 | Layouts of the in-context chiplets for heterogeneous integration                      | 45 |

| 18 | Per-technology in-context co-optimization flow for heterogeneous 2.5D systems         | 46 |

| 19 | Chiplets and assembled package layouts of the homogeneous 2.5D system                 | 49 |

| 20 | Layouts of the assembled heterogeneous system for in-context extraction               | 52 |

| 21 | Package and assembled system layouts of the experimental homogeneous and het-         |    |

|    | erogeneous 2.5D systems                                                               | 53 |

| 22 | Timing-accurate scalable in-context flow for heterogeneous 2.5D systems               | 54 |

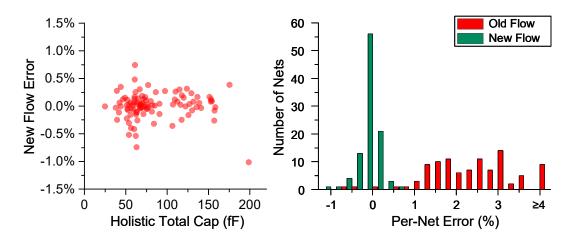

| 23 | Comparison of the total capacitance on individual nets of the this flavor of the flow |    |

|    | with per-chiplet in-context flow                                                      | 57 |

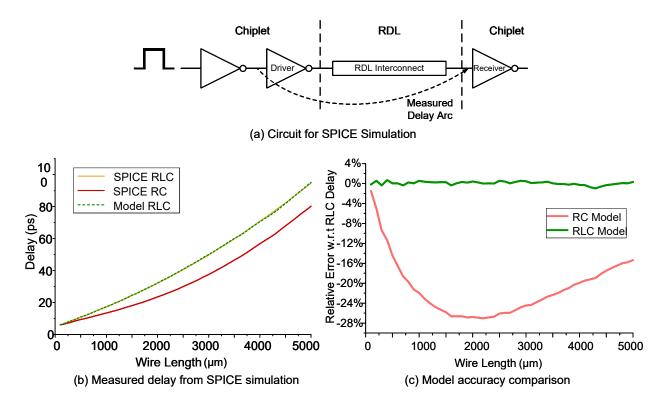

| 24 | SPICE simulation and validation of the proposed model                                 | 61 |

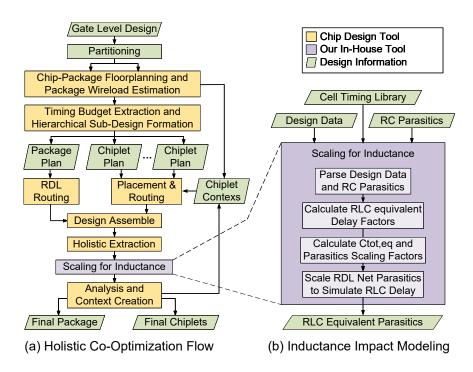

| 25 | Holistic co-optimization flow with RDL inductance impact on timing                    | 65 |

| 26 | Physical design layouts of chiplets and the package                                   | 70 |

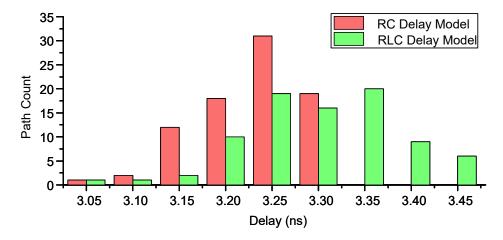

| 27 | Timing path count per 0.05 ns delay bin through RDL                                   | 71 |

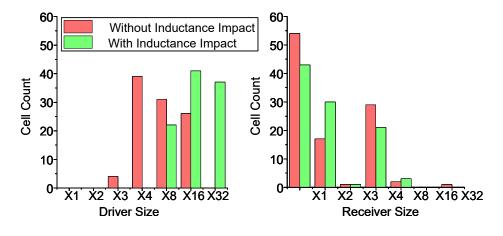

| 28 | Package inductance impact on cell size distribution                                   | 71 |

|    |                                                                                       |    |

# **List of Tables**

| 1  | Technology parameters of the modified 65nm layer stack                                 | 1.3 |

|----|----------------------------------------------------------------------------------------|-----|

| 2  | Holistic capacitance (in fF) extraction results                                        | 24  |

| 3  | Comparison of Holistic vs. Die-by-Die ground (GCAP) and coupling (CCAP)                |     |

|    | capacitance extraction results (in fF)                                                 | 25  |

| 4  | Analysis result comparison of the microcontroller system                               | 29  |

| 5  | Comparison of three-way partition design cases                                         | 33  |

| 6  | Parameters (in µm) of the modified Nangate45 PDK routing layers                        | 39  |

| 7  | Analysis results of reference designs implemented in the holistic flow                 | 41  |

| 8  | Comparison of Holistic (Holi) vs In-Context (In-C) ground (GCAP) and coupling          |     |

|    | (CCAP) capacitance extraction results (in fF) of Case-3 final homogeneous design.      | 44  |

| 9  | In-Context heterogeneous design results with 7M3R Core Chiplet in Nangate45            |     |

|    | and 6M3R Mem Chiplet in gscl45.                                                        | 44  |

| 10 | Coupling and ground capacitances (in fF) between routing layers in holistic extraction | 48  |

| 11 | Comparison of Holistic (Holi) vs. In-Context (In-C) ground (GCAP) and coupling         |     |

|    | (CCAP) capacitance extraction (in fF)                                                  | 51  |

| 12 | Per-net accuracy comparison of inter-chiplet package wires                             | 51  |

| 13 | In-Context heterogeneous design results with 7M3R Core-Chiplet in Nangate45            |     |

|    | and 6M3R Mem-Chiplet in gscl45.                                                        | 52  |

| 14 | Comparison of holistic (Holi) vs. in-context (In-C) coupling (CCAP) and total          |     |

|    | (Total CAP) capacitance extraction (in fF)                                             | 57  |

| 15 | Comparison of holistic and in-context flow optimization results of the experimental    |     |

|    | designs                                                                                | 58  |

| 16 | Model parameters for selected Nangate45nm cells                                        | 66  |

| 17 | Changes in receivers between RC and RLC Designs                                        | 72  |

## Chapter 1

#### Introduction

The demands for increased functionality and performance in emerging technologies, such as 5G, Artificial Intelligence, and high performance computing have pushed modern chips to the brink of the reticle limit. The industry responses with a modular design approach, in which a large system is broken down into smaller modules and then integrated as a whole system on the package. Traditionally, a Printed-Circuit-Board (PCB) is used as the integration platform. PCBs are cheap and easy to design. However, they suffer from high inductance and capacitance because of long and wide traces, thereby limiting bandwidth and increasing power loss. In the past few decades, the electronic packaging technology has been through substantial development. Starting from the dual in-line package (DIP), the packaging technology has evolved through quad flat package (QFP), ball-grid array (BGA), chip-scale package (CSP), etc. and today offers high-density, high-bandwidth, and energy-efficient 2.5D and 3D packaging solutions

#### 1.1 Introduction to 2.5D Systems

A multi-chip 2.5D system consists of multiple dies (chiplets), which are interconnected through redistribution layers (RDLs) on an interposer. Fig. 1 (b) and (c) show examples of two-chiplet 2.5D systems. Fig. 1 (b) shows a flip-chip package, while Fig. 1 (c) shows a bump-less wafer-level package (WLP). A 2.5D integration package may use different materials like glass, slilicon, and polymer as interposer [1]. 2.5D systems have overcome several drawbacks of traditional PCB-based systems and are providing energy efficient inter-die transmission and high-density integration options. With transistor scaling saturated, these 2.5D designs are becoming popular in high-density applications like mobile phones and tablets [2]. Moreover, 2.5D packaging enables heterogeneous integration [3, 4] and high-bandwidth inter-die communication [5]. It also offers promising hardware security applications [6, 7]. The increasing interests are driving the industry to develop compact and high-performance 2.5D packaging solutions [8]. In the last few years, the

industry has developed several 2.5D integration technologies like eWLB [9], SWIFT [10], and InFO [11]. In every iteration of these technologies, the packages wires become thinner and denser, bringing chips and packages very close with a reduced pad size.

Figure 1: 2.5D integration schemes: (a) PCB based system, (b) flip-chip with an organic interposer, (c) high-density integration scheme such as wafer-level-packaging

## 1.2 Need for a Cross-Boundary Flow

In the traditional flow, 2.5D systems are designed in a die-by-die (DbD) approach where each chiplet is designed independently as a single unit, and then all chiplets are mounted on the package as a complete system. The analysis and optimization of chiplets and the package are also conducted separately without consideration of the interactions between them [12, 13]. Fig. 2 illustrates this traditional flow in which chiplets and the package never interact with each other until they are fabricated and assembled. During package design, a chiplet is approximated as a ground mesh or plane. In this approach, it is possible to achieve the shortest possible turn-around time using off-the-shelf chiplets in a plug-and-play manner [12]. This flow is sufficient when the gap between chiplets and the package is large enough to make the interactions between them minimal. As shown in Fig. 1(b), in flip-chip WLP, this gap is around 30μm~50μm. In such

integration technologies, the traditional flow can be used without any critical problem. However, due to the industry's aggressive development and the adoption of bumpless contact pads [4], this gap is decreasing rapidly [14, 15, 16, 17]. Within a few years, this gap is reduced from tens of µm to 1.5 µm [16]. At such a small separation, significant capacitive and inductive coupling is expected between chip and package routing layers. To handle such high-density integration schemes, a cross-boundary design flow is required, which can capture these interactions during design and optimization steps of both chiplet and package.

Figure 2: The traditional Die-by-Die design flow of a 2.5D system

In the die-by-die approach, the complete system is not considered as a whole. Therefore, it is not possible to obtain a globally optimized system, though individual chiplets may perform well. Because of the pin-dominated nature of package routing, it can get overly complicated, introducing unnecessary package overhead due to detours if chiplet pins are not planned properly. As all the chiplets work together as a single system, timing optimizations need to be performed at the system level. While planning the package, it may be necessary to rearrange the chiplets pin configurations to obtain a compact package routing to minimize package wire delays. The

post-design analysis tools need to consider chiplets and package interactions to avoid signal reliability issues, potentially causing system failure.

In addition, some designs are intrinsically very small in area and power budget, such as IoT devices. Having a large/high-performance IO system will create too much overhead for such system to be implemented with multiple chiplets. One solution is to allow highly-customized IO interface to be used between chiplets which can be simplified into a few standard cells. However, as these cells are not designed for driving long RDL wires with many technology variations, parasitics and STA analysis must be performed very carefully to avoid potential violations. To overcome these challenges, it is essential to design a CAD method for low-cost IO systems that reduces timing and power overheads but still captures all couplings between the chiplet and package to ensure all design constraints are met.

# 1.3 Existing Work

In recent years, 2.5D system design methodologies have gained significant attention of both industry and academic researchers. There are existing studies that investigate different aspects of 2.5D system design. The design methodologies are investigated from different perspectives like IP-reuse, active interposer-based integration, RDL routing, Power Delivery Network (PDN), thermal issues, security, etc. This section outlines some of the recently published work in this area, which are most relevant with this thesis.

#### 1.3.1 Flows for IP-reuse and Active Interposer

2.5D integration platforms enable plug-and-play design approach through chiplet-based IP reuse. A complete system can be built through integration of off-the-shelf homogeneous or heterogeneous chiplets on the interposer in a very short time. A vertically integrated design flow for chiplet creation and integration utilizing 2.5D platforms was presented in [12]. They proposed a new protocol called Hybrid-Link for communication between chiplets that can be utilized in the plug-and-play design approach.

The 2.5D integration platform can utilize either active or passive interposer. A passive interposer contains only inter-chiplet interconnects and possibly some passive elements like capacitor, inductor, etc. An active interposer can have logic devices in addition to interconnects and passive devices. A design flow for active interposer-based 2.5D systems was presented in [18]. The flow utilizes chip design and analysis tools to design the active elements in the interposer.

Both of the works presented complete flows for 2.5D system design, which accomplishes their respective design goals, IP-reuse and active interposer design. They also explored some co-design approaches. However, none of the flows tries to capture the chiplet-package cross-boundary interactions and study their impact on the system performance.

# 1.3.2 RDL Routing Methodologies

Though 2.5D integration is a packaging technology, it uses ultra-fine pitch similar to the backend-of-the-line (BEOL) processes. As a result, traditional packaging tools cannot handle the complexity. Though chip design tools can handle the design complexity, existing methodologies for chip routing are not suitable for certain package design features, like any-angle routing, variable pad and trace width, irregular pad structures, etc. As a result, active research is going on to address the RDL routing problem.

A unified routing framework that can handle both grid-based and gridless routing on RLDLs was proposed in [19]. This work employs the modulus-based matrix splitting iteration method (MMSIM) and a bipartite matching algorithm in their methodology. Methodologies to handle routing problems with pre-assignment and via-based multi-chip multi-layer high-density 2.5D packages with irregular pad structures was proposed in [20]. This work proposes an algorithm to perform single-layer concurrent routing and an octagonal tile model. The tile model can handle triangles, rectangles, and trapezoids with 45°, 90°, and 135°interior angles.

Both of the works proposes novel routing methodologies to tackle the RDL routing problem.

These methodologies have great performance in terms of routability, total wirelength, and

runtime. However, these work lack the study of the impact of those methodologies at the system level.

# 1.3.3 Power Delivery and Thermal Aware Methodologies

In a 2.5D system, the power delivery network design is very important because it affects the IR-drop of chiplet designs. At high frequency, the power delivery network needs to be characterized accurately. A methodology for co-design, co-anlysis, and the system-level optimization of chiplet and interposer PDN is proposed in [21]. High-density package with closely packed chiplets suffer from thermal-based failures if the chiplets have high power densities. A thermally-aware chiplet placement methodology for heterogeneous 2.5D systems was proposed in [22]. This work proposes a simulated annealing-based placer that strategically inserts spacing between chiplets to jointly minimize the peak temperature of the overall system and the total inter-chiplet network wirelength. Both of these flows target very specific aspects of the 2.5D system design.

# 1.3.4 Design Flows for Security

2.5D integration platforms offer some great hardware IP security features. Some research has been conducted on this ground. A security-aware physical design flow for 2.5D systems was proposed in [6] that can prevent IP piracy. The methodology obfuscates the details of the design in the out-sourced part of the system through careful partitioning and placement. Methodologies to implement security features for network-on-chip (NoC) architectures were proposed in [18]. The security scheme implements a trustworthy communication backbone to prevent threats like snooping of communication, spoofing identifiers, malicious access or modification of data in shared memory, etc. and offers runtime monitoring of system-level memory requests.

#### 1.4 Contributions of This Work

In this work, chiplet-package co-design and optimization flows and methodologies are presented that employ a cross-boundary strategy to design chiplets and the package together. In these flows, chiplets and the package (at least part of it) are assembled in a common design environment during planning and analysis steps for holistic consideration. This shared layout database allows exchanging necessary cross-boundary design information to capture coupling and mutual interactions, which is essential to achieve high analysis accuracy, co-optimization of the chiplets, and reliable system design.

The effectiveness and flexibility the proposed flows are illustrated through the study of several 2.5D design cases of an ARM Cortex-M0 based microcontroller system. To verify that the flows are compatible with the existing foundry model and industry standard tools, a chip was designed using one of the proposed flows in TSMC 65nm technology. The contributions listed below are the direct result of this work.

- 1. An ASIC-CAD-compatible holistic flow that can design, optimize, and analyze homogeneous 2.5D systems with high-density FOWLP technologies,

- 2. Three flavors of cross-boundary in-context flow for design, optimization, and analysis of heterogeneous 2.5D systems,

- (a) A scalable per-chiplet in-context flow,

- (b) A highly accurate per-technology in-context flow,

- (c) A timing-accurate scalable in-context flow,

- 3. Package inductance-aware system-level cross-boundary timing optimization methodology

# 1.4.1 Holistic Flow for Homogeneous Systems

In all of the existing tool flows discussed in Section 1.3, the die-by-die design, analysis, and optimization flows are employed. Some co-design is achieved through manual transfer of design

information. To achieve a globally optimized system through co-design, a tool flow with inherent exchange of chiplet-package cross-boundary design information is essential. The holistic 2.5D chiplet-package co-design and optimization flow presented here employs a cross-boundary strategy to design chiplets and the package together. In this flow, chiplets and the package are assembled in a common design environment during planning and analysis steps for holistic consideration. This shared layout database allows exchanging necessary cross-boundary design information to capture coupling and mutual interactions, which is essential to achieve high analysis accuracy, co-optimization of the chiplets, and reliable system design. This flow has been silicon verified through tape-out of a system in TSMC 65nm technology.

## **1.4.2** In-Context Flows for Homogeneous Systems

Since the holistic flow requires to assemble the chiplets into a unified design environment, it cannot be applied to heterogeneous systems where the device stack are different. At the present, no standard computer aided design (CAD) flows support including two different technology files into a single physical design tools. Therefore, the in-context design flows are presented, which allows an arbitrary number of chiplets in different technologies integrated with chiplet-package coupling considered altogether. It is completely compatible with all standard ASIC tools for design, extraction, and analysis. The three flavors mentioned above offers trade-off between analysis accuracy and scalability. These flavors can be utilized together to design and analyze a single system at different stage of the design process.

# 1.4.3 Inductance-Aware System-Level Timing Optimization

Traditionally, chip-scale interconnects are modeled using resistive and capacitive (RC) elements. Several previous studies have discussed the impact of inductive (L) elements of interconnects at the high-frequency range. It is essential to take into account the inductive behaviors of the RDL wires to ensure system reliability and signal integrity of a high-performance 2.5D system with long interconnects. A system-level analysis and optimization flow has been presented for

chiplet-package co-optimization, which takes into account the inductive effects of RDL wires on the system performance. This flow can automatically co-optimize the IO drivers and receivers between chiplets taking into account the timing overhead introduced by the inductive behavior of the RDL wires. This analysis and optimization flow can be used a a part of the holistic and in-context flows to perform inductance-aware design of both homogeneous and heterogeneous 2.5D systems.

# Chapter 2

# **Holistic Methodologies**

Apart from heterogeneous integration, 2.5D integration technology enables the chiplet design approach. A large ASIC chip can be partitioned into smaller chiplets in order to increase yield through the use of the Known-Good-Dies [23]. In such systems, to ensure reliable inter-chiplet communication, an additional stage in the pipeline, like SerDes [3, 15], would be necessary to hide IO overhead. This would require changes at the architecture level. Changes in architecture require sufficient engineering efforts and are not so quick and flexible. The traditional method is to carefully design an IO interface and an architectural change in the pipeline depth and timing requirement. This is a complicated process that takes a few months ahead for planning and implementation. Though this is not an issue for large design houses, small ASIC design companies may not have enough resources and time for such architecture exploration. In that case, a large engineering design margin needs to be left such that the IOs from different chiplets can communicate with each other within the design tolerance. Novel IO designs [24, 25] have been proposed for 2.5D systems, which will significantly reduce the IO overhead and power consumption. However, as these cells are not designed for driving long redistribution layer (RDL) wires with many technology variations, parasitic extraction and static timing analysis (STA) must be performed very carefully to avoid potential violations to the overall system performance and signal integrity issues.

To enable agile customization without the need for a complete re-design, all parts in a 2.5D system must be considered holistically as much as possible. In this chapter, a holistic chiplet-package co-design and optimization flow is presented that facilitates the exchange of chiplet-package cross-boundary design information to obtain a globally optimized system with the highest system reliability. In this co-optimization methodology, all chiplets are automatically adjusted, making trade-offs among themselves for the package overhead. The holistic flow takes care of the co-optimization parts and offers flexibility and speed to explore different chipletization

and package design schemes without touching the system architecture. Through the use of all standard libraries to design custom pin drivers, it achieves zero overhead on pipeline depth and minimizes the timing and power overhead.

Through the study of several 2.5D design cases of an ARM Cortex-M0 based microcontroller system, the effectiveness and flexibility of the flow has been illustrated. To verify the flow in silicon, a chip that is designed using the flow is taped-out and studied in TSMC 65nm technology. This chapter presents an ASIC-CAD-compatible holistic flow that can design, optimize, and analyze 2.5D systems with high-density FOWLP technologies, a study of the necessity and effectiveness of holistic extraction and STA on 2.5D systems designed in commercial technologies, illustration of design flexibility and speed offered by the holistic flow with both drop-in and pay-as-you-use design strategies, and silicon validation of the flow with a 2D/2.5D tape-out design in TSMC 65nm technology.

# 2.1 Design Settings and CAD Flow

In this section, the overall holistic flow is briefly introduced. As an illustration, an ARM Cortex-M0 based microcontroller system is designed with a modified TSMC 65nm PDK. The architecture and the modified settings are also presented.

#### 2.1.1 Architecture and Chiplet Partitions

Fig. 3 shows the system architecture of the microcontroller system. It has an ARM Cortex-M0 processor core connected to the rest of the system through AMBA High-performance Bus (AHB). The AHB bus is connected to the system controller, two GPIO modules, a ROM table, the memory interface, and an Advanced Peripheral Bus (APB) sub-system. The APB sub-system consists of a watchdog timer, two simple timers, a dual-timer, UART modules, etc. The system has a total of 16KB memory divided into four 4KB banks. The memory interface is designed in a way that each bank occupies a contiguous address range. As a result, the system can operate even if some of the memory banks addressed by the upper address range are not present. RAM and

ROM macros are compiled using ARM memory compilers.

Figure 3: System architecture of the ARM Cortex-M0-based microcontroller

To implement the microcontroller as a 2.5D system, it is partitioned into two chiplets. Several partitioning algorithms and design schemes were studied to understand the impact of package wires during the partition stage. The area-balanced partitions using hMetis [26] and FLARE [27] algorithms, logic-vs-memory scheme, and Architecture-Aware scheme are compared. In the balanced-area and logic-vs-memory partitions, the chiplet areas are not sufficient to accommodate all the pins. In the Architecture-Aware partition scheme, the knowledge of architecture is used to come up with a partition in which the chiplets can accommodate all of their pins with reasonable pin-pitch. The Architecture-Aware partition scheme is used for the experimental studies presented in the latter part of this chapter. This scheme helps illustrate the Drop-in design approach, which allows several flavors of a 2.5D system with zero design cost. In this partition scheme, all core logic and 8KB of memory residing in the lower 8K address range are gathered into a Core-Chiplet. In the other Mem-Chiplet, only the rest of 8KB of memory is kept with a few control logic. As a result, the Core-Chiplet can operate as a standalone system with or without the Mem-Chiplet.

# 2.1.2 Technology Settings

TSMC 65nm technology is used to implement a 2D design and 2.5D chiplets. In this holistic flow, a unified environment is needed where both chiplet and package designs can be imported together

for holistic planning and extraction. Moreover, there is no publicly available PDK to design 2.5D packages for academic study. Therefore, the PDK is modified to create a unified chiplet-package co-design environment with all chiplet and package layers together.

| Table 1: Technol | logy parameters | of the modified  | l 65nm layer stack    |

|------------------|-----------------|------------------|-----------------------|

| radic 1. recilio | ogy parameters  | of the inounited | i osiiiii layei stack |

| Layer | Purpose                   | Width       | Spacing | Thickness | Epsilon |

|-------|---------------------------|-------------|---------|-----------|---------|

| M1-M7 | Chip Internal Routing     | TSMC        | TSMC    | TSMC      | TSMC    |

| ILD7  | Inter-layer Dielectric    | -           | -       | 5 μm      | 2.0     |

| M8    | RDL1                      | 10 μm       | 10 μm   | 5 μm      | 2.2     |

| ILDR1 | Inter-layer Dielectric    | -           | -       | 5 μm      | 2.0     |

| M9    | RDL2                      | 10 μm       | 10 μm   | 5 μm      | 2.2     |

| ILDR2 | Inter-layer Dielectric    | -           | -       | 5 μm      | 2.0     |

| M10   | RDL3                      | 10 µm       | 10 μm   | 5 μm      | 2.2     |

| PP    | <b>Planar Passivation</b> | -           | -       | 1 μm      | 4.0     |

| AP    | Solder Pads               | <b>TSMC</b> | TSMC    | TSMC      | TSMC    |

Figure 4: Package redistribution layer stack of the modified 65nm PDK

Table 1 shows the settings of the modified PDK. The lower seven metal layers (M1-M7) are used with their original settings for chiplet internal routing. The parameters of M8, M9, M10, and the relevant dielectric layers are modified to mimic the attributes of TSMCs InFO package routing layers. Though the most advanced InFO flavors can handle 0.8 μm/0.8 μm width/spacing [17], 10 μm/10 μm is used for a general setup. Fig 4 shows the layer stack of the modified PDK. For holistic extraction, this technology stack is characterized to generate an extraction-rule file. In an industrial design, this extraction-rule file would be provided by the packaging house through characterization of the chiplet-package technology combination they support.

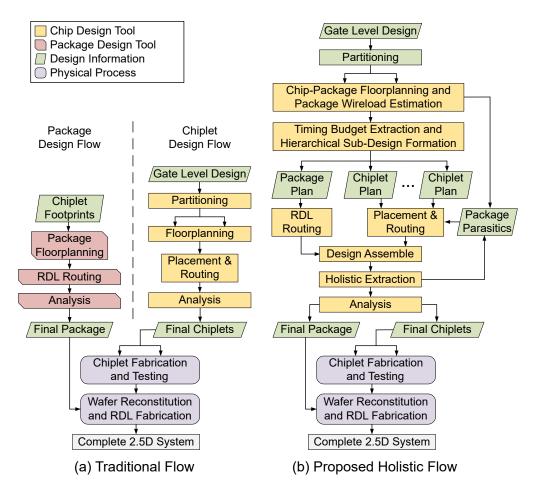

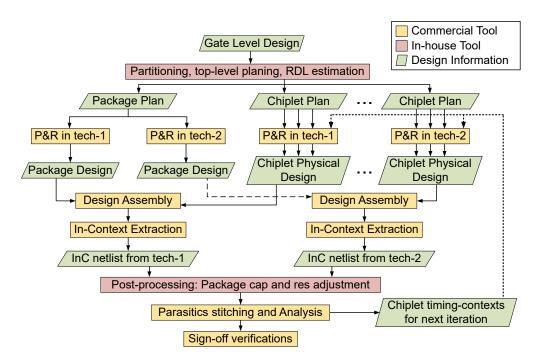

#### 2.1.3 Overall CAD Flow

The overall flow is illustrated in Fig. 5(b). When the RTL netlist is ready, the gate-level netlist is synthesized using a standard synthesis tool. The gate-level netlist is then fed to the partitioning

tool along with the partition scheme settings. The partition tool takes into account the impacts of package wires on chiplet partitions. Next, we prepate the top-level plan of chiplets and the package together in the same design environment set up with the unified PDK. We determine package floorplan and chiplet pin arrangement with an algorithm that reduces the package routing issues like long wires or detours and minimize package wire impacts on system performance. Next, we generate an initial package routing and estimate the package wireload on chiplet IO pins. We perform timing budget extraction of all chiplets and the package. Then, we split the overall design into individual chiplet and package sub-designs for parallel implementation. In Fig. 5(b), the "Chiplet Plan" boxes refer to plans of different chiplets, one plan for each chiplet. Though these chiplet plans are related through the top-level constraints, each plan is independent and all plans can be implemented in parallel.

After co-planning and RDL routing, chiplets and the package can be implemented independently with contexts and constraints propagated from the top level. Package design is performed utilizing the chiplet footprints, their connectivity, and the timing budget of package wires. The physical design of each chiplet is similar to the traditional 2D chip design flow with some additional constraints imposed by the top-level plan. After placement and routing, Design Rule Checking (DRC) is performed on all chiplets individually. If all chiplets pass the DRC, the entire system is assembled together for further optimizations and analyses.

The Design Assemble step combines chiplet and package designs into the same unified design environment as in the top-level planning stage. Because of this, optimization and analysis can capture chiplet-package interactions and perform adjustments to improve system performance and reliability. Holistic extraction is performed and the result is used for STA and timing context generation. These timing contexts are used to perform the next iterations of individual chiplets. This holistic optimization using standard tools improves system performance with buffer resizing, time borrowing, re-routing, etc. Following iterations can be carried out if there is a scope of improvement, but with a good estimation at the beginning, the second iteration is generally accurate enough. Finally, all the finished designs are assembled for full-system extraction,

Figure 5: The traditional Die-by-Die (DbD) design flow of a 2.5D system versus the holistic iterative optimization flow

analysis, and sign-off verifications.

# 2.2 Chiplet-Package Co-Planning and Modeling

In 2.5D systems, RDL and package planning is critical to minimize inter-chiplet signal delays due to package wires. Otherwise, even though the chiplets may obtain very high performance individually, the overall system will perform poorly due to timing bottlenecks through package wires. As the package routing is highly dependent on chiplet pin configurations, they need to be planned together. At this step of the flow, the package floorplan, RDL routing, and chiplet pin configurations are optimized in a holistic way to minimize the impact of package wire delay on the overall system performance.

Figure 6: Illustration of pin fan-out and track assignment of a chiplet with  $6\times6$  pin grid and two RDLs.

## 2.2.1 Top-Level Planning

The RDL routing problem of a 2.5D package is different from the conventional chip routing problem. Existing works [28, 20, 19] try to solve the routability between chiplet pins in the system. However, compared to the chip routing problem, the number of nets on the package level is much fewer, and signal integrity issues are mainly caused by skewed long wires. As a result, minimizing total wire-length is not always the primary concern. Several other factors like bus delay skew, signal-integrity, the inductive effect of long package wires, EMI effects, etc. can play a critical role. All these factors can be considered in the top-level planning stage of a 2.5D system. A strategy is presented, which focuses on developing a compact RDL routing plan with short and uniform wire-lengths to minimize routing issues like congestion, detours, and unequal bus wire delays between chiplets.

Chiplet dimensions and pin pitch are determined based on the chiplet area and pin count. In the experimental implementation, the Core-Chiplet has dimensions  $520 \, \mu m \times 475 \, \mu m$  and a total

of 100 pins. The Mem-Chiplet has dimensions 415  $\mu$ m $\times$ 230  $\mu$ m and a total of 60 pins. The pins of the Core-Chiplet are arranged in a  $10\times10$  grid and those of the Mem-Chiplet are arranged in a  $6\times10$  grid. In both chiplets, the pin pitch is 40  $\mu$ m in both directions of the grid. Without loss of generality, two chiplets are considered at a time in the co-planning step. In this strategy, signals are assigned to chiplet pins after the package floorplan and routing are determined. The top-level package and chiplet plans are determined through pin fan-out of chiplets, RDL track assignment, package floorplanning and routing, slack-based greedy signal assignment of package wires, and package wireload estimation. Algorithm 1 describes our co-planning strategy.

# Algorithm 1: RDL Planning Algorithm

- 1 Calculate area required for the chiplets

- 2 Generate pin array based on pin pitch and chiplet area

- 3 *sideOrder* = [near cut-line, top, bottom, opposite side]

- 4 *layerOrder* = [RDL layers from bottom to top]

- 5 foreach Chiplet do

- foreach s in sideOrder do

- 7 | foreach l in layerOrder do

- 8 Route pins to the Boundary Points of s on l

- Sort *BoundaryPoints* in increasing order of their distance from cut-line

- foreach bp in BoundaryPoints do

- 11 Assign the nearest available track to bp

- 12 while Floorplan not valid do

- 13 | Floorplan = New relative position of the chiplets

- 14 Check if Floorplan is valid

- 15 Connect pin pairs routed to the same track

- 16 AssignSignals(Tracks, Nets, Slack)

- 17 WireLoadEst(Tracks, PDK.WireLoadModel)

- 18 Generate TCL script and SDC files

# 2.2.2 Pin Fan-Out and RDL Track Assignment

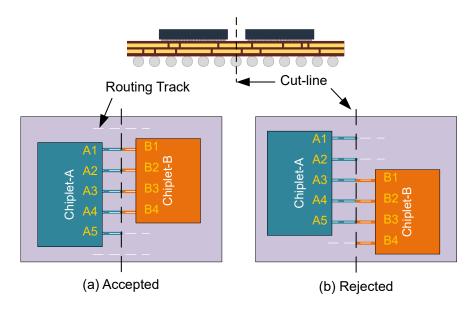

Before a chiplet pin can be routed externally, it needs to cross its chiplet boundary. A greedy strategy is used to fan out and track the chiplet pin assignment, which tries to use short and straight wires within a minimum number of package layers. In Algorithm 1, lines 5-11 show the pin fan-out and track assignment strategy. For the sake of illustration and explanation, a cut-line is

assumed between two chiplets, as shown in Fig. 7. This cut-line acts as the routing target in this step. As many internal pins as possible are brought to the chiplet boundary using all the RDL routing tracks that cross the boundary. The boundary locations where the pins are routed to are named as "Boundary Points." This is performed in a specific order on all sides of the chiplet. For each side, the layer touching the contact pads is routed first, followed by the subsequent RDLs. From line 3 of Algorithm 1, the side order is determined based on their rough distance from the cut-line. The number of rows/columns of pins that can be routed to boundary points depends on the pin pitch in terms of the package routing track. As shown in Fig. 6, if the pin pitch is two tracks, two rows/columns of pins adjacent to that side can be routed to the Boundary Points following those tracks.

Next, tracks are assigned to these Boundary Points. Boundary Point closest to the cut-line is assigned with its nearest track first. From line 9 of Algorithm 1, Boundary Points are sorted based on their distances from the cut-line. As a result, in the track assignment queue, the Boundary Points facing the cut-line comes first, followed by Boundary Points on the perpendicular side and the opposite side, sorted in increasing order by their distances to the cut-line. The opposite side is least preferred because of the detours introduced to reach the cut-line. Fig. 6 shows the pin fan-out and track assignment of a chiplet with a  $6\times6$  pin grid and two package layers.

# 2.2.3 Package Floorplan and Routing

Based on the track assignment of chiplets, their relative locations are determined. These relative locations will determine the package floorplans, chiplet connectivity, and RDL routing. In the current strategy, a relative position is accepted between the chiplets that can produce sufficient overlap of the tracks to allow all their connections. Lines 12-14 of Algorithm 1 describe the strategy to determine the package floorplan.

Fig. 7 illustrates this strategy for connecting four pins between the chiplets using only one RDL, where the dashed white lines show available tracks crossing the cut-line. The thick lines connected to chiplets represent assigned tracks to chiplet pins. The track assignment strategy

Figure 7: Illustration of the floorplanning strategy: (a) A selected solution that satisfies the pin connectivity requirement, (b) a rejected floorplan while finding the relative location

routes the pins of Chiplet-A and Chiplet-B to their nearest tracks crossing the cut-line separately. Next, while exploring different possible relative positions between chiplets, the floorplans similar to Fig. 7(b) are rejected as those have insufficient track overlap for four connections. Among two viable solutions, in this case, the floorplan in Fig. 7(a) is chosen arbitrarily, which supports the number of connections between the chiplets. After finding the relative position, the connectivity among the pins of the two chiplets is defined, which are routed to the same track crossing the cut-line. In this example, pin A1 of Chiplet-A to pin B1 of Chiplet-B are connected because they are routed to the same track. Similarly, pins A2, A3, and A4 of Chiplet-A will be connected to pins B2, B3, and B4 of Chiplet-B, respectively. Unconnected pins of the chiplets, like pin A5 of Chiplet-A, can be used to connect with some other chiplets or to act as external I/O.

# 2.2.4 Signal Assignment

With the connectivity defined, both chiplet floorplan and pin assignment can be prepared in compliance with the rest of the package plan. One way to perform the signal assignment would be based on chiplet floorplans. In this strategy, a designer can prepare some initial floorplans and assign signals to the pins. Another way would be to determine the signal assignment of the chiplet

pins based on timing requirements and then adjust chiplet floorplans to best-suite the pin configurations. The latter approach is followed here and a greedy algorithm is applied for the signal assignment. The AssignSignals() function in Algorithm 2 describes the signal assignment strategy. Performing STA analysis on the synthesized gate-level netlist, timing slacks of all package wires are collected. Based on the floorplan and routing obtained in the previous steps, all track lengths connecting chiplet pins are calculated. As shown in lines 4-5, tracks and nets are sorted by their lengths and slacks, respectively. As a result, in lines 7-9, the net with the smallest slack is assigned to the track with the shortest length. This greedy strategy assigns timing-critical nets to shorter package wires and thus minimizes the package-wire delay overhead on them. This eventually improves overall system performance.

# 2.2.5 Package Wireload Estimation

When RDL routing and signal assignment are complete, parasitic loads at chiplet IOs due to package wires can be estimated. Being aware of the output load, during the optimization steps, chiplet design tools can make necessary adjustments like buffer insertion, cell resizing on IO nets. At this point, the goal is to perform a rough estimation of package wire loads to complete the first iteration of chiplet implementation. More accurate parasitics can be extracted from the assembled design for the second iteration of chiplet implementation. The package wireload is calculated as a linear function of the wirelength. The function WireLoadEst() in Algorithm 2 describes the wireload estimation method. A wireload model is a list of values that represent the capacitance per unit length of package wires. These values are calculated from technology settings and package wire dimensions.

At the end of the co-design steps, as depicted in line 18 of Algorithm 1, the RDL planner tool generates a TCL script to implement the package routing and SDC files for all chiplets specifying wireload on IO pins. In the SDC file, the capacitance estimated by the WireLoadEst() function is specified as the wireload of the corresponding pin. With this strategy, the RDL planner can directly handle one-to-one pin connections between two chiplets. The point-to-point connection

is prioritize here since this is the most commonly used connection type on the package level. A multi-point connection can be handled by breaking it down into multiple point-to-point connections and then applying our strategy. Multiple chiplets can be handled by grouping the chiplets which are already interconnected into a single chiplet-like entity and perform routing between the group and another chiplet.

**Algorithm 2:** Signal Assignment & Wireload Estimate

```

1 Function AssignSignals (Tracks, Nets, Slack):

foreach track in Tracks do

track.length = calc_path_len(track.path)

sorted_tracks = sort_by_length(Tracks)

4

sorted_nets = sort_by_slack(Nets, Slack)

set next_track = 0

6

foreach net in sorted_nets do

sorted_tracks[next_track].signal = net

8

next_track += 1

9

return

10

11

12 Function WireLoadEst (Tracks, WireLoadModel):

foreach track in Tracks do

13

cap_per_len = WireLoadModel[track.layer]

14

track.load = track.length×cap_per_len

15

return

16

```

# 2.3 Physical Design

The physical design of both chiplets and the package can be implemented using any commercial chip design environment that supports hierarchical design flow. The Cadence Innovus is used to perform the hierarchical implementation of the package and chiplets in the experimental 2.5D system. The design environment is set up with the modified TSMC 65nm PDK and the entire system is loaded into the environment. Chiplets appear as modules in this design environment. Based on the plan generated by the RDL planner, the chiplets are placed on the package and their signal assignments are defined. Using the scripts generated by the RDL planner, the chiplet pins are routed on RDLs. Then the timing budget of chiplets and the package are extracted. After this

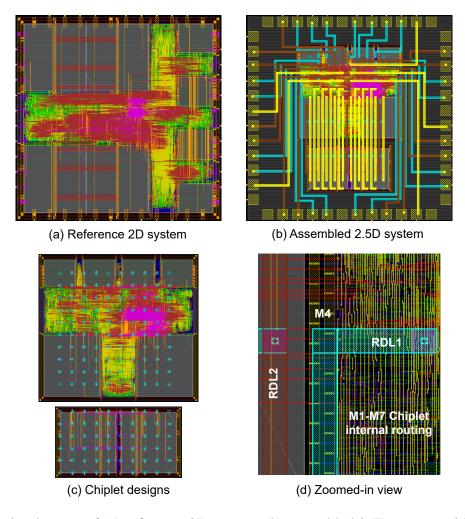

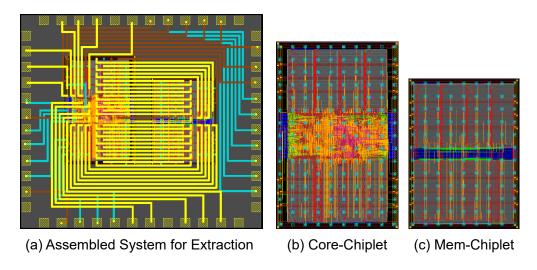

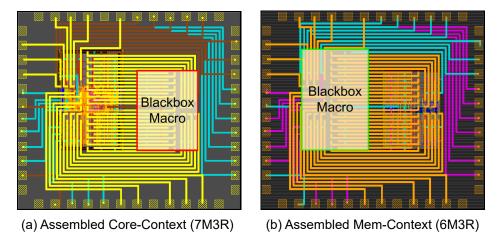

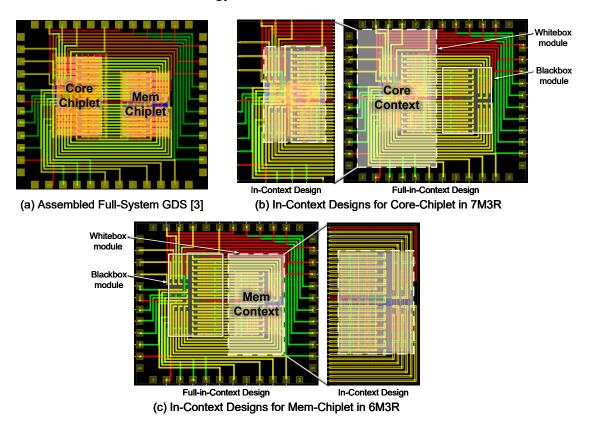

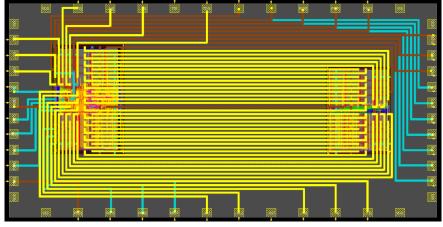

Figure 8: Design layouts of (a) reference 2D system, (b) assembled 2.5D system with chiplet and package layers, (c) designs of Core-Chiplet (top) and Mem-Chiplet (bottom), and (d) Zoomed-in view of the assembled design.

step, chiplets and the package are separated as hierarchical sub-designs, and can be implemented in parallel in their own design environments.

# 2.3.1 Hierarchical Implementation

During implementation, each chiplet is treated as a single 2D design with some extra constraints imposed by the top-level plan and designed using traditional chip design techniques. The initial SDC file, which defines the chiplet context (like IO delay, output load, etc.), is modified to include the wireload on chiplet pins estimated by the RDL planner tool. In the top-level planning stage, initial chiplet floorplans are prepared. This floorplan can be adjusted if necessary without

changing the pin configuration specified by the top-level plan. After fixing the floorplan, the Power Distribution Network is designed to ensure reliable power delivery to standard cells and memory macros. Standard tools are used for standard cell placement, clock network design, routing, and post-routing optimizations. Finally, filler cells and metal fills are used to fulfill the density requirement. Fig. 8(c) top sub-figure shows the Core-Chiplet, which contains all logic blocks and 8KB memory in the lower address range. Fig. 8(c) bottom sub-figure shows the Mem-Chiplet, which contains the other 8KB memory in the upper address range.

Package design can be implemented in parallel with chiplet designs. However, more accurate and reliable optimization of the package can be performed if interface timing models of chiplets extracted after their implementation are used. The RDL planner generates routing scripts for inter-chiplet routing at the end of the co-planning step. These scripts are utilized to finish inter-chiplet routing. Based on the package floorplan and inter-chiplet routing, package external IOs are placed. Chiplet pins that are not used in inter-chiplet connectivity are assigned as external connections to package IO pads. Fig. 8(b) shows the package design of the 2.5D system that integrates the chiplets shown in Fig. 8(c).

With routed chiplets and package layouts, they are imported into the integrated design environment again. To ensure manufacturability, DRC is performed on each of the chiplet and the package before design assembly. Fig. 8(d) shows a zoomed-in view of the assembled design, which shows traces from both chiplets and the package in the unified environment. Holistic extraction is performed on this assembled design using the extraction-rule file characterized for the chiplet-package unified technology. As all chiplets and the package are combined together in the same environment, all interactions between chiplets and the package are captured accurately in the extraction.

#### 2.3.2 Holistic Extraction

Holistic extraction can be performed using any commercial extraction tool that supports hierarchical extraction flow. The Synopsys StarRC LEF/DEF flow is used to perform the holistic

Table 2: Holistic capacitance (in fF) extraction results

| 1           |                    |       |       |       |       |       |  |

|-------------|--------------------|-------|-------|-------|-------|-------|--|

| Metal Layer | M1-M5              | M6    | M7    | RDL1  | RDL2  | RDL3  |  |

| M1-M5       | 16348              | 222.5 | 446.7 | 185.3 | 18.61 | 10.18 |  |

| M6          | 222.5              | 137.1 | 32.81 | 51.7  | 4.168 | 2.149 |  |

| M7          | 446.7              | 32.81 | 371.1 | 32.43 | 1.459 | 1.891 |  |

| RDL1        | 185.3              | 51.70 | 32.43 | 65.67 | 399.3 | 11.19 |  |

| RDL2        | 18.61              | 4.168 | 1.459 | 399.3 | 103.3 | 390.5 |  |

| RDL3        | 10.18              | 2.149 | 1.891 | 11.19 | 390.5 | 115.3 |  |

|             | Ground Capacitance |       |       |       |       |       |  |

| Metal Layer | M1-M5              | M6    | M7    | RDL1  | RDL2  | RDL3  |  |

| Capacitance | 31842              | 1526  | 477   | 853   | 251   | 420   |  |

extraction. Table 2 shows the coupling capacitance extraction result of the final design. For readability, capacitance numbers from M1 to M5 are merged. In the traditional die-by-die approach, it is not possible to accurately capture the interactions between chiplet and package routing layers. In the holistic method, these interactions are captured which are presented in the last three columns of the table, RDL1, RDL2, and RDL3. If we notice, there exists sufficient coupling between RDL1 of the package and M6-M7 of chiplets. Moreover, it is evident from the numbers that the coupling of RDL1 with M6 is greater than that with M7. As M7 is the topmost chiplet routing layer, it is expected that the coupling between RDL1 and M7 should be greater. However, as the routing on M6 is significantly greater than that on M7, and routing tracks of RDL1 and M6 run in the parallel direction, the effective overlap between RDL1 and M6 is much greater than that with M7. This detailed interaction can only be captured in a holistic extraction method. The extraction result can then be utilized to incrementally improve the system performance, signal integrity, and system reliability. In the next section, a set of design case studies is presented that reveals the impact of chiplet-package interactions and how the holistic extraction result can be utilized to iteratively improve the design.

Table 3 shows a comparative study between die-by-die and holistic extraction results. The die-by-die extraction result is calculated by performing extractions on individual chiplets and the package separately and then adding capacitance values of corresponding layers. As seen from Table 3, die-by-die extraction severely over-estimates the ground capacitance, especially on

Table 3: Comparison of Holistic vs. Die-by-Die ground (GCAP) and coupling (CCAP) capacitance extraction results (in fF)

| Metal Layer  | M1-M5  | M6     | M7     | R1     | R2     | R3     |

|--------------|--------|--------|--------|--------|--------|--------|

| DbD GCAP     | 31973  | 1568   | 485    | 1285   | 323    | 433    |

| Holi GCAP    | 31842  | 1526   | 477    | 853    | 251    | 420    |

| DbD GCAP Err | 0.41%  | 2.77%  | 1.60%  | 50.77% | 28.8%  | 3.19%  |

| DbD CCAP     | 23366  | 394    | 864    | 547    | 830    | 517    |

| Holi CCAP    | 23732  | 450    | 886    | 746    | 917    | 531    |

| DbD CCAP Err | -1.54% | -12.5% | -2.57% | -26.5% | -9.55% | -2.75% |

package layers. This over-estimation is due to the absence of chiplet routing layers between the package layers and the reference ground plane. More alarming errors are observed in coupling-capacitance. Die-by-die extraction severely underestimates the coupling capacitance on all layers as it cannot capture the interactions between chiplets and the package layers. This large error in parasitic extraction can cause severe signal integrity issues leading to system failure. Therefore, holistic consideration of chiplet and package interactions is a must in high-density 2.5D packaging technologies.

One limitation of holistic extraction is that the existing commercial extraction tools cannot perform holistic extraction when heterogeneous technologies are involved. However, this limitation is not inherent to the holistic flow. This limitation can be overcome by extending the extraction tools to handle multiple heterogeneous technologies. An intermediate solution is to perform in-context parasitic extraction per technology and stitch them together carefully to create the holistic extraction result.

# 2.3.3 Iterative Optimizations

After design assembly and analyses, if the target performance is not achieved and discrepancies between estimated package parasitics with extraction results are observed, iterative implementation of chiplets can be conducted. If active packaging material is used, a similar optimization procedure can be performed on the package layer as well. In the first iteration of the chiplet design, the package wireload is a rough estimation based on package wirelength. Thus almost always some room for improvement can be expected. After design assembly and holistic

extraction, STA analysis is performed on the design with the holistic extraction result. Based on this analysis, new timing contexts are created for all the chiplets. In the STA analysis, timing paths through the package are modeled, including the cells within the driver and receiver chiplets. This makes the cross-boundary co-optimization between chiplets possible. One limitation of existing STA tools is that they only consider resistive and capacitive parasitic elements of the nets. However, package wires exhibit significant inductive behavior. Though in this paper, we only consider the capacitive impact of the package wires, this same methodology can be applied to consider other elements of the package wire, which affect the overall system performance.

As accurate parasitic information is available through holistic extraction, it is possible to generate a tighter timing budget for the next iteration. The Synopsys PrimeTime is used to create the updated timing contexts utilizing its context characterization feature. The updated timing context is exported as an SDC file for each chiplet. This SDC file contains all the details of the timing contexts of each IO pin of a chiplet. For output pins, it specifies maximum transition time, wireload, pin-load, and output delay. For input pins, it specifies minimum/maximum allowed capacitance, maximum fanout, driving cell, and input delay. For all the delay information, clock latency is also specified. Using these updated timing contexts, all chiplets are reimplemented and adjusted for the package overhead. These timing contexts can be used to perform iterative optimization of the package design as well. There can be several iterations of assembly, extraction, timing context creation, and reimplementation until it is no longer possible to improve the system performance or the target performance is met. However, with a good estimation in the first iteration, a second iteration is generally good enough to meet the best system performance.

### 2.4 Two-way Partition Design Study

Several design cases are prepared to study the impact of chiplet-package interactions on the system. It is found that holistic extraction results can be utilized to significantly improve system performance. In this section, some of these designs and analysis results are presented. Since this is the first time a holistic chiplet-package design methodology is performed, not every detailed

analysis step is performed, such as power integrity and signal integrity, thermal analyses, etc. However, since the holistic design flow is compatible with all modern chip and package design CAD tools, it is likely that those analyses can be easily added with a few minor modifications.

#### 2.4.1 Design Case Variants

Case-1: Reference 2D Design: A 2D design of the microcontroller system is implemented as a reference design using TSMC 65nm technology with lower seven metal layers. The gate-level netlist obtained after synthesis and before preparing chiplet partitions is used in this design. After trying out several floorplans, a square floorplan was selected with a side length of 600µm, as shown in Fig. 8(a). PDN, cell placement, clock network design, routing, and post-routing optimizations are performed using standard chip design tools. The finished design achieves 400 MHz maximum system frequency. Table 4 Case-1 column shows the parameters of the finished design.

Case-2: Context-Free 2.5D Design: This case is a context-free single-pass design that resembles the traditional die-by-die approach. Chiplets and the package are designed independently without using the context creation step as in the holistic flow. Though the RDL planner generates the top-level plan, it does not perform package wireload estimation. However, design assembly and holistic extraction is performed to capture chiplet-package interactions. This design case reveals the impact of the package on chiplets and the consequent degradation of the overall system performance. Table 4 Case-2 column shows the parameters of this design case.

Case-3: Context-Aware Optimized 2.5D Designs: This case is designed in the holistic flow and optimized using iterative context creation and reimplementation of chiplets, as discussed in Section 2.3.3. Chiplet-package interactions are included as much as possible in the design and optimization steps. As discussed previously, the RDL planner prepares the top-level plan and calculates package wireload estimation, which is used in the first iteration of chiplets implementation. After design assembly and holistic extraction, extracted parasitics are used to

perform STA and create chiplet timing contexts for the next iteration of chiplets implementation. The last two columns of Table 4 show the parameters of two different iterations of this design.

### 2.4.2 Holistic Analysis and Optimization