## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

12-2022

# Reliability Enhancing Control Algorithms for Two-Stage Grid-Tied Inverters

Yuheng Wu University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electromagnetics and Photonics Commons, and the Electronic Devices and Semiconductor Manufacturing Commons

#### Citation

Wu, Y. (2022). Reliability Enhancing Control Algorithms for Two-Stage Grid-Tied Inverters. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/4776

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

## Reliability Enhancing Control Algorithms for Two-Stage Grid-Tied Inverters

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Yuheng Wu

Nanjing University of Aeronautics and Astronautics

Bachelor of Science in Detection, Guidance, and Control Technology, 2015

Nanjing University of Aeronautics and Astronautics

Master of Science in Control Theory and Control Engineering, 2018

## December 2022 University of Arkansas

| This dissertation is approved for recommendation to the Graduate Council. |                                               |  |

|---------------------------------------------------------------------------|-----------------------------------------------|--|

| Yue Zhao, Ph.D. Dissertation Director                                     | H. Alan Mantooth, Ph.D. Dissertation Director |  |

| Juan C. Balda, Ph.D.<br>Committee Member                                  | David Huitink, Ph.D. Committee Member         |  |

#### **ABSTRACT**

In the photovoltaic (PV) generation system, two types of grid-tied inverter systems are usually deployed: the single-stage grid-tied inverter system and the two-stage grid-tied inverter system. In the single-stage grid-tied inverter system, the input of the inverter is directly connected to the PV arrays, while an additional dc-dc stage is inserted between the PV arrays and the dc-ac inverter in the two-stage design. The additional dc-dc stage could provide a stable dc-link voltage to the inverter, which also enables new design possibilities, including the multi-MPPT operation and solar-plus-storage application. Thus, the two-stage grid-tied inverter has been widely used in the PV generation system.

As the core component of the PV generation system, the reliability of the grid-tied inverter determines the overall robustness of the system. The two-stage grid-tied inverter system includes three parts: the dc-dc stage, dc-link capacitor, and dc-ac inverter. Thus, the reliability of the two-stage grid-tied inverter relies on the reliability of each part. The dc-dc stage is used to provide a stable dc-link voltage to the inverter. However, when the inverter stage provides constant power to the grid, the load of the dc-dc stage becomes the constant power load (CPL), which will deteriorate the stability of the dc-dc stage. The dc-link capacitor is used to attenuate the voltage ripple on the dc-link and balance the transient power mismatch between the dc-dc stage and the dc-ac stage. However, during the operation of the inverter system, the degradation of the capacitor will reduce the converter reliability, and even result in system failure. The inverter stage is connected to the grid through the output filter, and the LCL type filter has been commonly used due to its superior performance. The resonance of the LCL filter must be properly damped to enhance the inverter stability. However, the grid-side impedance will lead to the resonant frequency drifting of the LCL filter, which will worsen the stability margin of the inverter. Thus,

the control design of the two-stage grid-tied inverter system must consider those reliability challenges.

In this work, three control algorithms are proposed to solve the reliability challenges. For the dc-dc stage, an uncertainty and disturbance estimator (UDE) based robust voltage control scheme is proposed. The proposed voltage control scheme can actively estimate and compensate for the disturbance of the dc-dc stage. Both the disturbance rejection performance and the stability margin of the dc-dc stage, especially under the CPL, could be enhanced. For the dc-link capacitor, a high-frequency (HF) signal injection based capacitance estimation scheme is proposed. The proposed estimation scheme can monitor the actual dc-link capacitance in real-time. For the inverter stage, an adaptive extremum seeking control (AESC) based LCL filter resonant frequency estimation scheme is proposed. The AESC-based estimation scheme can estimate the resonant frequency of the LCL filter online. All the proposed reliability enhancing control algorithms could enhance the reliability of the two-stage grid-tied inverter system. Detailed theoretical analysis, simulation studies, and comprehensive experimental studies have been performed to validate the effectiveness.

© 2022 Yuheng Wu All Rights Reserved

#### **ACKNOWLEDGEMENT**

At the last stage of my Ph.D. journey, I would like to express my appreciation to my advisors, Dr. H. Alan Mantooth and Dr. Yue Zhao, for their enormous support and encouragement, which inspired my study, research, and life. They have spent endless hours reviewing my papers and providing suggestions for the projects. They will be the inspiring role model for my future career growth.

I am also grateful to my dissertation advisory committee members: Dr. Juan C. Balda and Dr. David Huitink for their generous support and insightful suggestions. I would like to acknowledge my friends Dr. Mohammad Hazzaz Mahmud and Dr. Waleed Saad S. Alhosaini, who have closely worked with me since the start of my Ph.D. journey and helped me fit in at a new country. I would like to thank my other teammates and friends: Zhe Zhao, Eric Allee, Dr. Shuang Zhao, Fei Diao, Xinyuan Du, Shamar Christian, Dr. Roberto Fantino, David Arturo Porras Fernandez, Roderick Gomez Jimenez, Muhammad Jahidul Hoque, Tyler Adamson, and Bakhtiyar Mohammad Nafis. I would also like to thank Dr. Chris Farnell and Justin E. Jackson for their support in the testing.

Besides, I would like to my friends and colleagues at John Deere Intelligent Solutions Group: Dr. Long Wu and Mr. Tianjun Fu. I am also grateful to Dr. Danielle Chu with MathWorks. They have helped me to enhance my understanding of engineering research during the collaboration on a lot of interesting projects.

Finally, I'm extremely grateful to the University of Arkansas for the support during my Ph.D. study. The four peaceful and wonderful years at Fayetteville, AR are the most unforgettable experience of my life.

Financial support from the following institutions/organizations is gratefully acknowledged:

- U.S. National Science Foundation (NSF)

- U.S. Department of Energy's Solar Energy Technologies Office (SETO)

- U.S. Department of Energy's Oak Ridge National Laboratory (ORNL)

- U.S. Department of Energy's Advanced Research Projects Agency–Energy (ARPA-E)

- NSF Center on Grid-connected Advanced Power Electronics Systems (GRAPES)

- University of Arkansas, USA

# **DEDICATION**

This dissertation is dedicated to

my mother Dehui Yu, my father Gang Wu, and my sister Xiaojian Wu.

# LIST OF CONTENTS

| CHAPTER 1 Introduction                                                  | 1           |

|-------------------------------------------------------------------------|-------------|

| 1.1 Background                                                          | 1           |

| 1.2 The state-of-the-art of two-stage grid-tied inverters               | 4           |

| 1.3 Challenges and problem definitions                                  | 5           |

| 1.4 Outline                                                             | 10          |

| 1.5 Reference                                                           | 12          |

| CHAPTER 2 UDE-Based Robust Voltage Control for DAB Converters           | 14          |

| 2.1 Introduction                                                        | 14          |

| 2.2 A Brief Review of DAB Converters and UDE Scheme                     | 17          |

| 2.2.1 Review of the DAB Converter                                       | 17          |

| 2.2.2 Review of UDE                                                     | 18          |

| 2.3 UDE Based Robust Voltage Control for the DAB Converter              | 20          |

| 2.3.1 UDE Based Robust Voltage Control                                  | 20          |

| 2.3.2 Stability Analysis                                                | 24          |

| 2.3.3 Stability Under the CPL                                           | 28          |

| 2.3.4 Controller Design                                                 | 30          |

| 2.4 Experimental Studies                                                | 35          |

| 2.5 Conclusion                                                          | 45          |

| 2.6 References                                                          | 46          |

| CHAPTER 3 High-Frequency Signal Injection Based Output Capacitance Esti | imation for |

| Dual-Active-Bridge Converters                                           | 48          |

| 3.1 Introduction                                                        | 48          |

| 3.2 Modeling of the DAB Converter and DC-Link Capacitor                 | 50          |

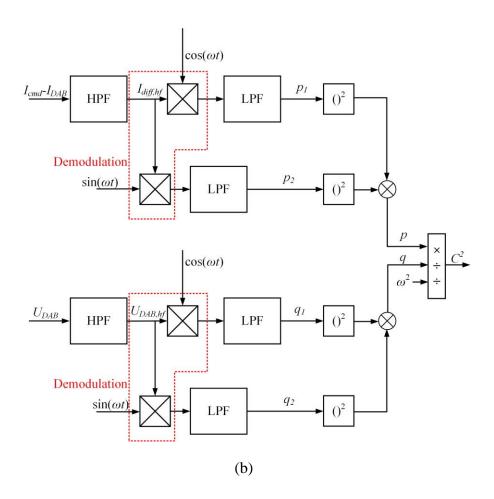

| 3.3 High-Frequency Signal Injection Based Capacitance Estimation Scheme | 53          |

| 3.3.1 Estimation Scheme                                                 | 53          |

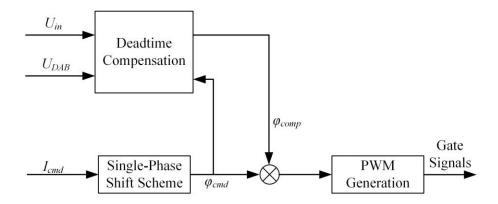

| 3.3.2 Deadtime Effect                                                   | 58          |

| 3.4 HIL and Experimental Studies                                        | 65          |

| 3.5 Conclusions                                                         | 68          |

| 3.6 References                                                          | 70          |

| CHAPTER 4 AESC-Based Resonant Frequency Estimation of LCL Filters | <b>72</b> |

|-------------------------------------------------------------------|-----------|

| 4.1 Introduction                                                  | 72        |

| 4.2 Review of LCL Type Grid-Tied Inverter and ESC Scheme          | 74        |

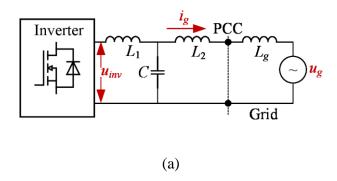

| 4.2.1 Review of LCL Type Grid-Tied Inverter                       | 74        |

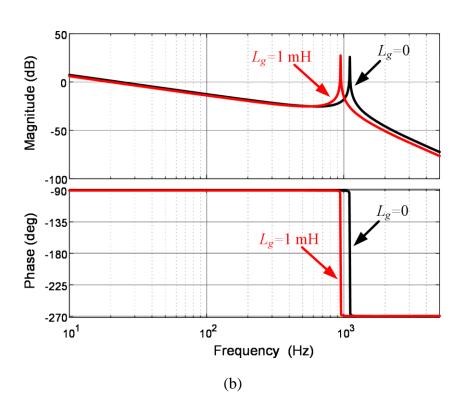

| 4.2.2 Review of ESC Scheme                                        | 76        |

| 4.3 ESC Based Resonant Frequency Estimation                       | 76        |

| 4.3.1 Design of ESC Based Resonant Frequency Estimation Scheme    | 76        |

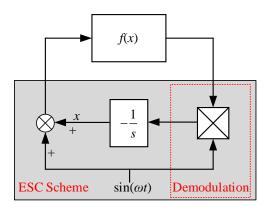

| 4.4 AESC Based LCL Filter Resonant Frequency Estimation           | 84        |

| 4.4.1 AESC based Estimation Scheme                                | 84        |

| 4.4.2 AESC Design and Stability Analysis                          | 90        |

| 4.4.3 Accuracy and implementation discussions                     | 93        |

| 4.5 Experimental Studies                                          | 02        |

| 4.6 Conclusions 10                                                | 80        |

| 4.7 References1                                                   | 10        |

| CHAPTER 5 Conclusions and Future Research Work                    | 12        |

| 5.1 Conclusions of This Dissertation                              | 12        |

| 5.2 Future Works                                                  | 13        |

# LIST OF TABLES

| TABLE 1-1 U.S. DOE SETO 2025 Goals of Low-Cost Electricity [1]. | 1   |

|-----------------------------------------------------------------|-----|

| TABLE 2-1 DAB Converter Parameters                              | 35  |

| TABLE 3-1 HIL Simulation Parameters                             | 65  |

| TABLE 3-2 Experiment Parameters                                 | 66  |

| TABLE 4-1. Summary of the Proposed Scheme                       | 101 |

# LIST OF FIGURES

| Figure 1-1. Different types of grid-tied inverter systems: (a) single-stage and (b) two-stage 3                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2. Schematic of the proposed two-stage grid-tied inverter system                                                                                                                              |

| Figure 1-3. Unstable dc-dc converter due to the CPL                                                                                                                                                    |

| Figure 1-4. DC-link capacitance degradation.                                                                                                                                                           |

| Figure 1-5. Unstable dc-ac stage due to the LCL filter resonant frequency drifting                                                                                                                     |

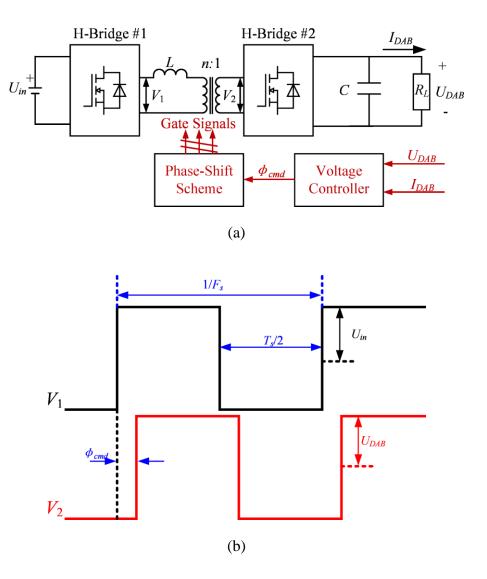

| Figure 2-1. (a) Schematic of the DAB converter and (b) single-phase-shift modulation scheme.17                                                                                                         |

| Figure 2-2. Output current model of the DAB converter                                                                                                                                                  |

| Figure 2-3. UDE controlled DAB converter. 22                                                                                                                                                           |

| Figure 2-4. (a) Negative incremental impedance of a CPL and (b) impedance model of the UDE                                                                                                             |

| controlled DAB converter                                                                                                                                                                               |

| Figure 2-5. (a) Nyquist plot of $\frac{1}{zG_s(z)+\alpha+k}$ , (b) and (c) frequency responses of                                                                                                      |

| $\left  \frac{G_f(z)G_s(z) + \alpha + k}{zG_s(z) + \alpha + k} \Delta_{Total}(z) \right  : \text{(b) under different parameter uncertainties and (c) under different parameter uncertainties} \right $ |

| closed-loop bandwidths and error convergence rates                                                                                                                                                     |

| Figure 2-6. Output impedance of the UDE controlled DAB converter. Bandwidth of (a) $G_f(z) =$                                                                                                          |

| 400 Hz and (b) $G_f(z) = 0$ . 34                                                                                                                                                                       |

| Figure 2-7. Experimental Setup                                                                                                                                                                         |

| Figure 2-8. Transient responses of the DAB converter under load step change with different                                                                                                             |

| controllers: (a) UDE controller with 400 Hz bandwidth $G_f(z)$ (b) UDE controller with $G_f(z)$ =0, and                                                                                                |

| (c) PI controller                                                                                                                                                                                      |

| Figure 2-9. Transient responses of the DAB converter when feeding a 120 W CPL with different         |

|------------------------------------------------------------------------------------------------------|

| controllers and accurate parameters: (a) UDE controller with 400 Hz bandwidth $G_f(z)$ (b) UDE       |

| controller with $G_f(z)=0$ , and (c) PI controller. 40                                               |

| Figure 2-10. Transient responses of the DAB converter when feeding a 120 W CPL with different        |

| controllers and 30% error in $L$ and $C$ : (a) UDE controller with 400 Hz bandwidth $G_f(z)$ (b) UDE |

| controller with $G_f(z)=0$ , and (c) PI controller. 43                                               |

| Figure 2-11. Transient responses of the DAB converter when feeding a 120 W CPL with a doubled        |

| deadtime: (a) the proposed UDE controller and (b) PI controller                                      |

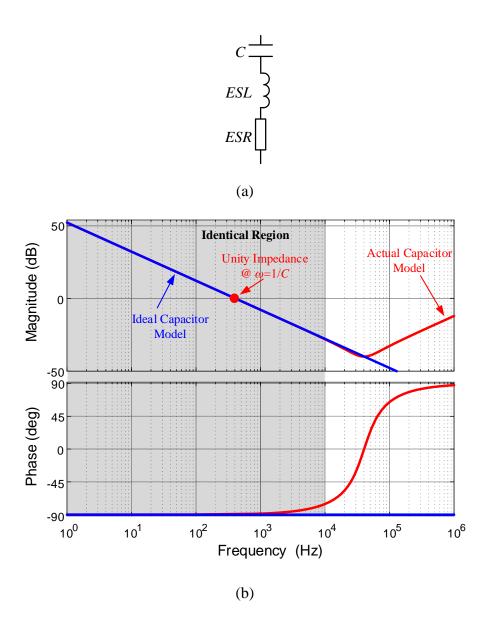

| Figure 3-1. (a) Single-phase DAB converter, (b) SPS modulation scheme, and (c) equivalent model      |

| of the DAB converter                                                                                 |

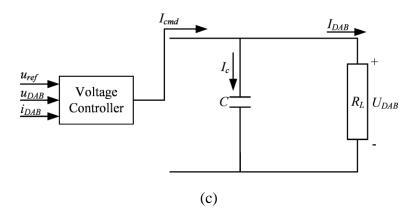

| Figure 3-2. (a) Actual capacitor model and (b) frequency response of the actual capacitor and ideal  |

| capacitor53                                                                                          |

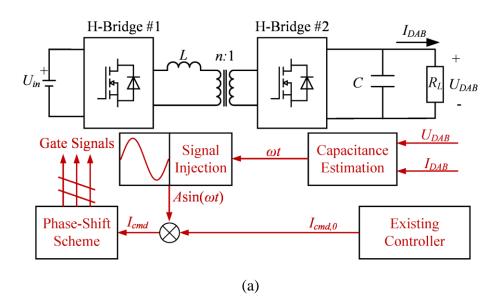

| Figure 3-3. (a) system diagram of the proposed scheme, and (b) detailed diagram of the proposed      |

| scheme                                                                                               |

| Figure 3-4. (a) Schematic of a half-bridge and (b) ideal gate signals, output voltage, and output    |

| current of the half-bridge                                                                           |

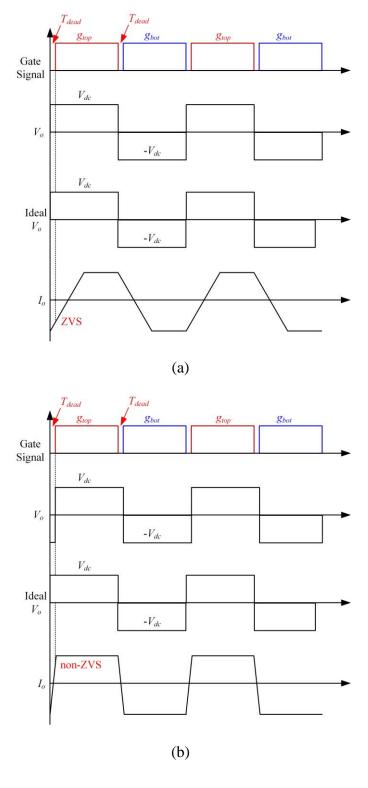

| Figure 3-5. Gate signals, output voltage, and output current of the half-bridge under (a) ZVS        |

| condition and (b) non-ZVS condition. 61                                                              |

| Figure 3-6. Proposed deadtime compensation scheme. 64                                                |

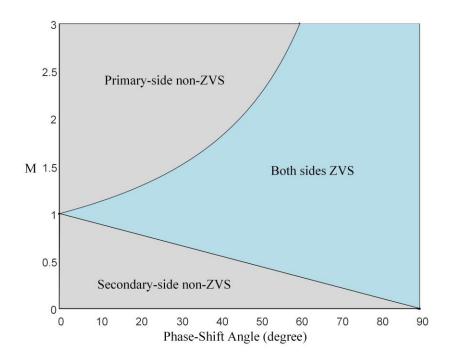

| Figure 3-7. ZVS region of the DAB converter. 64                                                      |

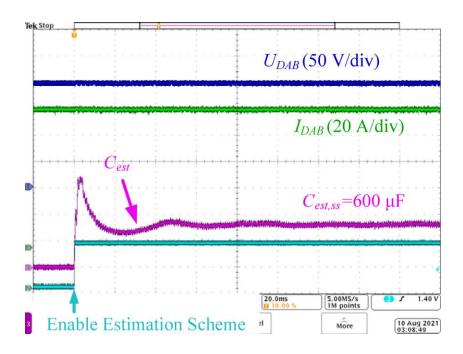

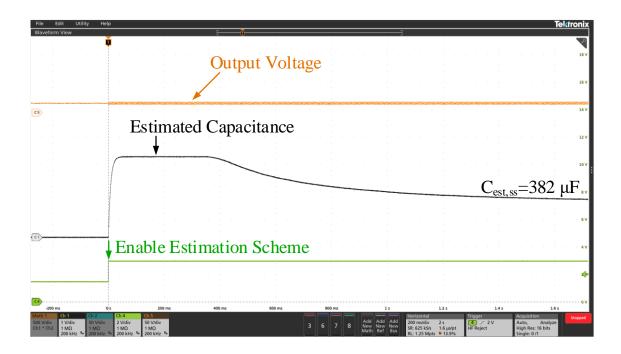

| Figure 3-8. HIL simulation result. 66                                                                |

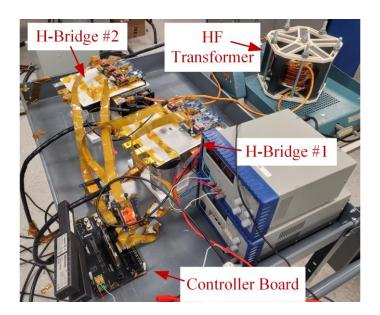

| Figure 3-9. Experimental setup. 67                                                                   |

| Figure 3-10. Experimental result                                                                     |

| Figure 4-1. (a) Grid-tied inverter with an LCL filter and (b) typical frequency response of the LCL |

|-----------------------------------------------------------------------------------------------------|

| filter                                                                                              |

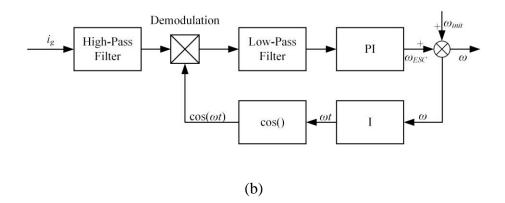

| Figure 4-2. Typical control diagram of the ESC scheme                                               |

| Figure 4-3. ESC based resonant frequency estimation scheme: (a) inverter system diagram and (b)     |

| ESC scheme. 78                                                                                      |

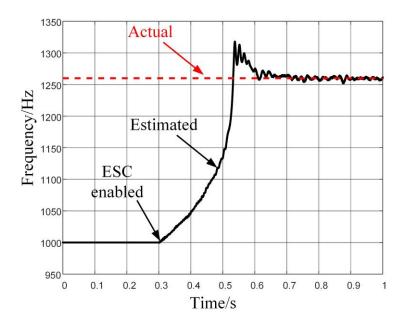

| Figure 4-4. Simulation of the proposed ESC based estimation scheme                                  |

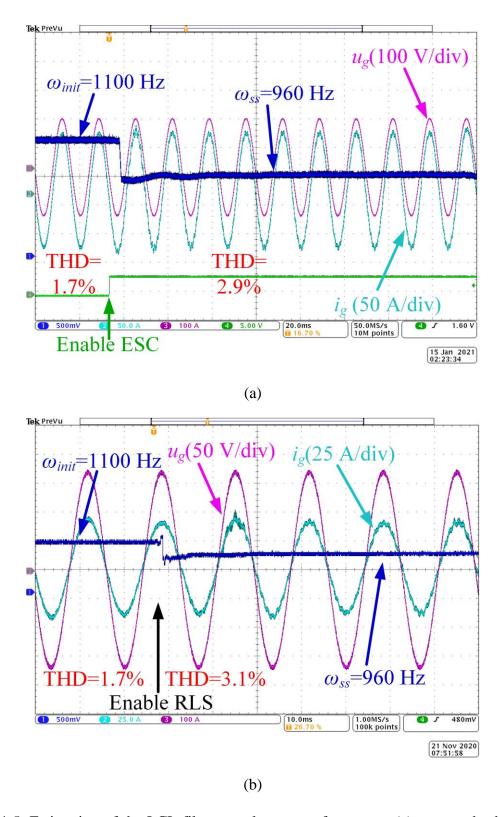

| Figure 4-5. Estimation of the LCL filter actual resonant frequency: (a) proposed scheme and (b)     |

| RLS scheme. 83                                                                                      |

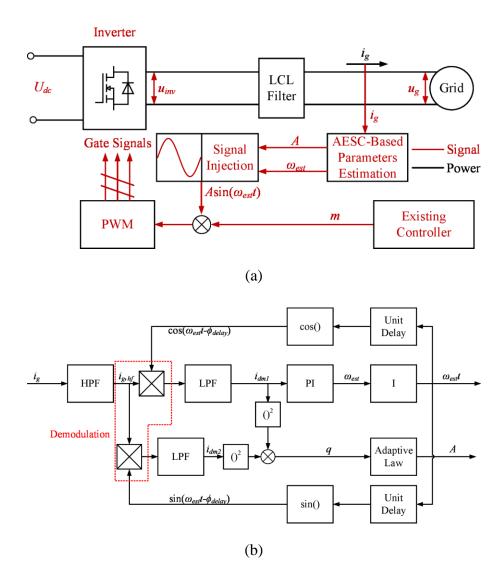

| Figure 4-6. AESC based resonant frequency estimation scheme: (a) inverter-level system diagram      |

| and (b) detailed diagram of AESC                                                                    |

| Figure 4-7. Adaptive amplitude of the injection signal.                                             |

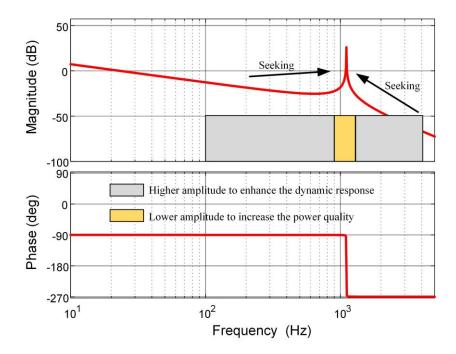

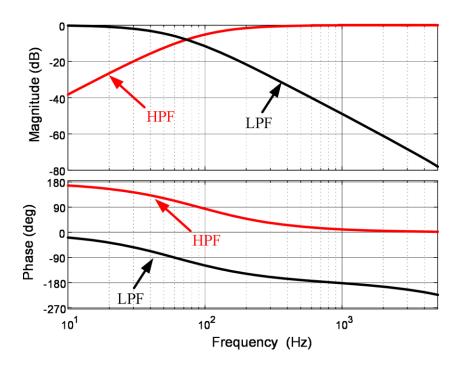

| Figure 4-8. Frequency responses of the designed HPF and LPF                                         |

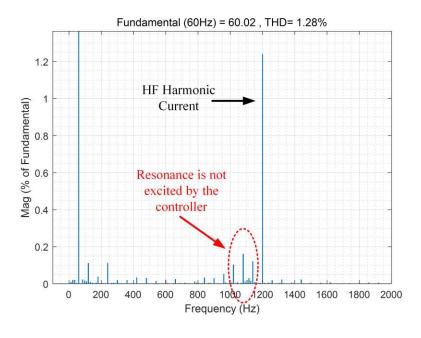

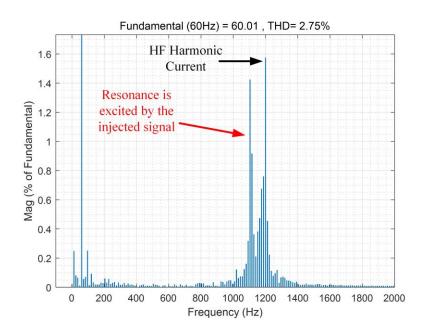

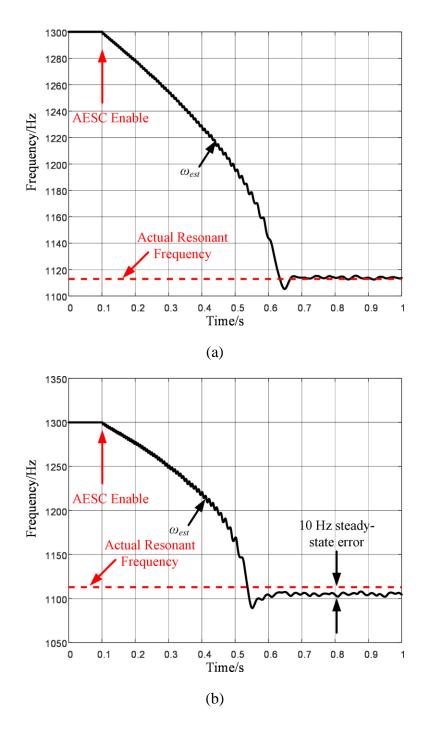

| Figure 4-9. Simulated results when the harmonic frequencies overlap the resonant frequency: (a)     |

| frequency spectrum of the grid-side current before the AESC scheme is enabled, (b) frequency        |

| spectrum of the grid-side current after the AESC scheme is enabled, and (c) estimated resonant      |

| frequency                                                                                           |

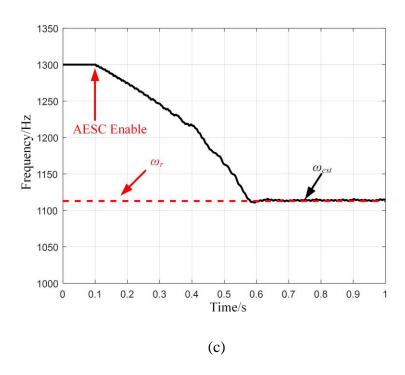

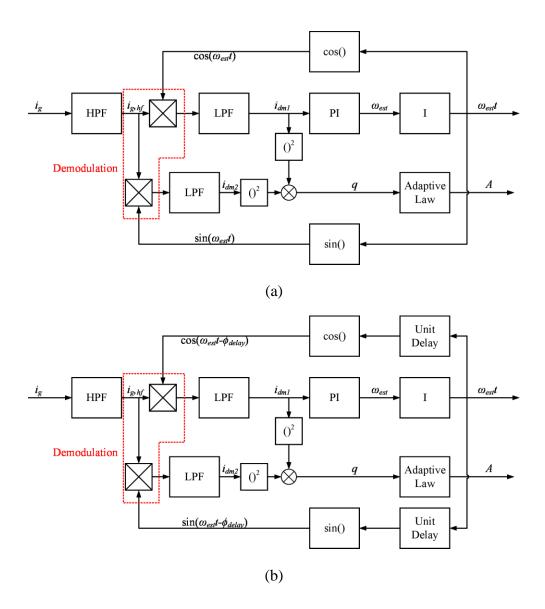

| Figure 4-10. Diagram of AESC (a) without delay compensation and (b) with explicit delay             |

| compensation. 98                                                                                    |

| Figure 4-11. Simulation results of AESC scheme: (a) with delay compensation and (b) without         |

| delay compensation                                                                                  |

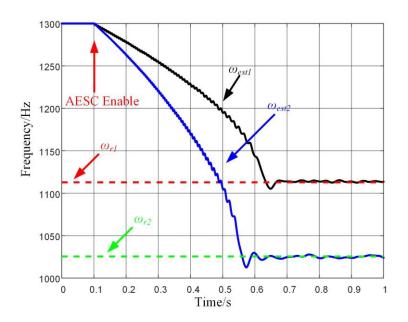

| Figure 4-12. Estimated resonant frequency when two grid-tied inverters are paralleled 100           |

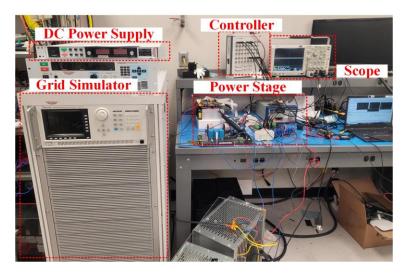

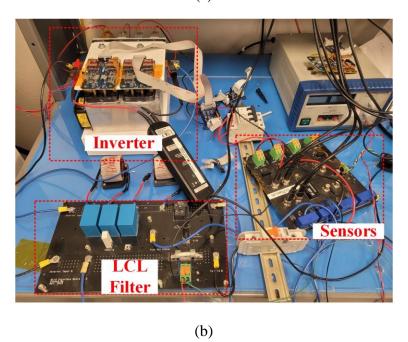

| Figure 4-13. (a) Experiment setup and (b) details of the grid-tied inverter under test              |

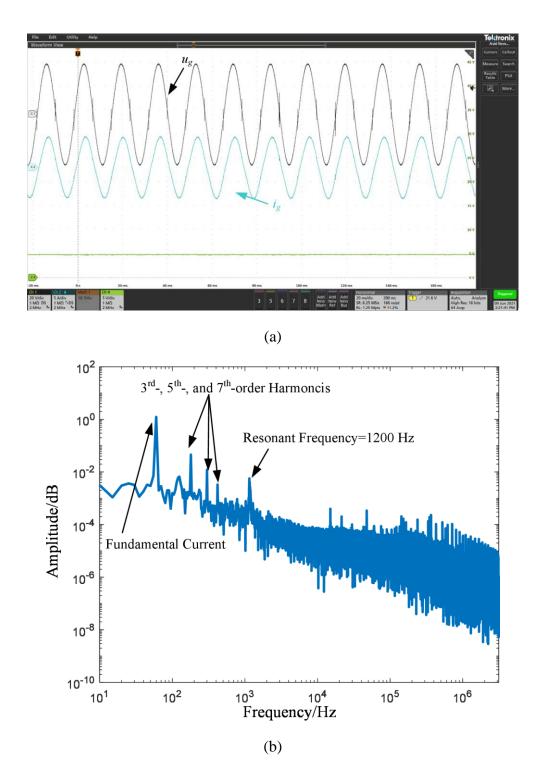

| Figure 4-14. Characterization of the LCL filter (a) output of the grid-tied inverter and (b)                | FFT       |

|-------------------------------------------------------------------------------------------------------------|-----------|

| results of the grid-side current.                                                                           | . 104     |

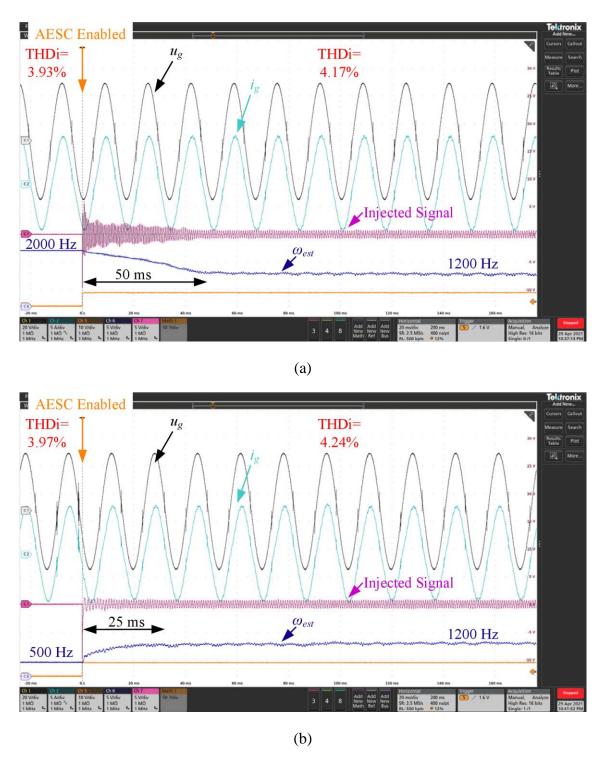

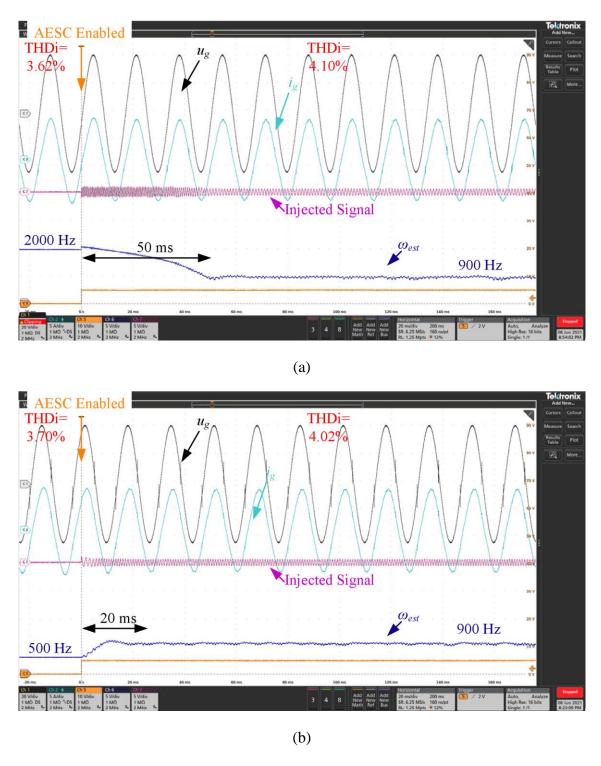

| Figure 4-15. Performance of proposed scheme with differential initial conditions: (a) $\omega_r < \omega_r$ | est, init |

| and (b) $\omega > \omega_{est,init}$ .                                                                      | . 106     |

| Figure 4-16. Performance of proposed scheme under weak grid with differential initial condit                | ions:     |

| (a) $\omega_r < \omega_{est,init}$ and (b) $\omega_{>}\omega_{est,init}$                                    | . 107     |

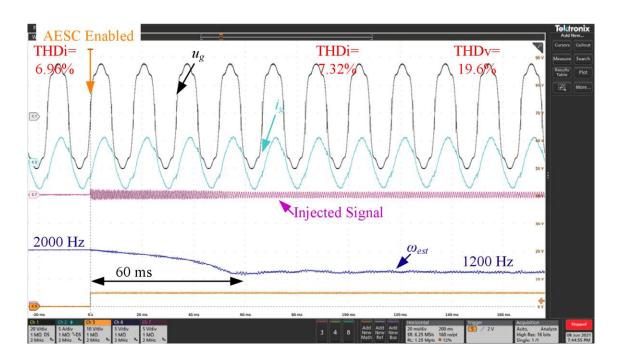

| Figure 4-17. Performance of proposed scheme under highly distorted grid                                     | . 108     |

#### LIST OF PUBLICATIONS

- [1] Y. Wu, M. H. Mahmud, Y. Zhao and H. A. Mantooth, "Uncertainty and Disturbance Estimator-Based Robust Tracking Control for Dual-Active- Bridge Converters," in IEEE Transactions on Transportation Electrification, vol. 6, no. 4, pp. 1791-1800, Dec. 2020. [Published, Chapter 2 consists of this paper].

- [2] Y. Wu, M. H. Mahmud, R. S. Krishna Moorthy, M. Chinthavali and Y. Zhao, "Adaptive Extremum Seeking Control Based LCL Filter Resonant Frequency Online Estimation," in IEEE Transactions on Power Electronics, vol. 37, no. 1, pp. 59-64, Jan. 2022. [Published, Chapter 4 consists of this paper].

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Background

The recent development in power electronic semiconductors enables the wide deployment of solar energy conversion systems. On one hand, the development of photovoltaic (PV) cells has notably reduced the cost of solar energy. In 2020, the cost of PV panels has reduced by about 85% compared with that in 2010, from \$2.51/W to \$0.38/W [1]. The cost reduction of PV panels has transferred solar energy from an expensive generation system to affordable clean energy. Table 1-1 summarizes some low-cost electricity goals of the U.S. Department of Energy (DOE) Solar Energy Technologies Office (SETO) for 2025 with a notable reduction in the levelized cost of energy (LCOE) of solar energy is expected. On the other hand, as the key component in the solar energy system that achieves the power conversion from PV modules to the grid, the design of the grid-tied inverter also benefits from the advancement of the wide bandgap (WBG) semiconductors, including silicon carbide (SiC) and gallium nitride (GaN) devices. The low switching loss of WBG devices allows for higher switching frequency, and thus, the power density of the converter can be improved. Meanwhile, compared to their silicon counterparts, the WBG devices can operate at higher temperature, which enhances the overall reliability of the inverter system [2].

TABLE 1-1 U.S. DOE SETO 2025 Goals of Low-Cost Electricity [1]

| Systems                 | LCOE Goal  |

|-------------------------|------------|

| Utility-scale PV system | \$0.03/kWh |

| Commercial PV system    | \$0.08/kWh |

| Residential PV system   | \$0.10/kWh |

| Utility-scale PV plus energy storage system | \$1.36/W <sub>DC</sub> |

|---------------------------------------------|------------------------|

|                                             |                        |

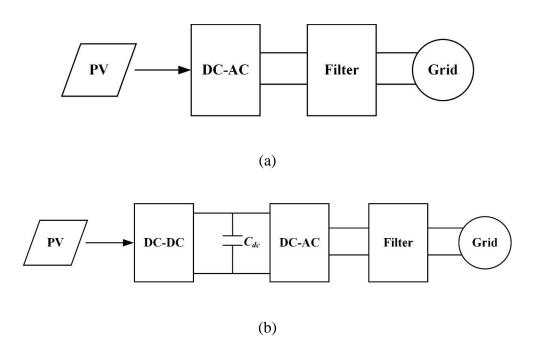

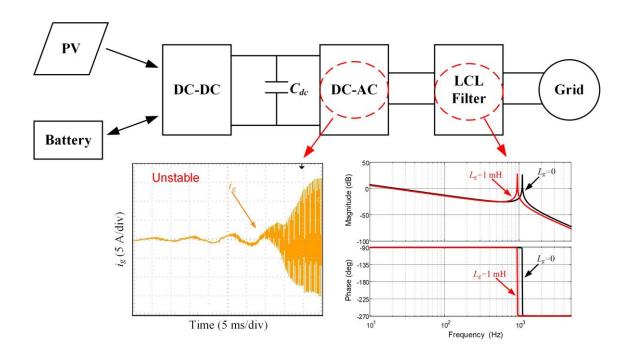

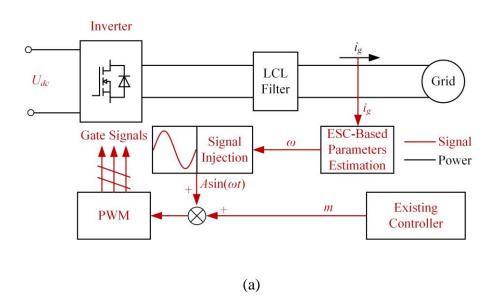

In grid-tied solar energy systems, single- and two-stage grid-tied inverters are the commonly used. Figure 1-1 (a) and (b) are the system-level architecture of the single-stage and two-stage grid-tied inverter systems, respectively. In the single-stage grid-tied inverter system, the PV modules are directly connected to the grid-tied inverter to achieve the dc-ac power conversion, where an output filter is inserted between the dc-ac stage and the grid to attenuate the switching ripples and harmonics. The two-stage grid-tied inverter system, however, contains an additional dc-dc stage. The dc-dc stage in the two-stage grid-tied inverter system provides a stiff dc-link voltage to the dc-ac stage, while the dc-link capacitor  $C_{dc}$  is used as the energy buffer to attenuate the voltage ripples and balance the transient power unbalance between the two stages. In order to maximize the output power of the PV module, both topologies are able to work in the maximum power point tracking (MPPT) mode [3]-[6]. Compared with the two-stage design, the single-stage grid-tied inverter system is simpler in the hardware design due to the elimination of the additional dc-dc stage. However, considering the intermittent nature of the solar energy and the MPPT operation, the input voltage of the single-stage grid-tied inverter system is not stable, and the control algorithm must be able to compensate for the uncertainties. Although the hardware cost of the two-stage design is higher, the input voltage of the dc-ac stage is stable due to the additional dc-dc stage. Thus, the control complexity of the dc-ac stage is much simpler in the two-stage design than that in the single-stage grid-tied inverter system. Besides, the single-stage grid-tied inverter cannot ensure the MPPT operation for each PV module if multiple PV modules are connected in series [3]. Those disadvantages of the single-stage grid-tied inverter could limit its application in the solar energy system. Nevertheless, the two-stage design can provide more degree-of-freedom in the MPPT operation. By adopting a proper dc-dc topology, the two-stage grid-tied inverter system can support multi-MPPT operation, i.e., more energy can be harvested from PV modules. Moreover, the two-stage design also enables the solar-plus-storage applications [1], [2]. By adopting a bi-directional dc-dc converter in the two-stage grid-tied inverter system, a battery energy storage system (BESS) could be integrated with the PV modules and improve the system robustness and reliability. In 2019, about 2% of all PV utility-scale PV systems were integrated with BESS, and more than 30% of new utility-scale PV systems that are proposed in 2022 and 2023 will be paired with energy storage [1]. Thus, the two-stage grid-tied inverter system has been widely adopted in the PV system due to its advantages.

Figure 1-1. Different types of grid-tied inverter systems: (a) single-stage and (b) two-stage.

## 1.2 The state-of-the-art of two-stage grid-tied inverters

Besides the fact that the two-stage grid-tied inverter has been widely adopted in the PV generation system, there are also a large amount of research effort on the two-stage grid-tied inverter from both academia and industry to further enhance the performance of inverter systems.

Since the additional dc-dc stage in the two-stage grid-tied inverter system can provide a stable dc-link voltage to the dc-ac stage, the selection of the dc-link voltage enhances the degree-offreedom of the controller design. In [7]-[9], the adaptive dc-link voltage strategy has been discussed. The dc-link voltage, i.e., the output voltage of the dc-dc stage, can be actively adjusted based on the required inverter output voltage, and thus, the switching loss in all power switches can be notably reduced. Feedforward control has been integrated with the adaptive dc-link voltage controller to enhance the dynamic response of the grid-tied inverter system. It should be noticed that although the additional dc-dc stage with a properly designed voltage controller can provide a stable dc-link voltage to the inverter, the high-frequency voltage ripples caused by the dc-ac stage still exist. Especially, when the grid-tied inverter is connected to the single-phase grid, voltage ripple on the dc-link with the double-line frequency will result in a series of odd order harmonics on the inverter output current, and thus, the output power quality will be distorted. In [10], a closedform solution is proposed to calculate the amplitude of the ripple-caused harmonics. With the closed-form harmonics analysis, the selection of the dc-link capacitance can be guided by the required output power quality. Moreover, the impact of the dc-link capacitance on the dc-link voltage control stability has been analyzed in [11], where a small-signal model of the dc-link voltage control loop has been proposed, and a right-half-plane (RHP) has been observed if the inverter is operating at voltages lower than the maximum power point. With the proposed smallsignal model, a minimum requirement of the dc-link capacitance can be provided to ensure the

stability of the PV generation system. In [4]-[6], the design method of the MPPT strategy of two-stage grid-tied inverter systems has been discussed. The low-voltage-ride-through (LVRT) problem of the two-stage grid-tied inverter has been discussed in [12], [13], and several control approaches have been proposed to increase the LVRT capability of the PV system.

Besides the research effort on the control of two-stage grid-tied inverter systems, various circuit topologies also have been discussed in the past decades. In [14], a three-level-stacked neutral point clamped (3L-SNPC) topology is proposed for the two-stage grid-tied inverter system. The proposed 3L-SNPC topology, as well as a new pulse-width-modulation (PWM) strategy, can enhance the converter efficiency, especially in the low-power region. The power loss of the two-stage inverter system has been analyzed, and a comparison of the single-stage and two-stage designs has been provided in [15]. In [16], a high step-up boost-integrated flyback converter is used as the dc-dc stage. The proposed dc-dc stage can work in the soft-switching condition, and thus, the switching loss can be notably reduced. Detailed analysis and comparison between different dc-dc topologies for the two-stage inverter system have been provided in [17], and a novel semi-isolated multi-input dc-dc topology has been proposed for the two-stage inverter system. All of those research efforts have enhanced the stability, efficiency, and output power quality of the two-stage grid-tied inverter system.

### 1.3 Challenges and problem definitions

As mentioned earlier, various research effort on the control and topology of the two-stage grid-tied inverter system have enhanced the stability, efficiency, and power quality of the PV system. However, challenges still remain in the reliability improvement of the two-stage grid-tied inverter system. It can be seen from Figure 1-1 that there are three major parts in the two-stage grid-tied

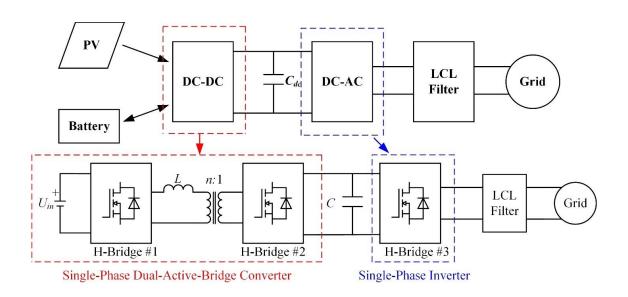

inverter system, i.e., the dc-dc stage, the dc-link capacitor, and the grid-tied dc-ac inverter. In this dissertation, three novel control algorithms are presented to enhance the reliability of the dc-dc stage, dc-link capacitor, and the grid-tied inverter stage, respectively. The two-stage grid-tied inverter investigated in this work contains a single-phase dual-active-bridge (DAB) dc-dc converter and a single-phase grid-tied inverter, and Figure 1-2 shows the schematic of the inverter system. The DAB converter is a bi-directional dc-dc converter with soft-switching capability. Due to the bi-directional power transmission capability, the DAB converter could be used in not only the conventional solar generation system but the solar-plus-storage applications. Besides, a standard H-bridge design could be adopted in the proposed two-stage grid-tied converter system to further enhance the modularity and flexibility.

Figure 1-2. Schematic of the proposed two-stage grid-tied inverter system.

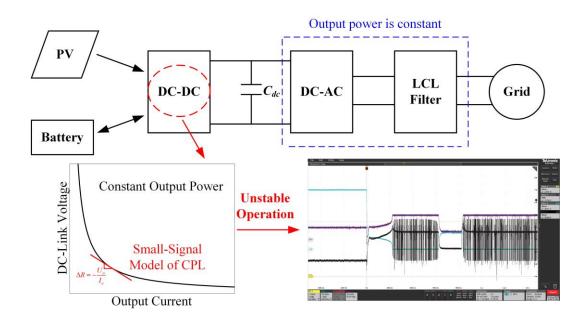

When the dc-ac stage provides constant power to the grid, the inverter stage will be a constant power load (CPL) to the dc-dc stage. However, the small-signal model of the CPL indicates a negative resistance, which deteriorates the stability of the dc-dc stage. As an example, Figure 1-3 shows the unstable dc-link voltage control due to the CPL. Due to the negative resistance

characteristic of the CPL, the voltage controller of the dc-dc stage is unstable. Thus, the design of the dc-dc converter voltage controller must consider the system stability under the CPL. Meanwhile, the voltage controller should also be able to provide a satisfactory command voltage tracking performance. Thus, the first reliability challenge of the two-stage grid-tied inverter is the robust voltage control of the dc-dc stage.

Figure 1-3. Unstable dc-dc converter due to the CPL.

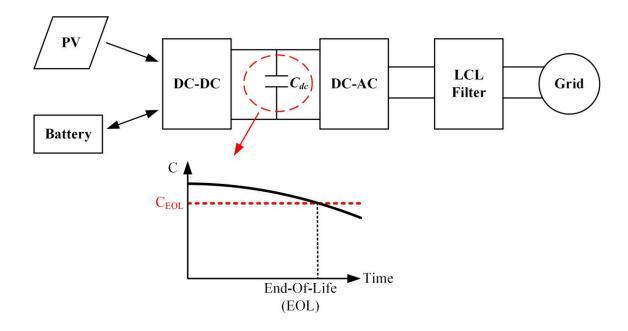

As the energy buffer, the dc-link capacitor connects the dc-dc stage and the dc-ac stage, and it also determines the reliability of the whole converter system. Besides, the dc-link capacitor also impacts the voltage control performance of the dc-dc stage, since it plays a vital role in the small-signal model of the DAB converter [2]. However, during the operation of the grid-tied inverter system, the actual dc-link capacitance may vary from its nominal value due to the component tolerance, thermal stress, and also capacitor degradation. As an example, Figure 1-4 shows the capacitance degradation over the long-term operation of the inverter system. It can be seen that the end-of-life of the dc-link capacitor can be indicated by the actual capacitance. By monitoring the

actual dc-link capacitance, the health status of the dc-link capacitor could be known. Thus, the second need for reliability enhancement of the two-stage grid-tied inverter system is the online monitoring of the actual dc-link capacitance.

Figure 1-4. DC-link capacitance degradation.

When the dc-ac stage is connected to the grid, an output filter is necessary to attenuate the switching ripples and satisfy the grid code. In practice, the LCL-type filter is commonly adopted in grid-tied inverter applications. Compared with the L-type filter, the LCL filter can provide better switching ripple attenuation performance with reduced filter volume. However, the resonance of the LCL filter could deteriorate the stability of the inverter. Especially, the resonant frequency of the LCL filter is affected by the component tolerance, as well as the grid impedance. The drifting resonant frequency can increase the difficulties in the design of the damping scheme and further reduce the stability margin of the grid-tied inverter. Figure 1-5 shows that the actual resonant frequency of the LCL filter is impacted by the grid-side impedance, and the inverter controller cannot maintain the stability of the inverter system under the resonant frequency drifting. Thus,

the third reliability challenge of the two-stage grid-tied inverter is the online estimation of the actual resonant frequency of the LCL filter.

Figure 1-5. Unstable dc-ac stage due to the LCL filter resonant frequency drifting.

In this work, three control schemes to enhance the reliability of the grid-tied inverter system will be presented to solve the challenges that are discussed earlier. First, an uncertainty and disturbance estimator (UDE) based robust voltage control scheme is proposed for the DAB converter to improve the robustness of the dc-dc stage, especially under the CPL. Second, a high-frequency (HF) signal injection based dc-link capacitor estimation scheme is presented to provide the online estimate of the actual dc-link capacitance. Moreover, in order to estimate the actual resonant frequency of the LCL filter, an adaptive extremum seeking control (AESC) based LCL resonant frequency estimation scheme is also presented in this work. Rigorous theoretical analysis, simulations, and comprehensive experimental studies have been performed to validate the

effectiveness of the proposed schemes. With the proposed control strategies, the discussed challenges can be effectively solved and the overall reliability of the two-stage grid-tied inverter system will be notably enhanced.

#### 1.4 Outline

This dissertation is organized as follows:

- Chapter 2 presents a UDE-based robust voltage control algorithm for the DAB converter. A linear output current based DAB model is proposed. Based on the linear DAB converter model, a UDE-based DAB converter voltage control scheme is presented. The proposed scheme can actively estimate and reject the converter uncertainty and disturbance, and thus, the voltage tracking performance and be enhanced. Besides, the CPL of the DAB converter has been analyzed in detail, and the proposed scheme can notably improve the DAB converter robustness and stability when feeding a CPL. Comprehensive experimental studies have been conducted to validate the effectiveness of the proposed voltage control algorithm.

- Chapter 3 describes the HF signal injection based dc-link capacitor estimation scheme. The proposed dc-link capacitor estimation scheme can provide an online estimate of the dc-link capacitor, which can be used for the component health monitoring. The deadtime of the DAB converter has been analyzed in detail, and a deadtime compensation scheme is proposed to further enhance the estimation accuracy. Both hardware-in-the-loop (HIL) and experimental studies have been performed to demonstrate and validate the effectiveness and performance of the proposed scheme.

- Chapter 4 presents an online estimation scheme for the LCL filter resonant frequency. By injecting an HF signal into the filter network, the proposed AESC-based estimation scheme can estimate the actual resonant frequency of the LCL filter, which will be impacted by the component tolerance and grid-side impedance. An adaptive law is proposed to actively adjust the magnitude of the injection signal, which can tradeoff the dynamic response and the steady-state inverter output power quality. The effectiveness of the proposed estimation scheme has been validated through experiments.

- Chapter 5 provides the conclusions and the future research recommendations for the work proposed in this dissertation.

#### 1.5 Reference

- [1]. Silverman, T. J., and H. Huang. "Solar energy technologies office multi-year program plan." US Dept. Energy Sol. Energy Technol. Office, Washington, DC, USA, Tech. Rep. DOE/EE-2346, May 2021.

- [2] Y. Wu et al., "A 150-kW 99% Efficient All Silicon Carbide Triple-Active-Bridge Converter for Solar-Plus-Storage Systems," IEEE Journal of Emerging and Selected Topics in Power Electronics, early access, doi: 10.1109/JESTPE.2020.3044572.

- [3] L. Chen, A. Amirahmadi, Q. Zhang, N. Kutkut and I. Batarseh, "Design and Implementation of Three-Phase Two-Stage Grid-Connected Module Integrated Converter," IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 3881-3892, Aug. 2014.

- [4] X. Li, Y. Li, J. E. Seem and P. Lei, "Detection of Internal Resistance Change for Photovoltaic Arrays Using Extremum-Seeking Control MPPT Signals," IEEE Transactions on Control Systems Technology, vol. 24, no. 1, pp. 325-333, Jan. 2016.

- [5] B. Singh, S. Kumar and C. Jain, "Damped-SOGI-Based Control Algorithm for Solar PV Power Generating System," IEEE Transactions on Industry Applications, vol. 53, no. 3, pp. 1780-1788, May-June 2017.

- [6] F. Wang, T. Zhu, F. Zhuo and H. Yi, "An Improved Submodule Differential Power Processing-Based PV System With Flexible Multi-MPPT Control," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 94-102, March 2018.

- [7] C. Jain and B. Singh, "A Three-Phase Grid Tied SPV System With Adaptive DC Link Voltage for CPI Voltage Variations," IEEE Transactions on Sustainable Energy, vol. 7, no. 1, pp. 337-344, Jan. 2016.

- [8] C. Lam, W. Choi, M. Wong and Y. Han, "Adaptive DC-Link Voltage-Controlled Hybrid Active Power Filters for Reactive Power Compensation," IEEE Transactions on Power Electronics, vol. 27, no. 4, pp. 1758-1772, April 2012.

- [9] C. Jain and B. Singh, "An Adjustable DC Link Voltage-Based Control of Multifunctional Grid Interfaced Solar PV System," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 2, pp. 651-660, June 2017.

- [10] Y. Du, D. D. -C. Lu, G. M. L. Chu and W. Xiao, "Closed-Form Solution of Time-Varying Model and Its Applications for Output Current Harmonics in Two-Stage PV Inverter," IEEE Transactions on Sustainable Energy, vol. 6, no. 1, pp. 142-150, Jan. 2015.

- [11] T. Messo, J. Jokipii, J. Puukko and T. Suntio, "Determining the Value of DC-Link Capacitance to Ensure Stable Operation of a Three-Phase Photovoltaic Inverter," IEEE Transactions on Power Electronics, vol. 29, no. 2, pp. 665-673, Feb. 2014.

- [12] C. Tang, Y. Chen and Y. Chen, "PV Power System With Multi-Mode Operation and Low-Voltage Ride-Through Capability," IEEE Transactions on Industrial Electronics, vol. 62, no. 12, pp. 7524-7533, Dec. 2015.

- [13] M. Mirhosseini, J. Pou and V. G. Agelidis, "Single- and Two-Stage Inverter-Based Grid-Connected Photovoltaic Power Plants With Ride-Through Capability Under Grid Faults," IEEE Transactions on Sustainable Energy, vol. 6, no. 3, pp. 1150-1159, July 2015.

- [14] Y. Wang and F. Wang, "Novel Three-Phase Three-Level-Stacked Neutral Point Clamped Grid-Tied Solar Inverter With a Split Phase Controller," IEEE Transactions on Power Electronics, vol. 28, no. 6, pp. 2856-2866, June 2013.

- [15] T. -F. Wu, C. -H. Chang, L. -C. Lin and C. -L. Kuo, "Power Loss Comparison of Single- and Two-Stage Grid-Connected Photovoltaic Systems," IEEE Transactions on Energy Conversion, vol. 26, no. 2, pp. 707-715, June 2011.

- [16] A. B. Shitole, S. Sathyan, H. M. Suryawanshi, G. G. Talapur and P. Chaturvedi, "Soft-Switched High Voltage Gain Boost-Integrated Flyback Converter Interfaced Single-Phase Grid-Tied Inverter for SPV Integration," IEEE Transactions on Industry Applications, vol. 54, no. 1, pp. 482-493, Jan.-Feb. 2018.

- [17] C. -W. Chen, C. -Y. Liao, K. -H. Chen and Y. -M. Chen, "Modeling and Controller Design of a Semi-isolated Multi-input Converter for a Hybrid PV/Wind Power Charger System," IEEE Transactions on Power Electronics, vol. 30, no. 9, pp. 4843-4853, Sept. 2015.

#### **CHAPTER 2**

#### UDE-BASED ROBUST VOLTAGE CONTROL FOR DAB CONVERTERS

#### 2.1 Introduction

The DAB converter has been widely adopted in many industrial applications, including the DC microgrids, renewable energy systems, on-board chargers for electrical vehicles, more electric aircrafts (MEA) and etc., as it could achieve isolated bi-directional power transmission with softswitching capability [1]-[7]. However, the system nonlinearities and external disturbances, e.g., the deadtime effect, on-state voltage drop of power devices, and load changes, will lead to tracking error in the DAB output voltage. Moreover, similar to other types of digital controlled converters [8], [9], there is at least one-step computation delay in the digital controlled DAB converter [10]. This time delay will lead to additional phase lag and deteriorate the system stability. Thus, it is still desirable to design a DAB controller to achieve the high-performance voltage tracking, which is robust against the system uncertainties and external disturbances.

Besides those uncertainties and disturbances of the DAB converter itself, the characteristics of the load can also pose significant challenges in the controller design. For example, when a DAB converter is used in a cascaded dc power conversion system, the load of the DAB converter could be other dc-dc or dc-ac converters rather than the passive loads [11]. In this configuration, the load of the DAB converter could be regarded as a constant-power load (CPL) as the second stage converter, when tightly regulated, providing a constant output power to its load regardless the input voltage. The characteristics of the two-stage inverter studied in this work is similar, where the load stage of the dc front-end can be viewed at CPL when the load power is tightly regulated. The small-signal model of the CPL exhibits negative incremental resistance [6], [11]-[16], which

significantly affect the stability of the converter. To address this issue due to CPLs, passive damping network could be introduced to the converter system to improve the system stability [14]. However, passive components can lead to additional power losses and reduce the efficiency. Active damping schemes also have been proposed to improve the stability with reduced power losses [11], [12]. Nevertheless, the conventional active damping scheme is achieved by emulating the passive components, which may conflict with other control objectives [14]. Thus, additional design effort for the high-performance DAB controller is still required to take into the account of the load characteristics.

To attenuate the disturbances and uncertainties, various types of disturbance rejection control (DRC) has been proposed. Based on the design domains, the conventional DRC schemes could be classified into two categories: frequency-domain DRC and time-domain DRC [17]. Among the frequency-domain DRC schemes, the disturbance observer (DOB) has been widely adopted in the control systems, which utilizes a disturbance estimate filter to achieve the compensation of the disturbances, and the disturbance rejection performance could be easily realized by selecting proper disturbance estimate filter [17]-[19]. Meanwhile, DRC design could also be conducted in the time-domain, like the active disturbance rejection control [20]. Compared with the frequency-domain counterparts, the state-space based time-domain DRC schemes is more suitable for multiple-input multiple-output system. Recently, a mix-domain DRC scheme, uncertainty and disturbance estimator (UDE) based control, has been proposed to attenuate lumped disturbances and improve the disturbance rejection performance [21]-[23]. Compared with those single domain control schemes, UDE achieves the nominal feedback control and estimates the lumped disturbance through the use of system time-domain model and states measurements, then a

frequency-domain filter is used to make the control law causal and improve the system robustness to measurement noises.

In this chapter, starting from the concept and preliminary study presented in [24], an UDE based voltage controller is proposed for the DAB converters to improve the system robustness while achieving the high accuracy tracking. First, the DAB converter circuit model and the model of the phase-shift modulation are integrated and re-modeled based on the converter output current to provide a generic linear model for the DAB controller design. Then a UDE based voltage controller is designed based on the proposed DAB model and the computation time delay also has been considered in the design. Rigorous stability analysis has been provided as the guidance of the parameter tuning. Besides, the output impedance of the UDE controlled DAB converter is also derived to show the stability boundary when the converter feeds a CPL. Comparative experimental studies have been conducted to show the effectiveness of the proposed schemes. The experimental results have proved that the proposed scheme can notably improve the voltage tracking performance even under significant parameter uncertainties. Meanwhile, the excellent disturbance rejection performance of the proposed scheme could also extend the stability boundary when feeding the CPL.

## 2.2 A Brief Review of DAB Converters and UDE Scheme

## 2.2.1 Review of the DAB Converter

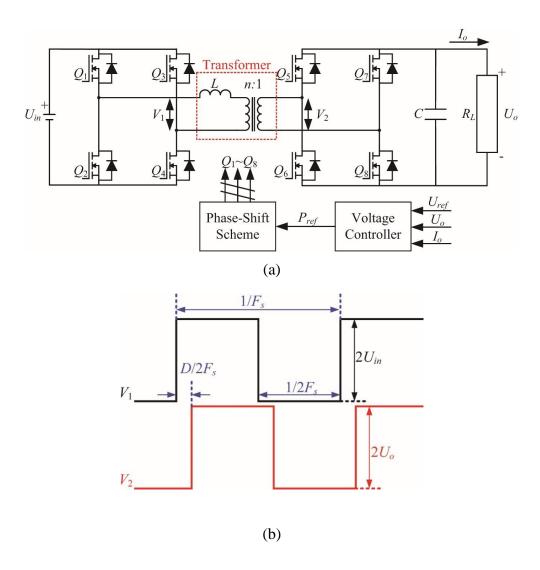

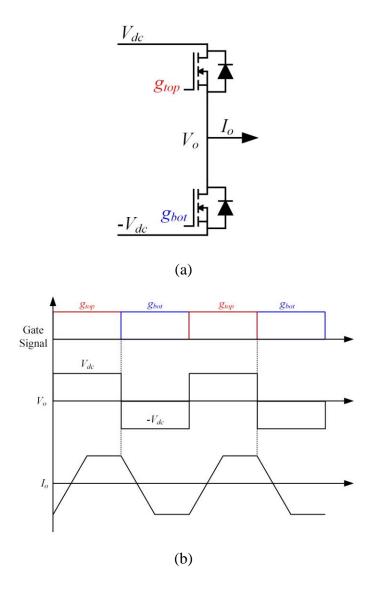

Figure 2-1. (a) Schematic of the DAB converter and (b) single-phase-shift modulation scheme.

Figure 2-1(a) shows the schematic of the DAB converter with phase-shift control scheme, where  $U_{in}$  is the input dc power supply,  $Q_1$ - $Q_8$  are power devices, C is the output capacitor,  $R_L$  represents the load, L is the leakage inductance of the transformer,  $I_o$  is the output current,  $U_o$  is the output voltage, and  $U_{ref}$  is the reference voltage that  $U_o$  should track. In order to transfer the

power between the input and output ports, phase-shift modulation schemes are commonly used in the DAB converter [3]. Figure 2-1(b) shows the most widely used single-phase-shift (SPS) modulation scheme, where  $V_1$  and  $V_2$  are the voltages across the transformer primary and secondary windings respectively, output voltage duty-ratio is fixed as 50%,  $F_s$  is the switching frequency, D is phase-shift angle. The power transferred between the input and output ports when the SPS scheme is applied could be written as

$$P = \frac{nU_{in}U_o}{2F_sL}D(1-D)$$

(2-1)

It should be noticed that the waveforms shown in Figure 2-1(b) are the ideal output voltages of the DABs. The deadtime must be inserted in practice to avoid shooting through the two switches in the same phase leg, which will lead to distortions in the output voltages and change the power transmission characteristic of the DAB converter. Thus, in this work, both the nonlinearities due to the deadtime effect, as well as the uncertainties caused by the circuit parameters, are regarded as the system uncertainties. The voltage controller should effectively compensate the system uncertainties and improve the voltage tracking accuracy.

## 2.2.2 Review of UDE

Consider a linear system with uncertainty and disturbance

$$\frac{dx}{dt} = (A + \Delta A)x(t) + Bu(t) + f(t)$$

(2-2)

where x(t) is the system state, u(t) is the input of the system, A and B are the known state matrixes,  $\Delta A$  represents the unknown dynamics of the system, and f(t) is the external disturbance [21]. The effect of the uncertainty and disturbance could be represented as  $u_d(t) = \Delta Ax(t) + f(t)$ , and the control

objective of UDE is to eliminate  $u_d(t)$  and ensure state variable x(t) tracks its reference  $x_m(t)$ . The reference state  $x_m(t)$  could be obtained through the reference model

$$\frac{dx_m}{dt} = A_m x_m(t) + B_m r(t) \tag{2-3}$$

where  $A_m$  and  $B_m$  are the reference system matrixes, which determine the closed-loop performance of the system, and r(t) is the reference signal. In other words, when a high-performance controller is adopted to the system and the state x(t) can tightly track its reference  $x_m(t)$ , the closed-loop system performance could be easily determined by selecting proper system matrixes  $A_m$  and  $B_m$ . In order to achieve the high accuracy tracking to the reference state  $x_m(t)$ , the tracking error could be defined as  $e(t) = x_m(t) - x(t)$ , and the converge rate of the tracking error could be defined through the following system

$$\frac{de}{dt} = A_m e(t) + Ke(t) \tag{2-4}$$

where K is the state-feedback gain and  $A_m+K$  should be Hurwitz. Combining the system model (2-2), desired closed-loop model (2-3), and the error convergence model (2-4), the control input should satisfy

$$u(t) = B^{+} \left\lceil A_{m}x(t) - Ax(t) + B_{m}r(t) - Ke(t) - u_{d}(t) \right\rceil$$

(2-5)

where  $B^+$  is the pseudoinverse of B.

However, it should be noticed that the uncertainty and disturbance is unknown in most of the practical applications. Thus, an estimate  $u_{de}(t)$  is introduced in u(t) to replace  $u_d(t)$ , which could be represented as

$$u_{de}(t) = g_f(t) * u_d(t)$$

$$= L^{-1} \left\{ G_f(s) \left\lceil sx(s) - Ax(s) - Bu(s) \right\rceil \right\}$$

(2-6)

where  $u_{de}$  is the estimate of  $u_d$ ,  $g_f$  is the impulse response of a strictly proper filter  $G_f(s)$ , \* represents the convolution operator, and  $L^{-1}$  is the inverse Laplace Transform operator. Thus,  $u_{de}(t)$  could achieve the estimate of  $u_d(t)$  within the bandwidth of  $G_f(s)$ . Besides, the introduction of the strictly proper stable function  $G_f(s)$  could also make the term  $G_f(s)sx(s)$  realizable.

## 2.3 UDE Based Robust Voltage Control for the DAB Converter

## 2.3.1 UDE Based Robust Voltage Control

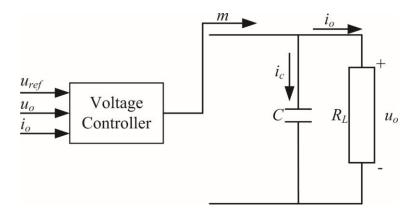

Figure 2-2. Output current model of the DAB converter.

Based on the power transmission characteristic of the SPS scheme (2-1), the relationship between the phase-shift angle D and the output power P is nonlinear, which increases the complexity when designing the controller. Moreover, when advanced phase-shift schemes are implemented, such as the dual- and triple-phase shift schemes, the power model can be more complicated [16]. To simplify the controller design and enhance the compatibility of the controller, an output current model of the DAB converter is shown in Figure 2-2, where  $u_{ref}$  is the reference

voltage that the output voltage  $u_o$  should track, m is the output current of the DAB converter, which consists of the output capacitor current, i.e.,  $i_c$ , and the load current, i.e.,  $i_o$ . Thus, the dynamic model of the DAB converter under the SPS scheme could be rewritten as

$$\begin{cases}

m = \frac{nU_{in}}{2F_sL}D(1-D) \\

\frac{du_o}{dt} = \frac{m-i_o}{C}

\end{cases}$$

(2-7)

$$D = \frac{1 - \sqrt{1 - 8F_s Lm_{ref} / (nU_{in})}}{2}$$

(2-8)

The revised model of the DAB converter (2-7) decouples the selection of the phase-shift schemes and the design of the DAB controller. The voltage controller could be designed based on the current model (2-7), which is a linear system regardless the phase-shift scheme. The output of the voltage controller is the converter output current m, which is then generated through the phase-shift scheme. Different phase-shift schemes could be utilized to achieve the optimization [3], while retaining the same voltage controller and control performance, as the current model (2-7) will be the same. Thus, the proposed current-oriented controller design concept could simplify the controller design. In contrast, if the output of the controller is directly designed as the phase-shift angle, the design of the controller must consider the complicated nonlinear converter model if advanced phase-shift schemes are utilized. Also, the controller will lose the generality, as the controller need to be redesigned if a different phase-shift scheme is deployed [2]. It should be noted that (2-8) is only valid for the ideal case, i.e., external disturbances, system uncertainties, computation time delay, and deadtime effect are not existed. In practice, the phase-shift angle D

calculated through (2-8) often leads to tracking errors in the output current m and affect the voltage tracking accuracy, as such the voltage controller should compensate the system uncertainties and eliminate the tracking error in the output voltage.

Considering the non-ideal system characteristics, including the deadtime, parameters uncertainty, external disturbance, computation time delay, etc., the ideal current model of the DAB converter (7) could be rewritten into a transfer function as

$$su_o(s) = \frac{e^{-T_s s} m \left[1 + \Delta_{Total}(s)\right] - i_o(s) + f(s)}{C}$$

(2-9)

where  $e^{-T_s s}$  is the one-step computation time delay,  $T_s = 1/F_s$  is the sampling period,  $\Delta_{Total}$  represents the system uncertainty, and f(s) is the external disturbance.

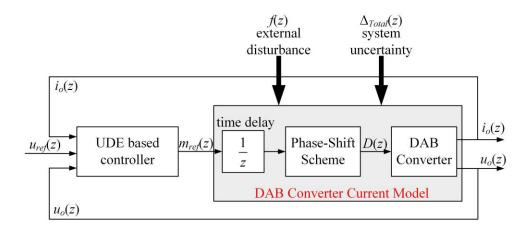

Figure 2-3. UDE controlled DAB converter.

Based on the UDE scheme reviewed in Section 2-2 and the DAB converter current model (2-9), define the reference system as

$$\frac{du_m}{dt} = -\alpha u_m(t) + \alpha u_{ref}(t) \tag{2-10}$$

where  $\alpha$ >0 is the bandwidth of the closed-loop DAB converter. The voltage tracking error is  $e(t)=u_m(t)-u_o(t)$ , whose dynamics satisfy

$$\frac{de}{dt} = -\alpha e(t) - ke(t) \tag{2-11}$$

Thus, the error convergence rate is determined by  $\alpha+k$ . Based on the UDE scheme and the system model (2-9), the control law can be written as

$$m_{ref}(t) = \underbrace{m_{fb}(t)}_{\text{state-feedback}} - f_e(t)$$

$$\underset{\text{estimation}}{\text{disturbance}}$$

(2-12)

where  $m_{fb}(t)$  is the nominal state-feedback, which satisfies

$$m_{fb}(t) = \alpha C \left[ u_{ref}(t) - u_o(t) + ke(t) \right] + i_o(t)$$

(2-13)

and  $f_e(t)$  is the estimate of the disturbance f(t), which could be written as

$$f_{e}(t) = g_{f}(t) * f(t)$$

$$= L^{-1} \left[ G_{f}(s) \right] * \left[ i_{o}(t) + C \frac{du_{o}}{dt} - m_{ref}(t - T_{s}) \right]$$

(2-14)

The nominal state-feedback term (2-13) could achieve the desired tracking performance if the time delay  $e^{-T_s s}$ , system uncertainty  $\Delta_{Total}(s)$ , and disturbance f(s) are not existed. The estimate of the disturbance  $f_e(t)$  is used to attenuate the unideal system dynamics. Here, the disturbance

estimate filter is designed as  $G_f(s) = \beta/(s+\beta)$ , which could estimate the disturbance within the bandwidth  $\beta$ . In summary, there are three controller parameters that need to be designed: closed-loop bandwidth  $\alpha$ , tracking error convergence rate k, and disturbance rejection bandwidth  $\beta$ . Figure 2-3 shows the block diagram of the UDE controlled DAB converter, where the proposed UDE controller measures the load current  $i_0(z)$  and output voltage  $u_0(z)$ , and generates the current reference  $m_{ref}(z)$ . Then the phase-shift scheme block will calculate the phase-shift angle accordingly, however, the angle will be deployed to the converter in the next switching period due to the computation delay.

## 2.3.2 Stability Analysis

Theorem 2-1: Consider a DAB converter system (2-9) controlled by the UDE based voltage controller (2-12)-(2-14), and the controller is digitalized with sampling time  $T_s$ . The system is stable if

- (1) roots of  $1/(zG_s(z)+\alpha+k)$  are within the unit circle;

- (2) external disturbance f(z) is bounded and system uncertainty  $\Delta_{Total}(z)$  is stable;

(3)

$$\left\| \frac{G_f(z)G_s(z) + \alpha + k}{zG_s(z) + \alpha + k} \Delta_{Total}(z) \right\|_{\infty} < 1$$

(2-15)

where  $z = e^{T_s s}$  and  $G_f(z)$ ,  $G_s(z)$ , f(z), and  $\Delta_{Total}(z)$  are the Z-domain counterparts of the filter  $G_f(s)$ , derivative operator s, disturbance f(s), and uncertainty  $\Delta_{Total}(s)$  respectively.

*Proof:* The control law in (2-12)-(2-14) could be rewritten as

$$m_{ref}(z) = m_{fb}(z) - f_{e}(z)$$

$$= \alpha C \left[ u_{ref}(t) - u_{o}(t) + ke(t) \right] + i_{o}(t)$$

$$-G_{f}(z) \left[ i_{o}(t) + CG_{s}(z) u_{o}(z) - \frac{m_{ref}(z)}{z} \right]$$

$$= \frac{z}{z - G_{f}(z)} \left[ \alpha C u_{ref}(z) - \alpha C u_{o}(z) + kCe(z) + i_{o}(z) - G_{f}(z) i_{o}(z) - CG_{f}(z) G_{s}(z) u_{o}(z) \right]$$

$$(2-16)$$

Combining (2-16) with the DAB converter model (2-9), the output voltage  $u_o$  could be written

$$u_{o}(s) = \frac{m_{ref}(z)}{z} \left[ 1 + \Delta_{Total}(z) \right] - i_{o}(z) + f(z)$$

$$= \left[ \alpha C u_{ref}(z) - \alpha C u_{o}(z) + k C e(z) + i_{o}(z) - G_{f}(z) i_{o}(z) \right]$$

$$- C G_{f}(z) G_{s}(z) u_{o}(z) \left[ \frac{1 + \Delta_{Total}(z)}{C G_{s}(z) \left[ z - G_{f}(z) \right]} \right]$$

$$- \left[ \frac{i_{o}(z) - f(z) \right] \left[ z - G_{f}(z) \right]}{C G_{s}(z) \left[ z - G_{f}(z) \right]}$$

$$= \frac{\left[ 1 + \Delta_{Total}(z) \right] \left[ \alpha u_{ref}(z) + k u_{m}(z) \right] + \left[ \frac{z - G_{f}(z) \right] f(z)}{C} \right] }{z G_{s}(z) + \alpha + k + \Delta_{Total}(z) \left[ G_{f}(z) G_{s}(z) + \alpha + k \right]}$$

$$+ \frac{\Delta_{Total}(z) \left[ 1 - G_{f}(z) \right] + (1 - z)}{z G_{s}(z) + \alpha + k + \Delta_{Total}(z) \left[ G_{f}(z) G_{s}(z) + \alpha + k \right]} \frac{i_{o}(z)}{C}$$

where  $u_m(z)$  is the Z-domain counterpart of  $u_m(s)$ .

as

As the external disturbance f(z) is bounded and the system uncertainty  $\Delta_{Total}(z)$  is stable, the closed-loop system stability is determined by

$$\frac{1}{zG_{s}(z) + \alpha + k + \Delta_{Total}(z) \left[G_{f}(z)G_{s}(z) + \alpha + k\right]}$$

$$= \frac{1}{zG_{s}(z) + \alpha + k} \frac{1}{1 + \frac{G_{f}(z)G_{s}(z) + \alpha + k}{zG_{s} + \alpha + k}} \Delta_{Total}(z)$$

(2-18)

Thus, based on the small gain theorem [25] and (2-18), the closed-loop stability requires that

$$\frac{1}{zG_s(z) + \alpha + k} \text{ is stable and } \left\| \frac{G_f(z)G_s(z) + \alpha + k}{zG_s(z) + \alpha + k} \Delta_{Total}(z) \right\|_{\infty} < 1.$$

Based on (2-17), the voltage tracking error satisfies

$$e(z) = u_{m}(z) - u_{o}(z)$$

$$= \frac{G_{s}(z)(z-1) + \Delta_{Total}(z)G_{s}(z)[G_{f}(z)-1]}{zG_{s}(z) + \alpha + k + \Delta_{Total}(z)[G_{f}(z)G_{s}(z) + \alpha + k]} u_{m}(z)$$

$$- \frac{[z-G_{f}(z)]f(z) + \{\Delta_{Total}(z)[1-G_{f}(z)] - (1-z)\}i_{o}(z)}{C\{zG_{s}(z) + \alpha + k + \Delta_{Total}(z)[G_{f}(z)G_{s}(z) + \alpha + k]\}}$$

(2-19)

Remark 2-1: The tracking error (2-19) suggests that the uncertainty  $\Delta_{Total}(z)$  and disturbance f(z) could be effectively attenuated when  $1-G_f(z)\approx 0$  and  $z-G_f(z)\approx 0$  respectively. Especially, at low-frequency region ( $\omega < F_s / 10$ ), the disturbance rejection performance also could be represented by  $\left|1-G_f(j\omega)\right|$ , as  $e^{T_s / i\omega} \approx 1$ . A high bandwidth  $G_f(z)$  could reject the disturbance well. However, as the stability condition (2-15) shows, high bandwidth may result in instability when the amplitude of the system uncertainty  $\Delta_{Total}(z)$  is large. Thus, the design of  $G_f(z)$  needs to tradeoff between disturbance rejection performance and stability performance.

Remark 2-2: Besides the deadtime effect, one of the major sources for system uncertainty is the circuit parameters perturbation. Especially, the leakage inductance L and output capacitance C may deviate from their nominal values. Supposing  $L_d$  and  $C_d$  are the parameters error of the leakage inductance and output capacitor, while  $L_n$  and  $C_n$  are the nominal values used in the controller design. The actual circuit parameters satisfy  $L=L_d+L_n$  and  $C=C_d+C_n$ . The system uncertainty caused by the leakage inductance and output capacitance perturbations are marked as  $\Delta_L$  and  $\Delta_C$  respectively. Based on (2-7) and (2-9),  $\Delta_L$  could be written as  $\Delta_L(z) = \frac{-L_d}{L_n + L_d}$ . Similarly, the system uncertainty caused by the capacitance error could be represented as  $\Delta_C(z) = \frac{C_d}{C_n} \left[ 1 - \frac{i_o(z)}{CG_s(z)u_o(z) + i_o(z)} \right]$ . The modeling of the uncertainties caused by the circuit parameters perturbation could be used in the robustness analysis.

## 2.3.3 Stability Under the CPL

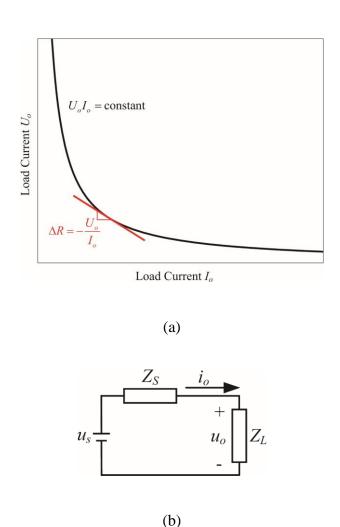

Figure 2-4. (a) Negative incremental impedance of a CPL and (b) impedance model of the UDE controlled DAB converter.

When the DAB converter feeds a CPL, only the nominal stability condition given in Theorem 2-1 cannot ensure the stability. Figure 2-4(a) shows the voltage-current relationship of the CPL, and the incremental impedance of the CPL could be written as  $\Delta R$ =- $U_o/I_o$ . Figure 2-4(b) is the equivalent impedance model of the UDE controlled DAB converter [14], where  $u_s$  is the ideal voltage source representing the converter output voltage under the no load situation,  $Z_s$  is the

output impedance of the converter,  $Z_L$  is the load,  $u_o$  is the output voltage, and  $i_o$  is the output current. Based on (2-17), the ideal voltage source is

$$u_{s}(s) = \frac{\left[1 + \Delta_{Total}(z)\right] \left[\alpha u_{ref}(z) + k u_{m}(z)\right] + \frac{\left[z - G_{f}(z)\right] f(z)}{C}}{z G_{s}(z) + \alpha + k + \Delta_{Total}(z) \left[G_{f}(z) G_{s}(z) + \alpha + k\right]}$$

(2-20)

and the output impedance  $Z_S$  could be written as

$$Z_{s}(s) = \frac{\Delta_{Total}(z)[1 - G_{f}(z)] + (1 - z)}{zG_{s}(z) + \alpha + k + \Delta_{Total}(z)[G_{f}(z)G_{s}(z) + \alpha + k]} \frac{1}{C}$$

$$= \frac{1}{C[zG_{s}(z) + \alpha + k]} \frac{\Delta_{Total}(z)[G_{f}(z) - 1] + (z - 1)}{1 + \frac{G_{f}(z)G_{s}(z) + \alpha + k}{zG_{s}(z) + \alpha + k}} \Delta_{Total}(z)$$

(2-21)

Thus, the output voltage  $u_o(z)$  could be written as

$$u_{o}(z) = \frac{Z_{L}(z)}{Z_{s}(z) + Z_{L}(z)} u_{s}(z)$$

$$= \frac{1}{1 + \frac{Z_{s}(z)}{Z_{L}(z)}} u_{s}(z)$$

(2-22)

It can be seen from (2-22) that the nominal stability condition given in Theorem 2-1 could ensure the stability of  $Z_S$ . However, when the load impedance  $Z_L(z)$  is a negative constant, i.e.,  $Z_L(z) = -U_o/I_o$ , a stable  $Z_S(s)$  cannot ensure the system stability. Based on the small gain theorem [25], a sufficient condition for the system stability is

$$\left\| \frac{Z_s(z)}{Z_L(z)} \right\|_{\infty} < 1 \tag{2-23}$$

Although the stability condition (2-23) may lead to a more conservative requirement on  $Z_S(z)$ , a small value of  $Z_S(z)$  is always desired as it could improve the tracking performance of the converter. Thus, the stability of the DAB converter when feeding CPL and a good tracking performance could be obtained by reducing the amplitude of the output impedance  $Z_S(z)$ . Based on (2-21), the introduction of  $G_f(z)$  could effectively attenuate the system uncertainties and reduce the output impedance within its bandwidth.

## 2.3.4 Controller Design

Based on the derived control law (2-12)-(2-14), there are three parameters needed to be designed: the closed-loop bandwidth  $\alpha$ , the error convergence rate k, and the disturbance rejection bandwidth  $\beta$ . In order to maintain the system stability, the stability criteria given in Theorem 2-1 should be satisfied. Moreover, the output impedance of the UDE controlled DAB converter should also satisfy (2-23) when feeding a CPL. The detailed design process will be discussed in following.

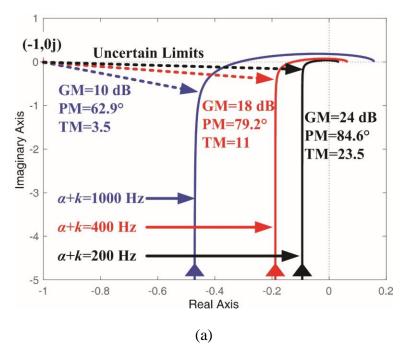

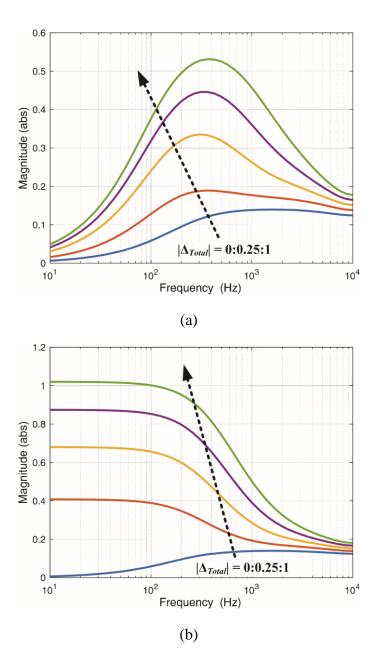

First, the closed-loop bandwidth and error convergence rate could be designed based on the requirement that the roots of  $1/(zG_s(z)+\alpha+k)$  are within the unit circle. Figure 2-5(a) shows the Nyquist plot of system  $1/(zG_s(z)+\alpha+k)$ , where GM is the gain margin in dB, PM is the phase margin in degrees, and TM is the time delay margin in steps. It can be seen that a good robustness and dynamic performance could be obtained when  $\alpha+k=400$  Hz. Larger  $\alpha+k$  could improve the dynamic response at the cost of worse robustness. Here, the closed-loop bandwidth  $\alpha$  is selected as 100 Hz, and the error convergence rate k is designed as 300 Hz. Then the design of

bandwidth is set as  $\beta$ =400 Hz to tradeoff between the system robustness and disturbance rejection performance. Figure 2-5(b) shows the frequency response of  $\left| \frac{G_f(z)G_s(z) + \alpha + k}{zG_s(z) + \alpha + k} \Delta_{Total}(z) \right|$ . It

the disturbance estimate filter should satisfy (2-3). In this work, the disturbance rejection

can be seen that a 400 Hz disturbance rejection bandwidth could maintain the system stability even under 30% circuit parameters error. Figure 2-5(c) shows the system stability performance under different closed-loop bandwidths and error convergence rates, when the disturbance rejection bandwidth  $\beta$  is fixed as 400 Hz and both L and C have 30% error. It can be seen that the system robustness is deteriorated when a high  $\alpha+k$  is adopted, which matches the trend shown in Figure 2-5(a).

Figure 2-5. (a) Nyquist plot of  $\frac{1}{zG_s(z)+\alpha+k}$ , (b) and (c) frequency responses of  $\left|\frac{G_f(z)G_s(z)+\alpha+k}{zG_s(z)+\alpha+k}\Delta_{Total}(z)\right|$ : (b) under different parameter uncertainties and (c) under different closed-loop bandwidths and error convergence rates.

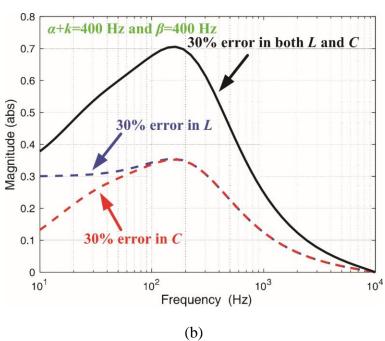

Considering the DAB converter feeding a CPL, the output impedance of the converter is shown in Figure 2-6. The system uncertainty  $\Delta_{Total}(z)$  is regarded as a constant to show the effectiveness of the disturbance compensation. It can be seen that the introduction of  $G_f(z)$  could notably reduce the amplitude of  $Z_S(z)$  which means a larger stable margin is obtained when feeding a CPL. Based on Figure 2-6(a) and (2-23), the maximum negative resistance that the UDE controlled DAB converter could feed is  $Z_L$ =-0.54  $\Omega$ . In this work, a 120 W CPL is considered, and the maximum output voltage and current of the converter is 200 V and 10 A respectively. Thus, the maximum negative incremental resistance of the CPL is  $\Delta R_{max}$ =-1.2  $\Omega$  and the UDE controlled converter could maintain the system stability.

Figure 2-6. Output impedance of the UDE controlled DAB converter. Bandwidth of (a)  $G_f(z) = 400 \text{ Hz}$  and (b)  $G_f(z) = 0$ .

# 2.4 Experimental Studies

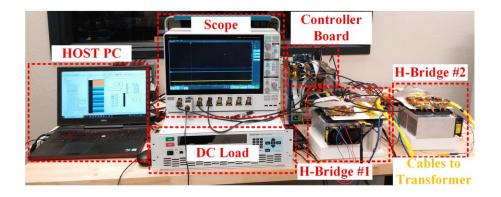

Figure 2-7. Experimental Setup.

TABLE 2-1 Key Parameters of the DAB Converter used in the Experimental Study

| Parameter              | Value  | Parameter                               | Value  |

|------------------------|--------|-----------------------------------------|--------|

| Input Voltage $U_{in}$ | 100 V  | Turns Ratio n                           | 1      |

| Leakage Inductance L   | 80 μΗ  | Closed-Loop Bandwidth α                 | 100 Hz |

| Output Capacitor C     | 195 μF | Error Convergence Rate k                | 300 Hz |

| Power of CPL           | 120 W  | Disturbance Rejection Bandwidth $\beta$ | 400 Hz |

To verify the effectiveness of the proposed schemes, a series of comparative experiments are conducted. Table 2-1 summarized the converter and controller parameters. For comparison purpose, a proportional-integral (PI) controller is also tested. The PI controller is designed based on the DAB converter current model (2-7), and the controller structure is almost the same as the

one shown in Figure 2-3 except that the UDE controller is replaced by the PI controller. Moreover, the output current feedforward compensation is also implemented with the PI controller to improve the dynamic response, and the control output of the PI controller could be written as

$$m_{ref|PI}\left(z\right) = \left(k_p + k_i \frac{T_s}{z - 1}\right) \left[u_{ref}\left(z\right) - u_o\left(z\right)\right] + i_o\left(z\right)$$

(2-24)

where  $k_p$  and  $k_i$  are the PI gains. In this work, the PI controller is designed as  $k_p$  =0.34 and  $k_i$ =216, and the closed-loop system bandwidth of the PI controlled DAB converter is also 400 Hz to ensure a fair comparison, which is the same as the disturbance rejection bandwidth of the UDE controller. Figure 2-7 shows the experiment setup. The deadtime of the converter is set as 2  $\mu$ s.

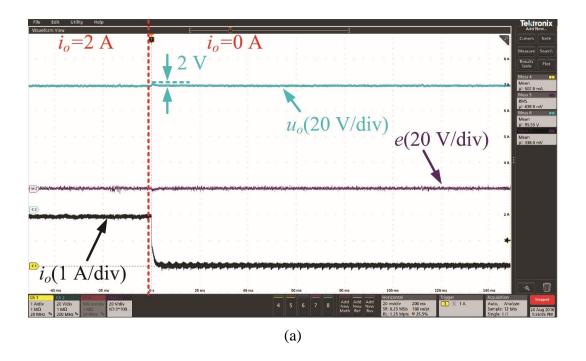

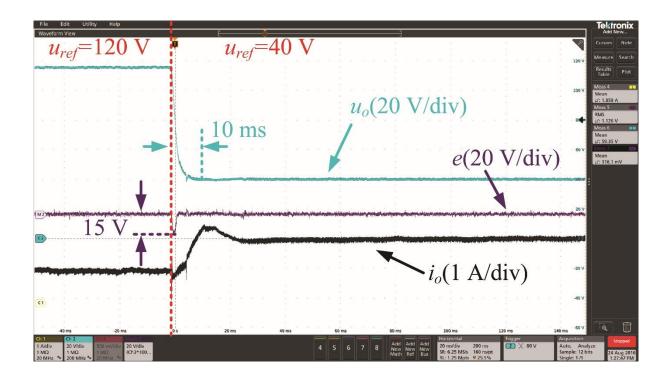

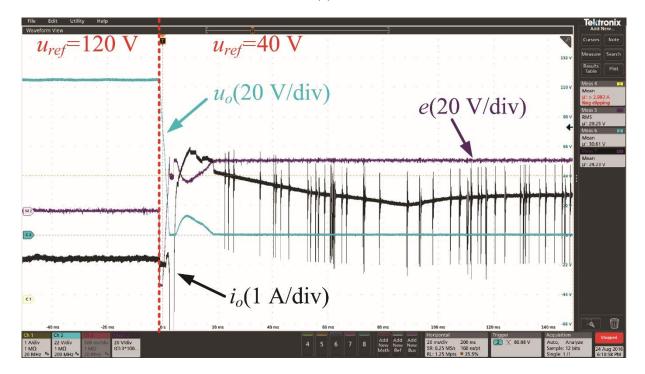

Figure 2-8. Transient responses of the DAB converter under load step change with different controllers: (a) UDE controller with 400 Hz bandwidth  $G_f(z)$  (b) UDE controller with  $G_f(z)$ =0, and (c) PI controller.

Figure 2-8 shows the dynamic responses of the DAB controller with different controllers, where the output current changes from 2 A to 0 A and the reference output voltage is  $u_{ref}$ =100 V. It can be seen that with the 400 Hz bandwidth disturbance compensation, the UDE controller could effectively attenuate the disturbance, and the tracking error is relatively small. Without the disturbance compensation, i.e.,  $G_f(z)$ =0, it can be seen that the tracking error cannot converge to 0. Actually, both Figure 2-6 and (2-21) show that the system uncertainty will affect the converter output impedance, and  $G_f(z)$  could notably attenuate the system uncertainty and reduce the output impedance within its bandwidth. Lower output impedance means that the output voltage is more robust when the load changes. Similar to the UDE controller, the PI controller could also achieve the zero steady-state voltage tracking, but the disturbance attenuation performance is worse than the UDE controller.

(a)

(b)

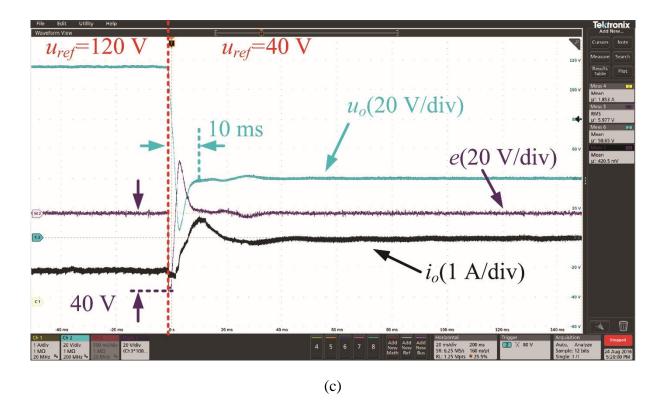

Figure 2-9. Transient responses of the DAB converter when feeding a 120 W CPL with different controllers and accurate parameters: (a) UDE controller with 400 Hz bandwidth  $G_f(z)$  (b) UDE controller with  $G_f(z)$ =0, and (c) PI controller.

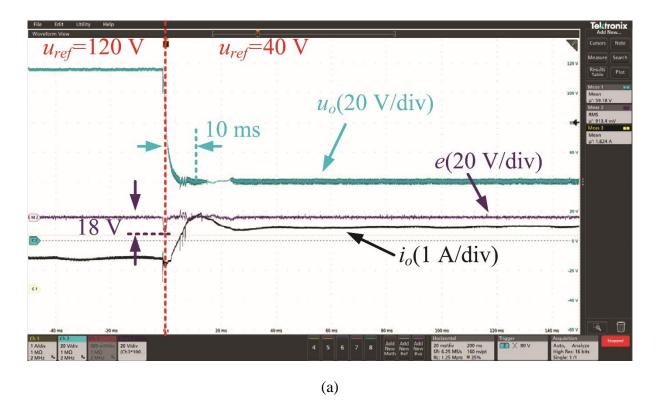

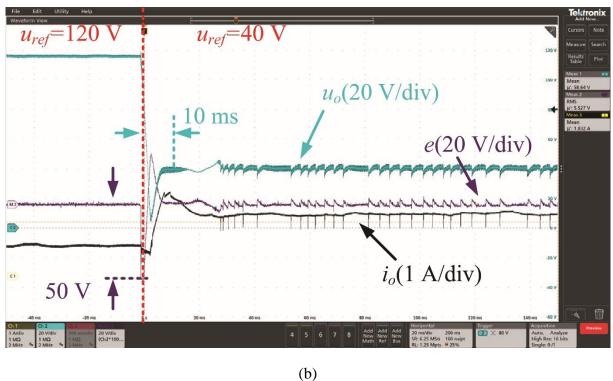

Figure 2-9 shows the DAB converter voltage responses when feeding a 120 W CPL. The CPL is emulated by using a programmable DC load. The reference voltage  $u_{ref}$  changes from 120 V to 40 V, and the UDE controller with disturbance compensation achieves the voltage tracking within 10 ms, which means the closed-loop performance of the UDE controlled DAB converter is matched with the designed reference system. The maximum tracking error during the transient response is also low. However, when the disturbance compensation is not enabled, i.e.,  $G_f(z)$ =0, the system is unstable. Based on Figure 2-6, without disturbance compensation, the output impedance of the DAB converter is determined by the system uncertainty, especially in the low-frequency region. Based on the stability condition shown in (2-23), a low output impedance is always desired, as it could improve both the voltage tracking performance and system stability when feeding a CPL. Figure 2-9(c) shows that the PI controller could also maintain the system

stability and achieve the voltage tracking. However, the tracking overshoot of the PI controller is much higher than that of the UDE controller, which is almost not existed.

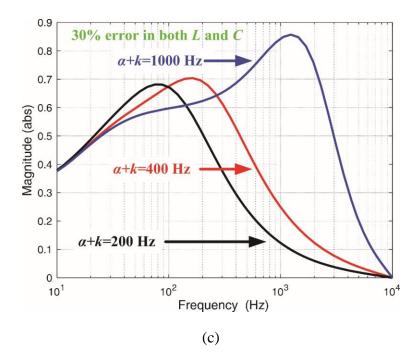

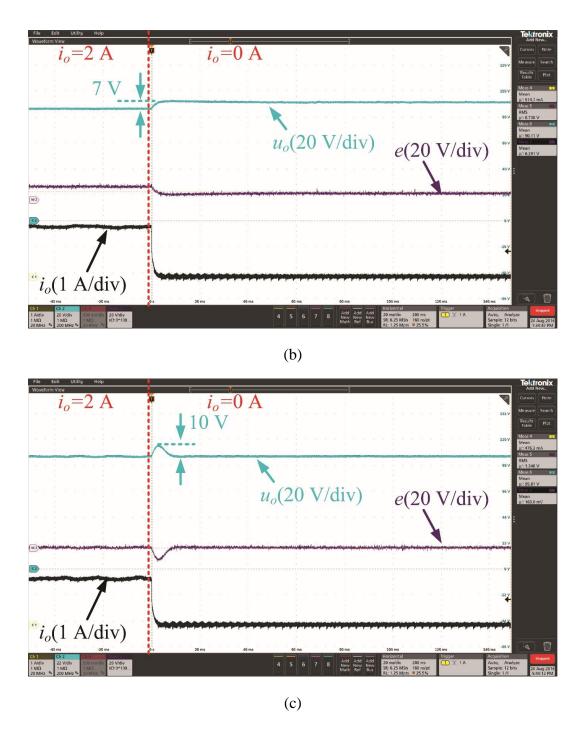

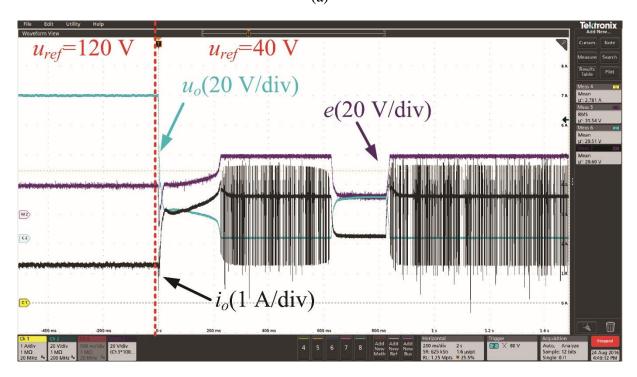

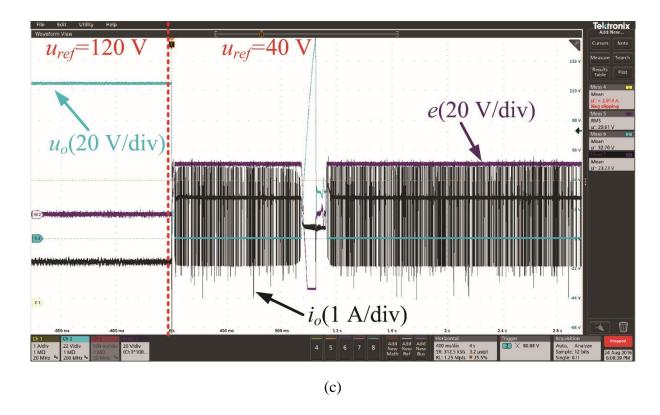

Figure 2-10 shows the system voltage responses when feeding the same CPL. However, the circuit parameters used in the controller design have 30% error, i.e., L=56  $\mu$ H and C=136.5  $\mu$ F rather than the values shown in Table 2-1 are used in the UDE and PI controllers design. It can be seen that the UDE controller with disturbance compensation maintains excellent tracking performance even under the high system uncertainty, and the closed-loop performance is still matched with the designed reference system. However, similar to the accurate parameters test, without  $G_f(z)$ , the UDE control law cannot maintain the system stability due to the large output impedance. Similarly, the PI controller is also unstable under the high system parameters uncertainty. In practical applications, not only the circuit parameters uncertainties, but also the deadtime uncertainty can affect the converter output performance.

(a)

(b)

Figure 2-10. Transient responses of the DAB converter when feeding a 120 W CPL with different controllers and 30% error in L and C: (a) UDE controller with 400 Hz bandwidth  $G_f(z)$  (b) UDE controller with  $G_f(z)$ =0, and (c) PI controller.

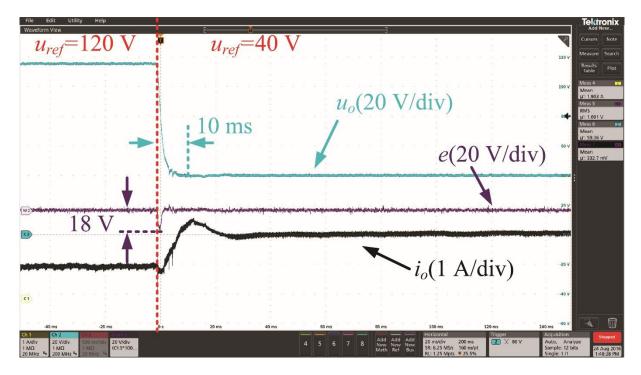

Figure 2-11 shows the system responses under the same 120 W CPL, but the converter deadtime has been doubled, i.e., 4 µs deadtime was used during the test. It can be seen that compared with the PI controller, the proposed UDE controller can still perform excellent tracking performance, while the PI controller almost reach the stability limitation due to the deadtime uncertainty and large overshoot as well as high voltage ripples occur in the voltage response. Thus, the proposed scheme could effectively improve the robustness and voltage tracking performance of the DAB converter.

Figure 2-11. Transient responses of the DAB converter when feeding a 120 W CPL with a doubled deadtime: (a) the proposed UDE controller and (b) PI controller.

#### 2.5 Conclusion

In this chapter, a UDE based robust voltage control scheme is proposed for DAB converters to improve the output voltage tracking performance and system robustness against internal and external disturbances and uncertainties. To simplify the controller design and improve the controller compatibility, a universal DAB converter model is proposed based on the converter output current. Then the UDE based voltage controller is proposed using the proposed universal DAB model. The one-step delay caused by the computation in digital controller is considered, and the rigorous stability analysis is presented. To enhance the robustness to the load dynamics, especially when feeding the CPLs, the output impedance of the UDE controlled DAB converter is presented for the first time. Based on the stability requirements, the design of the UDE based voltage controller could be accomplished by selecting three parameters: the closed-loop bandwidth  $\alpha$ , the error convergence rate k, and the disturbance rejection bandwidth  $\beta$ , which have strong physical significance. A series of comparative experiment studies have been conducted and the results are presented to validate the effectiveness of the proposed scheme.

#### 2.6 References

- [1] E. De Din, H. A. B. Siddique, M. Cupelli, A. Monti and R. W. De Doncker, "Voltage control of parallel-connected dual-active bridge converters for shipboard applications," IEEE Journal of Emerging and Selected Topics in Power Electroncis, vol. 6, no. 2, pp. 664-673, Jun. 2018.

- [2] B. Zhao, Q. Song and W. Liu, "Power characterization of isolated bidirectional dual-active-bridge DC–DC converter with dual-phase-shift control," IEEE Transactions on Power Electronics, vol. 27, no. 9, pp. 4172-4176, Sep. 2012.

- [3] B. Zhao, Q. Song, W. Liu and Y. Sun, "Overview of dual-active-bridge isolated bidirectional DC–DC converter for high-frequency-link power-conversion system," IEEE Transactions on Power Electronics, vol. 29, no. 8, pp. 4091-4106, Aug. 2014.