University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

8-2023

# A Real-Time ANPC Inverter Digital Twin with Integrated Design-For-Trust

Paulo Vitor Do Amaral Custodio University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Computer Engineering Commons

#### Citation

Do Amaral Custodio, P. V. (2023). A Real-Time ANPC Inverter Digital Twin with Integrated Design-For-Trust. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/5035

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

A Real-Time ANPC Inverter Digital Twin with Integrated Design-For-Trust

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Paulo Vitor do Amaral Custodio State University of Londrina Bachelor of Science in Electrical Engineering, 2015

> August 2023 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Committee Member

Roy A. McCann, Ph.D. Committee Member Chis Farnell, Ph.D. Committee Member

### ABSTRACT

The demand for renewable energy has increased over the last few years, and so has the demand for greater expectations within the energy market. This increasing trend has been accompanied by more significant usage of internet-connected devices (IoT), leading to critical electrical infrastructure being connected to the internet. Implementing internet connectivity with such devices and systems provides benefits such as improving the system's performance, facilitating irregularity and anomaly mitigation, and providing additional situational awareness for enhanced decision-making. However, enhancing the connected system with IoT introduces a drawback – a greater vulnerability to cyber-attacks.

Cyber-attacks targeting critical infrastructure in the electrical sector have occurred in the United States and Ukraine. These cyber-attacks highlight and expose vulnerabilities that a system inherits when connecting to the internet. These attacks left thousands of customers without electricity for hours until operators could regain control of the electric utility grid.

Therefore, to address the vulnerabilities of an internet-connected power electronic device, this work focused on the hardware layer of the system. Implementing a cyber-control system inside the hardware layer can significantly reduce the possibility of an attacker patching malicious controller firmware into a photovoltaic grid-connected inverter, thus mitigating the likelihood that the inverter becomes inactive a cyber-attack scenario. With this mitigation technique, if a cyberattack is successful and an attacker gains control of the network, a cyber-defense technique is in place to mitigate the impact of the cyber-attack.

This additional protection layer was developed based on an innovative concept known as Digital Twin (DT). A DT, in this case, replicates an Active-Neutral Point Clamped (ANPC) inverter and was designed using a hardware language known as VHDL (Very High-Speed Integrated Circuit Hardware Description Language) and applied to Field-Programmable-Gate-Array (FPGA). The DT is embedded within the FPGA and contained in a controller board, the UCB (Unified Controller Board), developed by the University of Arkansas electrical engineering team. This UCB also contains two Digital Signal Processors (DSPs) responsible for generating associated signals to control an authentic physical inverter. These DSP signals are received and processed by the FPGA that implements the DT of an ANPC; in other words, it simulates in realtime the expected output of an actual ANPC inverter using the signals from the DSP.

When a new firmware is ready to be patched, the DT provides output signals simulating behavior that a real ANPC inverter would generate with the new firmware. The new firmware is tested to check if it meets all the operational requirements established using a Design-For-Trust technique (DFTr). If the new firmware fails in at least one of the DFT tests, it is considered malicious and must be rejected.

This work is divided into sections, such as Background, which explains the pieces that were used and the strategy behind this work; Process and Procedure, which explains the methodology that was adopted to prove the reliability and effectiveness of this work; Results and Discussion, where the simulations and results are described and explained; followed by Conclusion and Future work section, which concludes this work and adds possible future projects to continue this work further. ©2023 by Paulo Vitor do Amaral Custodio All Rights Reserved

#### ACKNOWLEDGEMENTS

First, I would like to thank God for giving me good health, courage, wisdom, and perseverance to follow my dreams and to be able to pursue my master's degree. Second, I want to thank my family for their support and guidance and for always believing in myself and pushing me forward. I would also like to thank my wife, Ana Paula Garcia, who always stood by my side and gave me all the support I needed. I am also very grateful for the opportunity to work with Dr. H. Alan Mantooth, Dr. Chris Farnell, and Dr. Le-Vasicek. Without them, this project would not exist, and the knowledge and the experiences they provided to me during this time we worked together are unforgettable and priceless. Lastly, I would like to especially thank Brady McBride and Justin Jackson for all their support and knowledge during the creation of this work, their help and partnership made my master's degree journey much lighter and exciting.

| CHAPTER 1                                                  | 1  |

|------------------------------------------------------------|----|

| INTRODUCTION                                               | 1  |

| CHAPTER 2                                                  |    |

| BACKGROUND                                                 |    |

| 2.1 Cyber-Attacks                                          |    |

| 2.2 Photovoltaic Systems                                   | 6  |

| 2.3 ANPC INVERTER                                          | 7  |

| 2.4 MODULATION                                             |    |

| 2.4.1 Modulation: 3-level ANPC Inverter                    |    |

| 2.5 CONTROLLER BOARD AND ARCHITECTURE                      | 17 |

| 2.5.1 Field-Programmable-Gate-Array (FPGA)                 |    |

| 2.5.2 Digital Signal Processor (DSP)                       |    |

| 2.5.3 Serial Peripheral Interface Flash Memory (SPI Flash) |    |

| 2.5.3.1 Flash Memory                                       |    |

| 2.5.3.2 SPI Protocol                                       |    |

| 2.6 DIGITAL TWIN                                           |    |

| 2.7 Design-For-Trust                                       |    |

| 2.7.1 Short-Circuit                                        |    |

| 2.7.2 Deadtime                                             |    |

| 2.7.3 Fundamental Frequency                                |    |

| 2.7.4 Fast Frequency                                       |    |

# TABLE OF CONTENTS

| 2.7.5 Watchdog (Timer)                                                    | . 36 |

|---------------------------------------------------------------------------|------|

| CHAPTER 3                                                                 | . 37 |

| METHODOLOGY                                                               | . 37 |

| 3.1 PROCESSES                                                             | . 38 |

| 3.1.1 EXTERNAL PROCESSES                                                  | . 38 |

| 3.1.2 INTERNAL PROCESSES                                                  | . 48 |

| CHAPTER 4                                                                 | . 60 |

| RESULTS AND DISCUSSION                                                    | . 60 |

| 4.1 Standard Firmware (Non-malicious)                                     | . 60 |

| 4.2 Short-circuit corrupted Firmware (Malicious)                          | . 63 |

| 4.3 FIRMWARE WITH MISSING DEADTIME (MALICIOUS)                            | . 65 |

| 4.4 FIRMWARE WITH A FUNDAMENTAL FREQUENCY DIFFERENT THAN 60Hz (MALICIOUS) | . 67 |

| 4.5 FAST FREQUENCY NOT MATCHING 42 KHZ FIRMWARE (MALICIOUS)               | . 69 |

| 4.6 Stall state firmware (Malicious)                                      | . 72 |

| 4.7 Cost Analysis                                                         | . 74 |

| CHAPTER 5                                                                 | . 77 |

| CONCLUSIONS AND FUTURE WORK                                               | . 77 |

| REFERENCES                                                                | . 79 |

| APPENDICES                                                                | . 84 |

| APPENDIX A: VHDL CODE                                                     | . 84 |

| A-1: Top file                                                             | . 84 |

| A-2: Firmware Validation      | 142 |

|-------------------------------|-----|

| A-3: Short-circuit            | 211 |

| A-4: Deadtime                 | 223 |

| A-5: Fast Frequency           | 235 |

| A-6: Fundamental Frequency    | 246 |

| A-7: Watchdog                 | 258 |

| A-8: Emulation (Digital Twin) | 266 |

# LIST OF FIGURES

| Fig. 1 Cyber-physical layer representation [2].                                    | 5 |

|------------------------------------------------------------------------------------|---|

| Fig. 2. Solar Power Plant [10]                                                     | б |

| Fig. 3. Typical representation of a 3-level ANPC inverter hardware                 | 7 |

| Fig. 4. Inverters: (a) NPC; (b) ANPC                                               | 8 |

| Fig. 5. Three-level ANPC inverter topology                                         | 9 |

| Fig. 6. Pulse Width Modulation [16]1                                               | 1 |

| Fig. 7. SPWM generation principle1                                                 | 1 |

| Fig. 8. Ideal PWM inverter output voltage [17]12                                   | 2 |

| Fig. 9. Gate signals for modulation type II [12]12                                 | 3 |

| Fig. 10. Phase leg of a three-level ANPC inverter topology [2]                     | 4 |

| Fig. 11. Switching states: (a) P state, (b) O+ state, (c) O- state, (d) N state 1: | 5 |

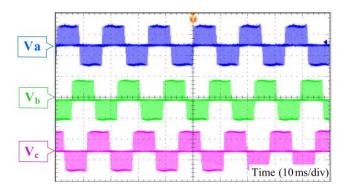

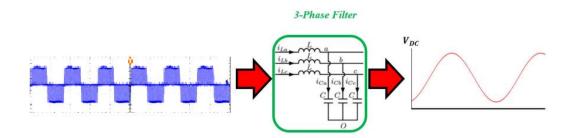

| Fig. 12. Inverter voltage output waveforms [12] 10                                 | б |

| Fig. 13. Filtered Inverter Voltage Output                                          | б |

| Fig. 14. Block diagram of UCB architecture showing significant components [2]      | 8 |

| Fig. 15. UCB with auxiliary daughter boards installed [2]19                        | 9 |

| Fig. 16. Internal architecture of a typical FPGA [18]                              | 1 |

| Fig. 17. DSP Block diagram                                                         | 3 |

| Fig. 18. SPI Connection [21]                                                       | б |

| Fig. 19. MT25Q128ABA [23]                                                          | 7 |

| Fig. 20. SPI Flash reading procedure [23]                                          | 8 |

| Fig. 21. Hardware Architecture (DSP1 as active)                                    | 1 |

| Fig. 22. DSP2 as active                                                            | 2 |

| Fig. 23. Short Circuit scenario [2]                        |    |

|------------------------------------------------------------|----|

| Fig. 24. Dead Time                                         |    |

| Fig. 25. LabVIEW interface                                 |    |

| Fig. 26. CCS IDE                                           |    |

| Fig. 27. Example of a Hex File (firmware)                  |    |

| Fig. 28. USB cable connection                              |    |

| Fig. 29. LabVIEW project                                   |    |

| Fig. 30. Loading Firmware                                  | 44 |

| Fig. 31. Hot-Patch Ready                                   |    |

| Fig. 32. Generate Digital Twin output.                     |    |

| Fig. 33. Possible errors                                   | 47 |

| Fig. 34. Backup FW: Drop-down menu                         |    |

| Fig. 35. Asynchronous Hot-Patch [4]                        | 56 |

| Fig. 36. Synchronous Hot-Patch [4]                         | 56 |

| Fig. 37. DSP Standard Firmware                             | 61 |

| Fig. 38. Three-Level ANPC Inverter Digital Twin            | 63 |

| Fig. 39. Channel 0 and 3 on simultaneously                 | 64 |

| Fig. 40. Short-Circuit scenario detected.                  | 65 |

| Fig. 41. DSP firmware without deadtime                     | 66 |

| Fig. 42. Missing deadtime detected.                        | 67 |

| Fig. 43. DSP firmware with a fundamental frequency of 30Hz | 68 |

| Fig. 44. Fundamental Frequency different than 60 Hz        | 69 |

| Fig. 45. DSP firmware with a fast frequency of 42 kHz      | 71 |

| Fig. 46. Fast Frequency different than 42 kHz | 72 |

|-----------------------------------------------|----|

| Fig. 47. Stall Firmware                       | 73 |

| Fig. 48. Timer Error                          | 73 |

| Fig. 49. MachXO2 Price [32]                   | 74 |

| Fig. 50. DSP controlCard Price [32]           | 75 |

| Fig. 51. FPGA Intel Altera [23]               | 75 |

| Fig. 52. FPGA Intel Altera [32]               | 76 |

# LIST OF TABLES

| Table 1. Switch states modulation type II [12]      | , 14 |

|-----------------------------------------------------|------|

| Table 2. Correlation SPI - MT25Q128ABA              | . 27 |

| Table 3. Correlation between DSP and FPGA GPIOs     | . 40 |

| Table 4. Firmware Register Map                      | . 49 |

| Table 5. Backup Firmware Register Map               | . 50 |

| Table 6. Digital Twin ANPC Output                   | . 58 |

| Table 7. Digital Twin Registers                     | . 59 |

| Table 8. Transistor/Channel relation                | . 62 |

| Table 9. Fast transistors and channels relationship | . 70 |

# LIST OF ABBREVIATIONS

| AC               | Alternative Current           |

|------------------|-------------------------------|

| CFM              | Configuration Flash Memory    |

| CLBs             | Configurable Logic Blocks     |

| DFTr             | Design-For-Trust              |

| DNS              | Domain Name System            |

| DC               | Direct Current                |

| DER              | Distributed Energy Resource   |

| DoS              | Denial-of-Service             |

| DSP              | Digital Signal Processor      |

| DT               | Digital Twin                  |

| EBR              | Embedded Block RAM            |

| FFs              | Flip-Flops                    |

| FPGA             | Field-Programmable-Gate-Array |

| GUI              | Graphic User Interface        |

| IEA              | International Energy Agency   |

| IoT              | Internet-of-Things            |

| I <sup>2</sup> C | Inter-Integrated Circuit      |

| JTAG             | Joint Test Action Group       |

| LUT              | Look-up table                 |

| MitM             | Man-in-the-Middle             |

| MUX              | Multiplexer                   |

NERC North American Electric Reliability Corporation

- NVM Non-volatile Memory

- NPC Neutral Point Clamped

- PFUs Programmable Function Units

- PLL Phase Lock Loop

- PV Photovoltaic

- PWM Pulse Width Modulation

- RAM Random Access Memory

- SRAM Static random-access memory

- SPWM Sinusoidal Pulse Width Modulation

- SPI Serial Peripheral Interface

- UART Universal Asynchronous Receiver and Transmitter

- UCB Unified Controller Board

- UI User Interface

- VHDL Very High-Speed Integrated Circuit Hardware Description Language

#### CHAPTER 1

#### INTRODUCTION

Advances in technology have led to significant improvements in computing power while reducing overall device size and increasing availability and speed of communication. These developments have led to a dramatic increase in internet-connected devices, including IoTs. While IoTs offer many benefits, such as increased situational awareness, they also create new vulnerabilities for cyber-attacks to exploit.

In 2015, Ukraine experienced a significant power outage when a cyber-attack resulted in the disconnection of twenty-three 35kV and seven 110kV substations for three hours. The attack was initiated using a phishing technique and resulted in power loss for 225,000 customers. Similarly, in 2016, part of the capital city of Ukraine, Kyiv, was left without electricity for over an hour due to a cyber-attack [1].

In response to these emerging threats, in 2017, the US president signed a bill to increase the cybersecurity of federal networks and critical infrastructure. This order highlighted the risks of "electricity disruption" caused by cyber-attacks. It is essential to address these risks and intensify efforts to improve cybersecurity and protect against cyber-attacks capable of causing significant disruption to critical infrastructure [2].

In addition, according to the International Energy Agency (IEA), the potential to produce energy via renewable technologies, such as wind and solar power, is expected to increase around 60% of the renewable electricity capacity by 2026, making renewables the primary source responsible for almost 95% of this increase, with more than half coming from solar photovoltaic (PV) by itself, consequently becoming "the powerhouse of growth in renewable electricity" [3].

1

Therefore, this work applied the modern idea of utilizing Digital Twin to lessen the vulnerabilities of internet-connected devices in light of the growing need for renewable energy and the rising application of internet-connected devices. As [4] presented a cyber protection system for grid-connected devices using embedded systems, this work proposed an improvement to the hardware layer of the cyber-physical devices - creating a Digital Twin of an ANPC inverter within a custom controller, which was the same controller used in [4].

The controller contains a Field Programmable Gate-Array (FPGA), which emulates a 3level ANPC inverter, instead of a 2-level inverter, as was cited in [4]. Additionally, it has two Digital Signal Processors (DSPs): one is used to control an actual inverter – called "Active DSP"; while the other is used to create a Digital Twin and authenticate a new firmware before patching it – called "Stand By DSP." In this case, the authentication method is called Design-For-Trust (DFTr). The purpose of utilizing this technique is to prevent malicious firmware from being installed or updated inside grid-connected inverters used within solar distributed energy resources (DERs). Such malicious firmware can potentially carry out a cyber-physical attack on the DERs, which can have serious consequences, such as shutting the grid down. DFTr ensures that the firmware installed on these inverters is trustworthy and free of malicious code, thereby reducing the risk of cyber-physical attacks.

### **CHAPTER 2**

#### BACKGROUND

### 2.1 Cyber-Attacks

Cyberattacks usually concentrate on revealing the weaknesses of the communications layer. Cyber attackers connect to the network using a variety of techniques, including phishing, Man-in-the-Middle (MitM) attacks, Denial of Service (DoS), SQL injection, Domain Name System (DNS) tunneling, and more, to obtain access to the communication layer. Attackers that take over the communications section can send the controller malicious commands or software, which could damage the power electronic device [4]. Several cybersecurity techniques are specific to the grid for determining the primary forms of attack vectors and performing risk evaluations. Since the communications layer is the first point of interaction with the system, most cybersecurity techniques concentrate on protecting it. However, new system vulnerabilities are continually being found, raising serious concerns about the grid's dependability [5].

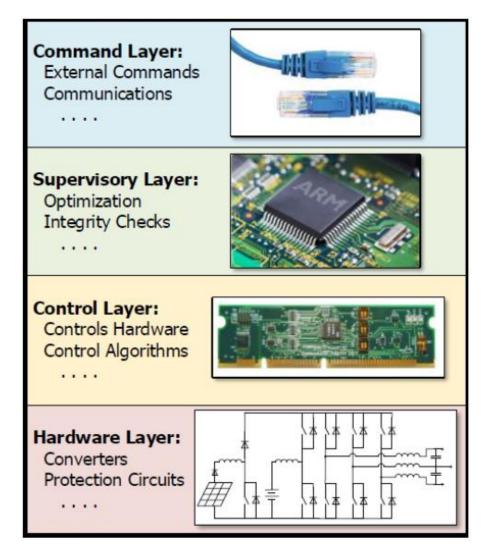

Grid vulnerabilities are a serious threat because they allow cyberattacks to take down the power grid in an entire nation or city, as was the case with Ukraine strikes in 2015 and 2016 [6]. Recently, a ransomware attack shut down pipeline operations on the Colonial Pipeline in the southeast of the United States [7]. Ransomware programs have caused several cyberattacks that shut down physical activities in 2020, as discussed in [7], highlighting the significant need for cybersecurity. Cybersecurity must now be incorporated into the design of power electronics control systems to decrease the electric grid's vulnerability to cyberattacks that target the communication network [4]. If an attacker successfully takes control of the communications layer, they can manipulate the controller, hardware layer, and other layers. Fig. 1 below displays a graphical depiction of these layers.

For example, when malicious firmware is uploaded to the controller, it might force the grid-connected device to shut down or start operating with suboptimal settings. This attack might not shut down the entire grid but a portion of it, similar to what happened during the attacks targeting Ukraine in 2015 and 2016. This work presents a technique for further protecting grid-connected devices that use the Supervisory, Control, and Hardware layers.

This project was designed to address a scenario where an attacker had already taken control of the network. The objective was to enhance the security of the power electronics controller in order to safeguard the grid operation. In case of an attack, a compromised controller would issue a command to shut down the system. The suggested method does not allow unauthorized firmware updates that could compromise the controller board. Moreover, a validated backup firmware replaces the compromised firmware without disrupting the ongoing system control. This technique ensures that the system will not crash during an attack, enhancing its resilience and security.

Fig. 1 Cyber-physical layer representation [2].

2.2 Photovoltaic Systems

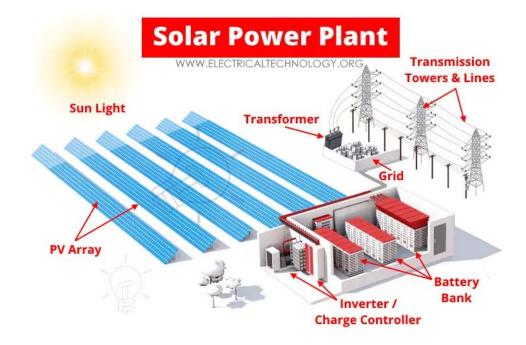

The conversion process of light (photons) into electricity (voltage) is known as the photovoltaic effect. This effect gives the field of photovoltaics (often abbreviated as PV) its name. The significance of this effect was first demonstrated in 1954 by researchers at Bell Laboratories, who built a silicon solar cell capable of generating electric current upon exposure to light. Since then, the development of photovoltaic systems has progressed significantly. Due to their increasing economic viability, they are now widely installed and used on a large scale to help power electric grids [8].

In transmission and distribution networks, almost all power is provided as alternating current (AC), while the photovoltaic cells produce Direct Current (DC), the same type of current provided by batteries. To connect solar-power systems to the grid, inverters, and other components, shown in Fig. 2, necessary to connect a solar power plant to the grid, are utilized to convert DC to AC power [9].

Fig. 2. Solar Power Plant [10]

### 2.3 ANPC Inverter

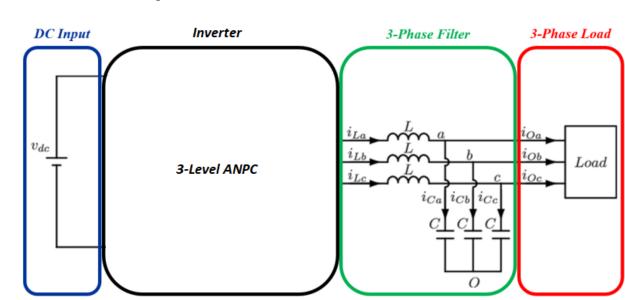

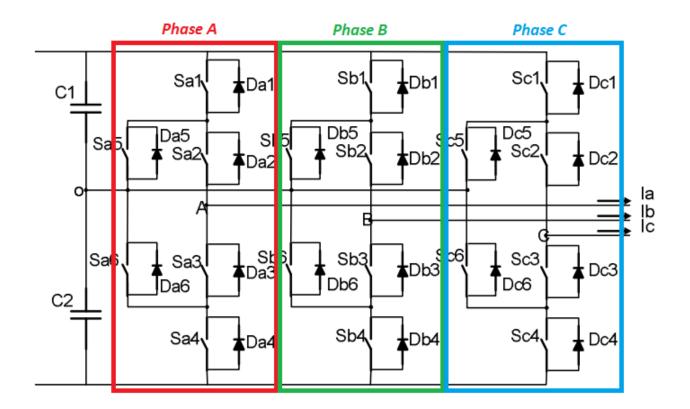

Neutral-point-clamped (NPC), capacitor-clamped, and cascaded H-bridge inverters are just a few examples of inverters commonly used in PV systems [11]. These power converters, known as inverters, take a DC link supply as input. Using Pulse Width Modulation (PWM) signals, it controls its output to generate a three-phase sinusoidal AC with each phase offset by 120 degrees from the other. The whole system is depicted in Fig. 3 as having four sections:

- DC input voltage supply: Representing PV arrays from Fig. 2.

- An inverter: Considering a 3-level ANPC inverter in this case.

- A three-phase filter.

• Three-phase load.

Fig. 3. Typical representation of a 3-level ANPC inverter hardware

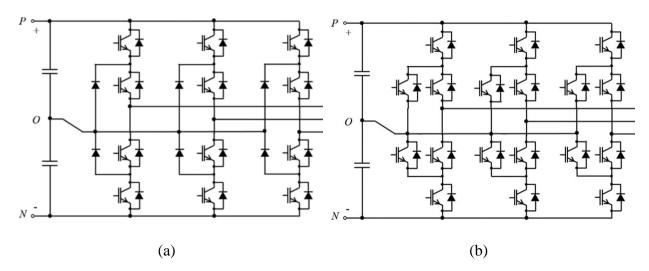

The NPC inverter design can handle higher voltage levels using semiconductor components with lower voltage ratings while generating fewer harmonics in its output, and it is appealing for use in high-power applications. The semiconductor devices used in this inverter architecture have a rating of half the input DC bus voltage. Although, the unbalanced loss distribution across its semiconductor components is a drawback of the NPC inverter [12] [11].

Conversely, this drawback is resolved by the ANPC inverter design. Due to the two redundant neutral current pathways in this architecture, semiconductor device losses may be balanced regardless of the load power factor [13], [14]. Additionally, it needs low voltage-rated semiconductor components for high voltage applications, just like the three-level neutral-point clamped inverter structure. As a result, it is a highly appealing option for applications requiring high-power energy conversion [12] [11].

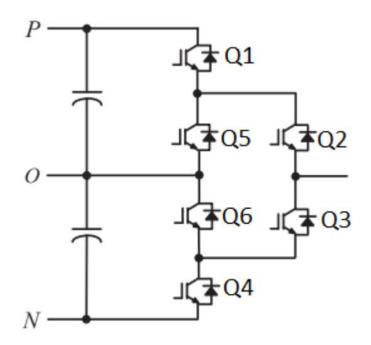

The NPC design (Fig. 4a) involves twelve switches (four for each phase) and six clamping diodes (two for each phase), while the ANPC design uses 18 switches, with six switches for each phase, as Fig. 5 illustrates. With these six transistors, it became possible to manipulate more switches involved in the design, increasing the number of possible modulation strategies that could be used to enhance the ANPC performance, as presented in work [12].

Fig. 4. Inverters: (a) NPC; (b) ANPC

Fig. 5. Three-level ANPC inverter topology

This project is centered on implementing a Digital Twin of an ANPC (Active Neutral Point Clamped) inverter, as this inverter type was incorporated with the controller of a solar farm during testing. In light of the growing significance of photovoltaic energy in the renewable energy sector, three-level inverter topologies have gained prominence over two-level inverters, owing to their distinct advantages, such as lowered switching loss, diminished electromagnetic interference, and reduced harmonic content in the output current waveform. These benefits are characteristic of three-level inverter topologies, setting them apart from their two-level counterparts [12].

### 2.4 Modulation

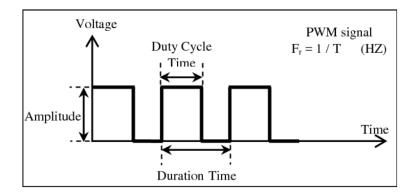

Pulse-width modulation (PWM) is a crucial component of power electronic converters that was initially proposed to facilitate the production of sinusoidal AC voltage and current by inverters. Despite being suggested over 60 years ago, in 1964, PWM continues to be widely used with the rise of advanced power electronic converters and growing requirements for superior output voltage and current. PWM remains a significant subject of exploration in the realm of power electronics, captivating the curiosity and enthusiasm of researchers and scholars. The ongoing interest in PWM reflects its continued relevance and importance in enabling the efficient and effective use of power electronic converters in a range of applications [15].

The effectiveness and reliability of the inverter can be affected immediately by the switching frequency of the PWM technique. Increasing the switching frequency can lead to a lower distortion rate in the inverter's AC output current, as well as a decrease in the size and capacity of the filter inductor and capacitor. However, increasing the switching frequency also results in higher switching losses and greater performance demands on the switching device [15].

In order to maintain the output voltage of the single-phase inverter at a specific level, it is necessary to apply a control signal that will activate the inverter switches, and a PWM is commonly used for this purpose (Fig. 6). PWM signals have two main variables:

- Duty-Cycle: Also known as "On time," it is the length for which the switch is in operation (On).

- Switching period: sum of the on-time and the off-time duration time.

Fig. 6. Pulse Width Modulation [16]

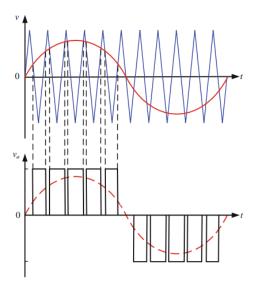

The PWM generation is frequently based on comparing a low-frequency sine wave signal to a high-frequency carrier signal, which is usually a triangular method known as SPWM (Sinusoidal Pulse-Width Modulation). The fundamental concept behind natural sampling SPWM involves the comparison of a sinusoidal modulating voltage with a high-frequency triangular carrier wave. This comparison generates a rectangular pulse sequence whose width follows the sinusoidal law, as represented by Fig. 7 It is then power amplified and used to drive the inverter, ultimately producing a sinusoidal voltage or current output. [15].

Fig. 7. SPWM generation principle

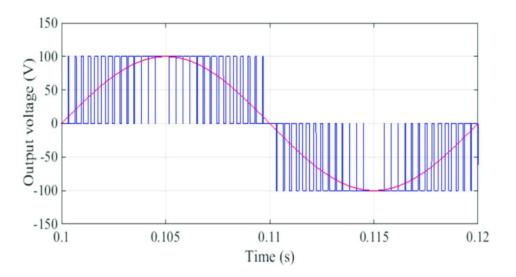

The voltage output of an unfiltered single-phase inverter is half of the DC input voltage during the on-time. However, the filtered output voltage is limited to a certain percentage of the DC input voltage. As the on-time approaches the maximum limit of 100%, the filtered output voltage increases proportionally. When the on-time is 100%, the filtered output voltage equals 50% of the DC input voltage, equivalent to half of the DC input voltage. The same line of principle is applied to the negative side, generating an output voltage as a sinusoidal waveform, which symbolizes an AC output, by raising and lowering the on-time, as Fig. 8 portrayed.

Fig. 8. Ideal PWM inverter output voltage [17]

#### 2.4.1 Modulation: 3-level ANPC Inverter

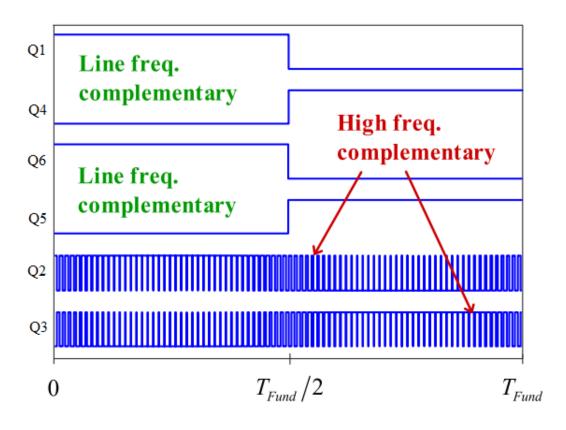

A three-level ANPC inverter possesses eighteen transistors, allowing several strategies to improve the inverter's performance using different transistor types or modulation, as proposed in [12]. As this work was put into practice, an authentic ANPC inverter provided by SMA was used. As another group chose the modulation in the same project, modulation type two was selected from [12], where the external switching devices (Q2 and Q3) commutate at the carrier frequency.

In contrast, the inner transistors commutate at the US's fundamental line frequency - 60 Hz – as presented in Fig. 9.

Fig. 9. Gate signals for modulation type II [12]

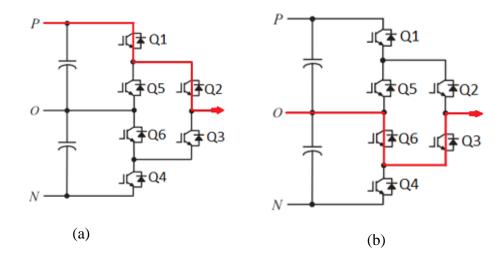

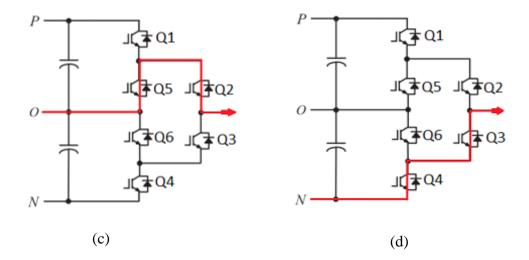

In order to simplify the explanation of how the ANPC inverter works, Fig. 10 illustrates one phase leg of the inverter. Each transistor can be considered a switch that can be turned on and off, and depending on the state of each switch, the output might change. Considering non-malicious states only, Table 1 represents each transistor's possible output and states, where Vdc is the DC input from the system (Fig. 3), while Fig. 11 illustrates the current path on each of these states.

Fig. 10. Phase leg of a three-level ANPC inverter topology [2]

| State          | Output  | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 |

|----------------|---------|----|----|----|----|----|----|

| Р              | 0.5Vdc  | 1  | 1  | 0  | 0  | 0  | 1  |

| O <sup>+</sup> | 0       | 1  | 0  | 1  | 0  | 0  | 1  |

| 0-             | 0       | 0  | 1  | 0  | 1  | 1  | 0  |

| N              | -0.5Vdc | 0  | 0  | 1  | 1  | 1  | 0  |

Table 1. Switch states modulation type II [12]

Fig. 11. Switching states: (a) P state, (b) O+ state, (c) O- state, (d) N state

During the P state, transistors Q1 and Q2 are turned on, allowing the positive half of the DC input voltage to reach the output, generating  $\frac{Vdc}{2}$  Volts on the output Fig. 11(a). Meanwhile, the O+ state, a zero state during the positive cycle, involves turning the transistors Q6 and Q3 On, allowing the zero voltage to reach the output Fig. 11(b). In the next state O-, represented by Fig. 11(c), the transistors Q2 and Q5 are on, allowing the zero voltage to reach the output. Lastly, the N state, illustrated in Fig. 11(d), affects the output when transistors Q3 and Q4 are turned on,

creating a path for the negative half of the DC input to influence the output, generating  $\frac{-Vdc}{2}$  Volts. The inverter's output voltage is shown in Fig. 12, where the on-time fluctuates. This voltage output goes through a filter and gives it a sinusoidal form, as presented in Fig. 13.

This sinusoidal output is produced by fluctuating on time with the constant filter settings. The output voltage increases as the on-time increases and lowers as the on-time decreases. Switch Q6 is set ON in the "P" state to ensure that Q3 and Q4 share the same amount of voltage, while switch Q5 is switched ON in the "N" state to ensure that Q1 and Q2 share the same amount of voltage [13]. Table 1 shows that Q1 and Q6 are linked because they share the same position for each state, and the same applies to Q4 and Q5.

Fig. 12. Inverter voltage output waveforms [12]

Fig. 13. Filtered Inverter Voltage Output

### 2.5 Controller board and architecture

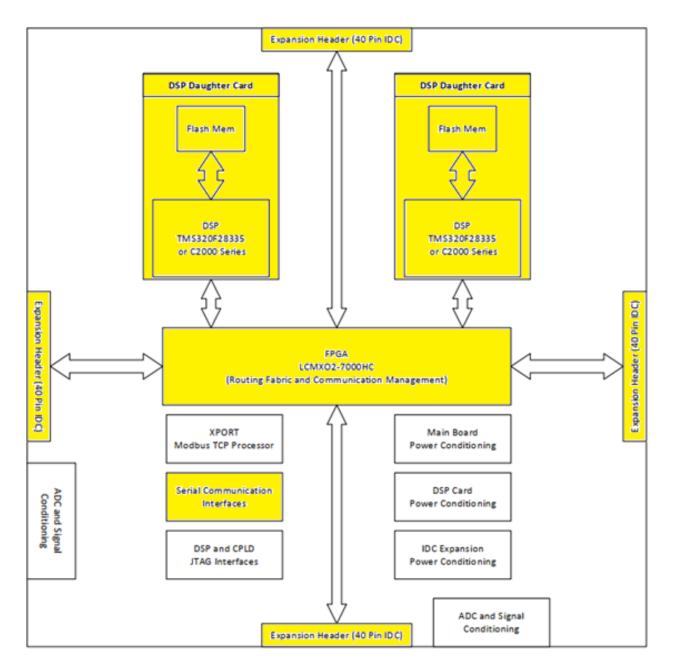

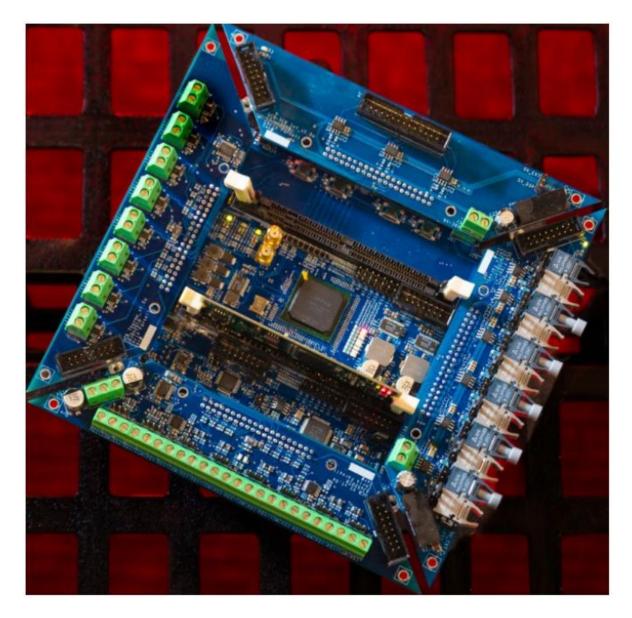

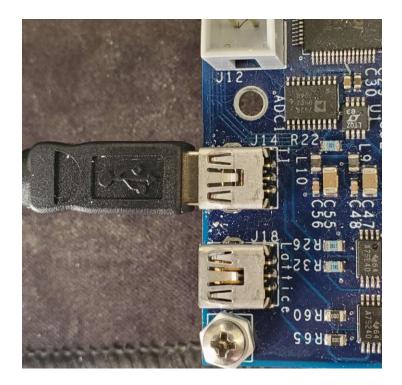

The work described in [4] used a controller called UCB (Unified Controller Board), which contains two DSPs, one FPGA, one Xport gate, four expansion headers, a JTAG interface, IDC expansions, and ADC signal conditioners, as illustrated in Fig. 15. As this work is a continuation of the work developed in [4], so the same controller board was used.

The highlighted components displayed in Fig. 15 played a crucial role in the design of this project. The expansion headers were utilized primarily to establish a connection between the controller and the SMA inverter while providing a pathway to connect other peripheral components to the controller, which will be elaborated on in further detail in this work. The DSPs and FPGA were extensively integrated into the project since it was primarily developed in VHDL and embedded within the FPGA. Communication between these components relied on the Modbus RTU protocol, designed by the University of Arkansas and implemented using VHDL. Additionally, the Serial Communication Interface (SCI) was heavily utilized to facilitate communication between the FPGA and a computer. A picture of the physical board is presented in Fig. 15.

Although not depicted in Fig. 14, the external SPI Flash was another critical component. As the development progressed, the FPGA firmware grew to a point where the internal Flash memory within the FPGA was insufficient to store the FPGA firmware and the DSP firmware, which was initially stored in the same Flash memory. To overcome this issue, an external board with an SPI Flash chip was added as a solution, so the DSP firmware could be stored apart from the FPGA firmware. Micron's Micron Serial NOR Flash Memory was used for this project.

Fig. 14. Block diagram of UCB architecture showing significant components [2]

Fig. 15. UCB with auxiliary daughter boards installed [2]

## 2.5.1 Field-Programmable-Gate-Array (FPGA)

An array of configurable logic gates makes up a Field-Programmable Gate Array (FPGA), which may be programmed internally using either a special Joint Test Action Group (JTAG) or another type of serial/parallel non-volatile memory. Static random-access memory (SRAM), a volatile memory type where, once the board is shut down, the data stored in an FPGA's memory is erased, is widely used in the FPGA architecture, and an external non-volatile memory (EEPROM) is connected to the FPGA in order to configure the data.

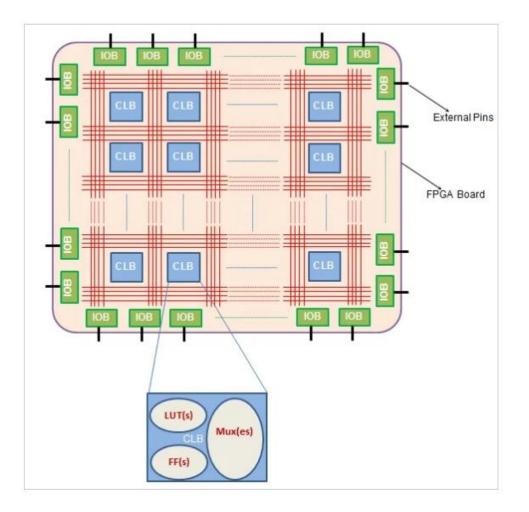

The FPGA Architecture allows for the implementation of any design of digital hardware circuit, and it is based on three distinguished elements:

- Configurable Logic Blocks (CLBs): The CLBs are the blue boxes represented in Fig. 16. Each of these blocks consists of a large number of look-up tables (LUTs), multiplexers (MUXs), and Flip-Flops (FFs), as they can be used to implement logic functions.

- Input/Output Blocks (IOBs): Are external connection resources near the FPGA's edge. These programmable blocks carry signals "to" or "from" an FPGA device. IOBs are depicted in Fig. 16 as rectangular boxes bounded by the FPGA.

- Switch Matrix: A configuration of linking wires inside an FPGA that provides low-impedance and low-delay dedicated pathways for the CLBs.

The Lattice MachX02-7000HC FPGA device used in this project can be programmed using the IDE provided by Lattice named "Lattice Diamond." This FPGA includes an embedded clock system providing a frequency not higher than 400MHz, including a Phase Lock Loop (PLL) that provides alternative frequency domains for different designs. It also includes Configuration Flash Memory, or CFM, where the developed firmware is stored, Embedded Block RAM (EBR), a component that can be used to store parameters, was used to store some variable's values, I/O banks, Programmable Function Units (PFUs) that contains 6864 Look-Up-Tables (LUTs) are used in the design and have a voltage core of 2.5-3.3V.

Fig. 16. Internal architecture of a typical FPGA [18]

For external communication, the FPGA can communicate through Inter-Integrated Circuit (I<sup>2</sup>C), Serial Peripheral Interface (SPI), and Universal Asynchronous Receiver and Transmitter (UART) protocols. In this design, the SPI communicated between the FPGA and an external Flash memory to increment the controller's memory capacity. At the same time, the UART was crucial to connect the board with the User Interface (UI) during development and testing. More information about the MachX02 can be found in [19].

### 2.5.2 Digital Signal Processor (DSP)

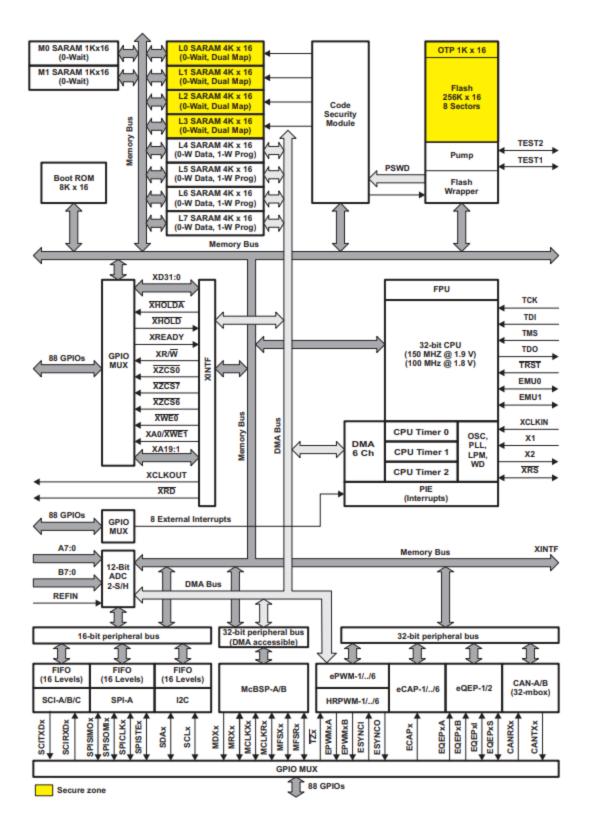

It is common to employ DSPs in regulating power inverters that transform DC power derived from solar panels or batteries into AC power suitable for utilization in electrical systems. DSPs can be used to execute complicated control algorithms that govern inverter voltage, frequency, and power production and monitor and fix problems. For this project, DSPs were utilized to generate the PWM signals.

PWM is a crucial feature of DSPs in inverter management. PWM is a method for controlling an inverter's output voltage by changing the width of its output pulses, in this case, to control the ANPC inverter output. The average voltage can be changed over time by changing the pulse width, providing precise output voltage control. The PWM impulses can be generated in real-time using DSP, allowing for fast and precise changes to working circumstances.

The PWM was generated based on the previously explained method of natural sampling SPWM, which compares a triangle carrier wave, and a sinusoidal modulating voltage with a fundamental frequency, ensuring the carrier has a much higher frequency than the fundamental. Then, a rectangular pulse sequence that varies its width is produced, and the pulse sequence drives the inverter to provide a sinusoidal voltage or current output, as presented in Fig. 7.

The two DSP cards utilized within the controller, model Delfino F28335, manufactured by Texas Instruments, use Code Composer Studio (CCS) as an interface to communicate and control the devices. This DSP was chosen due to its capabilities. As a C2000 real-time microcontroller, it was designed to increase closed-loop performance and was specifically manufactured for use in real-time control applications, such as solar inverters [20]. Fig. 17 represents the F28335 schematic.

22

Fig. 17. DSP Block diagram

2.5.3 Serial Peripheral Interface Flash Memory (SPI Flash)

### 2.5.3.1 Flash Memory

One of the main differences between a volatile memory, like Random Access Memory (RAM), and a non-volatile memory (NVM) is that in a volatile memory, the data stored in it is lost when the power is switched off. However, in a non-volatile memory such as Flash Memory, this limitation does not occur. The Flash memory can retain the data through multiple power cycles, which means the program stored in the Flash is not lost even when switched off [21].

The Flash memory was since, during the firmware loading process, the FPGA needs to access the DSP firmware when the user requests. In addition, as it also needs to keep a genuinely known firmware as a backup, the controller must not lose the DSP firmware in case the system is turned off.

The memory component used as a solution to the lack of internal memory in the FPGA was the MT25QL128ABA manufactured by Micron. This chip was selected due to its memory size, 128Mb, its voltage application -2.7 to 3.6V – and its versatility to read and program it with ease.

#### 2.5.3.2 SPI Protocol

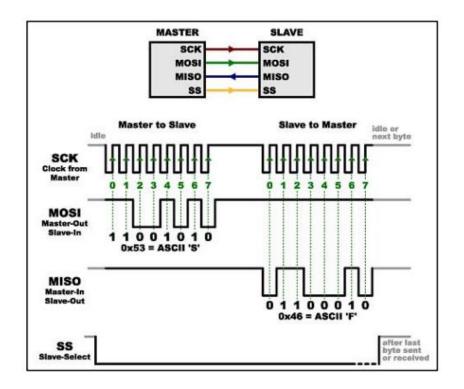

The communication within the Flash Memory is made through a protocol named Serial Peripheral Interface, or SPI. It is a widely used synchronous serial communication protocol developed by Motorola in the mid-1980s to facilitate data transfer between various electronic components [22]. This protocol uses a four-wire interface consisting of a clock line, a master-out-slave-in (MOSI) line, a master-in-slave-out (MISO) line, and a slave select (SS) line, as depicted in Fig. 18.

SPI utilizes a master-slave architecture, meaning it has one device (the master) that controls the communication and one or more devices (the slaves) that respond to the master's commands. This structure provides a straightforward and efficient method of communication between devices. It allows for full-duplex communication, meaning the master and slave devices can transmit and receive data simultaneously [22].

The SPI protocol employs two lines, one for transmitting data and the other for synchronization via clock pulses. Whenever the receiver detects a clock edge, it reads the bit from the data line. The entity that generates the clock signal is called the "master," while the other party is known as the "slave." Typically, there is only one master, which in this case was the FPGA, but there may be one or more slaves. To send data from the master to a slave, the master sends bits through the MOSI line, and the MISO is used by the slave to return the response. When multiple slaves are present, the SS line chooses the intended one and signals the slave to prepare for receiving or sending data. The SS line is usually held high, severs the slave's connection to the SPI bus [21].

For example, in Fig. 18, the master sends a binary command "01010011", which corresponds to "53" in hexadecimal format. After a while, the slave replies to the master with a binary message "01000110", which correlates to "46" in hexadecimal. It is important to note that the SS is low during the entire communication process between the master and slave because that is the method the master uses to select the slave with whom it will communicate.

SPI can achieve high-speed data transfer rates of up to 400 Mbps, making it an ideal choice for applications that require fast and reliable communication between devices, such as sensors, displays, and memory chips. Additionally, SPI is commonly used in embedded systems and microcontroller-based projects because of its simplicity and low hardware requirements [22].

25

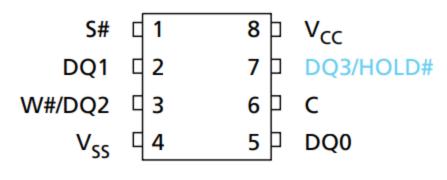

Fig. 18. SPI Connection [21]

Fig. 19 depicts the MT25Q128ABA pinout. The nomenclature provided earlier in the SPI protocol does not appear in this picture. However, the manufacturer provides the correlation in the component's datasheet, where the S# is the slave-select, also known as Chip Select, the C pin is the clock input, DQ0 is the input MOSI, DQ1 is the output MISO, Vcc is the power supply, and Vss is the ground [23]. Table 2 presents the correlation between the SPI protocol and the SPI Flash chip used in this work. The W# and DQ3/HOLD were not used in this work; they are extra protection pulled high to disable them.

Fig. 19. MT25Q128ABA [23]

Table 2. Correlation SPI - MT25Q128ABA

| SPI  | MT25Q128ABA |

|------|-------------|

| MOSI | DQ0         |

| MISO | DQ1         |

| SS   | S#          |

| SCLK | С           |

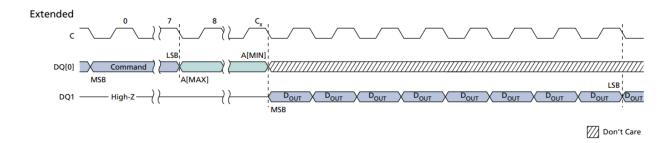

An example of when the FPGA needs to read data from the SPI Flash, it must send the read command – "03" in hexadecimal – followed by the register address where the data is stored. As presented in Fig. 20, the command takes eight clock cycles, 0 to 7, since "03" in hex would be "0000 0011" in binary, and each bit takes one clock to be read. After sending the desired register, the slave, which is the flash memory itself, replies to the master with the data that was stored at that address. LSB and MSB presented in the pictures stand for Least Significant Bit and Most Significant Bit, respectively.

Fig. 20. SPI Flash reading procedure [23]

A VHDL-based method was developed to extract data from the MT25Q128ABA, essential to store the DSP firmware externally from the FPGA. The reason for this was that the MachXO2 device had limited resources, and it was no longer feasible to store the firmware within the FPGA memory. As the project progressed, the FPGA firmware size grew to a point where the internal Flash memory was inadequate to contain both the FPGA and DSP firmware.

## 2.6 Digital Twin

The Digital Twin (DT) was initially introduced by Professor Grieves at the University of Michigan in 2003 while teaching a product life cycle management course. Grieves defined DT as a virtual information structure representing a manufactured product [5]. He proposed that a DT model should have three dimensions: a physical entity, a virtual entity, and an interconnection between them [6].

In their research on the prediction of complex product/system behaviors through Digital Twins, Grieves highlighted the importance of using simulation predictions to minimize the complexity of such products/systems. The ultimate goal is to prevent unforeseen and unfavorable outcomes that could result in disastrous consequences. For instance, when launching a rocket, a virtual space is created to simulate the Digital Twin of an actual rocket. The Digital Twin allows

for quick replacements and repairs in the event of failure, reducing the risk of catastrophic problems [24].

This technology is considered the leading force in changing the norms of aviation manufacturing in the years to come [25]. This technology is causing significant disruption in various industries by utilizing data feeds to map physical entities. The German Information Technology and New Media Association BITKOM predicts the manufacturing market will see immense value in digital twins, with estimates surpassing 78 billion euros by 2025. In 2016 and 2017, Gartner – a 5+ billion-dollar company that provides insights and guidance to other businesses - recognized DT as one of the top ten strategic technology development trends. In November 2017, the largest weapons manufacturer globally, Lockheed Martin, identified DT as one of the top six technologies in the future defense and aerospace industry [26].

Furthermore, according to [27], applying DT in automated industries is vital. They refer to the comprehensive simulations used to create a virtual replica of a physical system. By embracing digital twins, operators can oversee production, analyze deviations in a controlled virtual setting, and enhance the safety of process industries.

However, the meaning of DT may vary depending on the context in which it is used. For instance, aircraft or system orientation, optimal utilization of advanced physical models, sensors, historical operating data, integration of various multi-disciplinary and multi-scale probabilistic simulation processes and mapping the physical aircraft's corresponding state are all encompassed in NASA's definition of a digital twin.

Meanwhile, in the electrical engineering realm, more specifically in grid-connected IoT devices, some experts argue that DTs for cyber-secure grid-connected devices are real-time

29

simulations that can be employed to monitor system health and event response, and overall efficiency during cyberattack scenarios [4].

Based on the concept of monitoring system health, creating an alternative to check system responses for new patches, and also offering the possibility to check system performance without putting it into jeopardy, an emulator that replicates a 3-level ANPC inverter behavior (DT) was designed in VHDL and embedded within the FPGA.

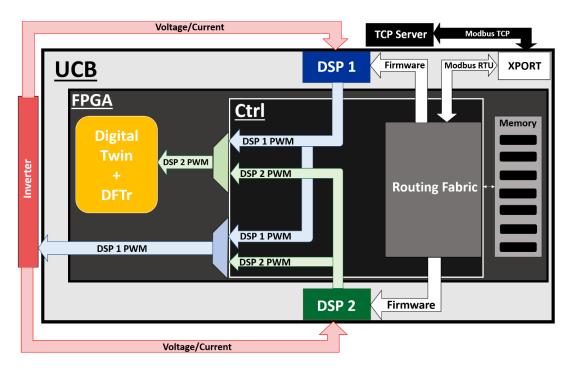

Fig. 21 illustrates the DT implementation for the FPGA subsystem, where the FPGA contains a hardware emulator that mimics the physical hardware of the grid-connected device, which in this case is an ANPC inverter, as shown in Fig. 5. The emulator employs the PWM signals generated by the DSP. Based on its status, the DT determines the corresponding output voltages. Once the 3-level ANPC output has been determined, the FPGA proceeds to collect 192 output samples, with a sampling interval of 100µs, and stores them in its internal RAM, as illustrated in Fig. 21 and Fig. 22. When a user requires access to the output generated by the new firmware in the standby DSP, the FPGA retrieves the relevant data from its RAM and transmits it to the user via the SCI interface. The output is then made available on LabVIEW, among other platforms.

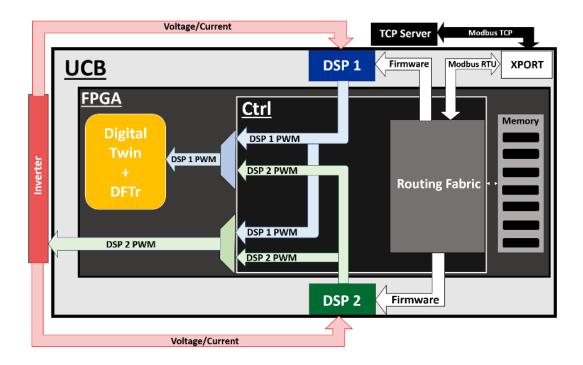

The process of creating a DT for a 3-level ANPC inverter involves utilizing a DSP that is not currently in charge of controlling the inverter. As depicted in Fig. 21, the DSP1 is classified as the active DSP since it is responsible for routing the PWMs that control the inverter. In contrast, DSP2 is identified as the standby or non-active DSP since its PWM signals are directed not to the inverter but to the emulator, which generates the DT and performs firmware validation.

As an illustration, consider a scenario where a user intends to update the device's firmware. The new firmware is transmitted to the FPGA via the SCI interface and is stored in the Flash Memory using the SPI protocol. At this point, the user can load and test the firmware. If the

30

user decides to proceed with testing, the firmware is extracted from the Flash Memory via SPI and transmitted to the standby DSP, which in this instance is DSP2, using the MODBUS RTU protocol. While the DSP1 continues to control the grid-connected device, the DSP2 undergoes an online validation process, which is integrated into the controller board. The validation feature evaluates a set of potential firmware flaws, ensuring that the firmware meets all pre-established requirements, as described in the subsequent section.

Additionally, it simulates the behavior of the 3-level ANPC inverter to verify the functionality of the firmware on the standby DSP. If the new firmware passes all the tests, it becomes available to take over control of the inverter, facilitating hot-patching and providing the DT of the new firmware. If the user opts to hot-patch, the signals that regulate the inverter are switched, with the DSP1 transitioning into the standby DSP role and the DSP2 becoming the active DSP, as illustrated in Figure 19.

Fig. 21. Hardware Architecture (DSP1 as active)

Fig. 22. DSP2 as active

## 2.7 Design-For-Trust

Considering a scenario where an attacker gained access to the inverter and attempted to update the DSP with malicious firmware, to harm the grid or the inverter, or to shut the inverter down, a couple of crucial tests were established and designed in VHDL and embedded in the FPGA. Thus, the DSP firmware must be trustworthy to be approved and allowed to control the inverter.

The DFTr technique was designed to prevent the system from entering situations that pose a potential risk to the ANPC inverter or the power grid. Before a new firmware is activated, tests are conducted to ensure its reliability. If any of these tests fail, the firmware is considered inherently harmful, and the system rejects it and prevents it from becoming active. These tests are processed simultaneously, enhancing the efficiency of the authentication process.

The considered tests were based on critical scenarios that could cause significant damage

to the grid or the inverter. One of the considered tests was to detect short-circuit scenarios due to malicious DSP firmware, which could cause immense damage to the grid and the inverter. Another test was made to prevent new DSP firmware from lacking deadtime, generating short-circuits for a short period but very frequently, which could jeopardize the inverter and the grid. Another test checks if the new firmware is based on the fundamental frequency of 60Hz. The last test is a watchdog that ensures a new firmware is not blank, which would turn the inverter off without any visible changes in the inverter and impact the power delivered to the grid.

## 2.7.1 Short-Circuit

A low-resistance connection between two conductors that power a circuit is commonly referred to as a short-circuit. When electricity flows through a path with low resistance, it creates an electrical short circuit, causing an excessive current flow and voltage streaming in the power supply, leading to potentially dangerous consequences such as circuit overheating, fire, or explosion [28].

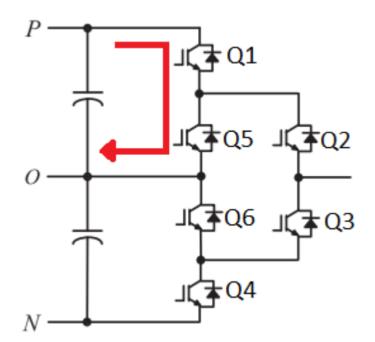

Considering a 3-level ANPC inverter, the scenario that creates a path between the positive, negative, and neutral that generates a short-circuit, known as a shoot-through, must be avoided. Considering one phase lag of the ANPC, Fig. 23 illustrates the scenario when Q1 and Q5 are on simultaneously. The short-circuit path is generated between P and O, which could harm the device. The same idea applies to the scenario where Q4 and Q6 are on simultaneously.

The purpose of the short-circuit tests is to assess the operational switching states of the new firmware and ensure that a short-circuit condition among the switches never occurs, as depicted in Fig. 23.

Fig. 23. Short Circuit scenario [2]

# 2.7.2 Deadtime

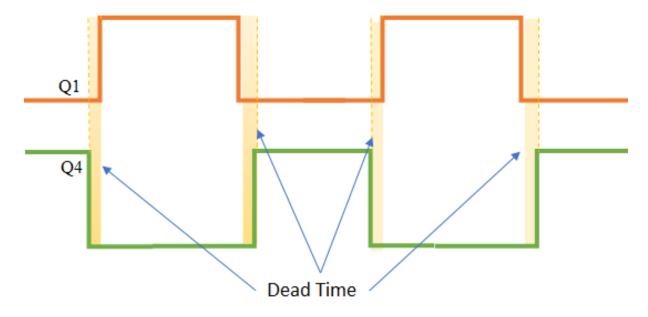

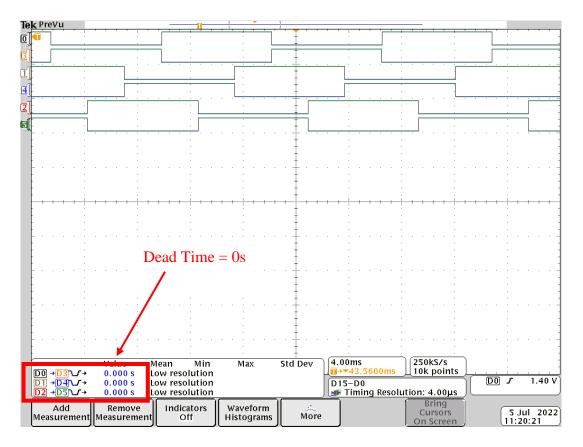

Actual transistors are not ideal, requiring a small amount of time to switch between the on and off states. Hence, a deadtime is necessary for modulation controls to prevent a shoot-through scenario in transistors that cannot be on at the same time. Deadtime refers to the interval between the first transistor turning off and the second turning on. Fig. 24 illustrates a deadtime between Q1 and Q4, as it was used in this project since Q1 and Q4 cannot be on simultaneously because the same PWM sent to Q1 is also forwarded to Q6, while Q4 and Q5 share the same PWM. Therefore, if Q1 and Q4 are on simultaneously, it implies that Q1, Q4, Q5, and Q6 are all on together. This delay is generated by the control circuit, which is the DSP, and is essential because switching delays can cause cross-conduction. The gap is then necessary to prevent it [29].

The deadtime test aims to establish a sufficient delay between switching states to prevent the simultaneous conduction of switches that should not be conducted simultaneously. If this invalid switching configuration were to occur, it could result in a short-circuit for a short period but very frequently, putting the inverter and the grid in jeopardy.

Fig. 24. Dead Time

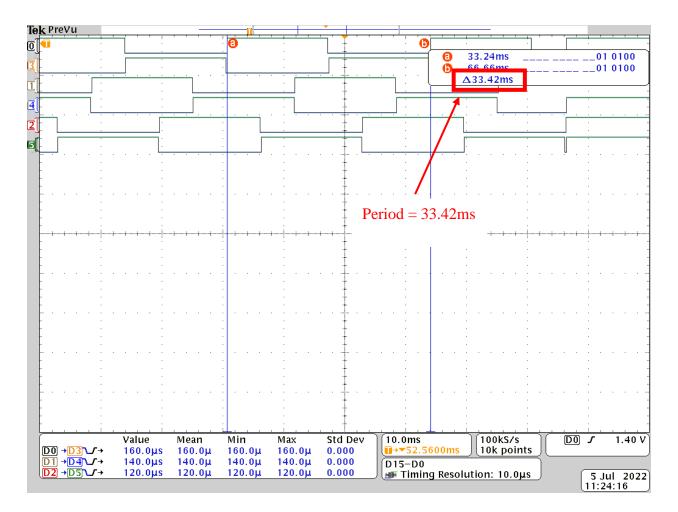

# 2.7.3 Fundamental Frequency

According to the source [30], the electrical systems in the United States currently operate at a frequency of 60Hz. It is essential to maintain a high level of stability in frequency to ensure a reliable electric system. Various factors, such as generation loss and demand overload, can cause frequency variations, adversely affecting the grid. These variations can trigger protection relays involuntarily and lead to the grid reaching the lowest acceptable frequency, which can severely impact the system's stability, as stated in [31].

Furthermore, according to [31], the deployment of under-frequency load-shedding schemes varies across NERC (North American Electric Reliability Corporation) regions and subregions, with different frequency set points. In the United States, the highest initial blocks of load shedding have frequency set points ranging from 59.7 to 59.3 Hz.

Under-frequency load shedding is a process that involves disconnecting a significant number of predetermined customers from the power grid when the frequency drops to pre-set frequency thresholds.

Therefore, when dealing with grid-connected energy resources, it is essential to maintain a stable operational frequency to prevent unwanted harmonic distortions in the grid. The DFTr inside the controller ensures that the DSP firmware of the inverter generates a frequency of 60Hz, which is necessary for the grid's stability. [2].

## 2.7.4 Fast Frequency

This test checks if the new firmware has 42kHz as the frequency for the fast transistors (Q2 and Q3), as this frequency was defined during the progress of this work. Even though new firmware with different frequency values might not be dangerous to the inverter or grid, it can reduce the inverter's performance and change the semiconductors' response with the possibility of increasing losses or harmonics. Thus, during the tests on this work, the firmware needed to remain consistent with the defined characteristics.

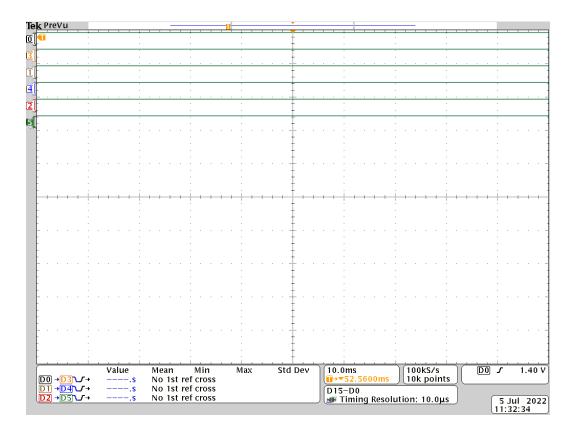

### 2.7.5 Watchdog (Timer)

The final step in validating the DFTr strategy involves verifying that the DSP firmware does not cause the controller to enter a stall state. In this context, a stall state refers to a situation where the FPGA is awaiting both rising and falling edges from the Pulse Width Modulation (PWM) signals but instead receives malicious firmware that lacks any oscillation in the control signals. During the firmware testing phase, the DSP firmware is subject to a maximum waiting time, and if the timer reaches this threshold, the new DSP firmware is rejected.

## CHAPTER 3

#### METHODOLOGY

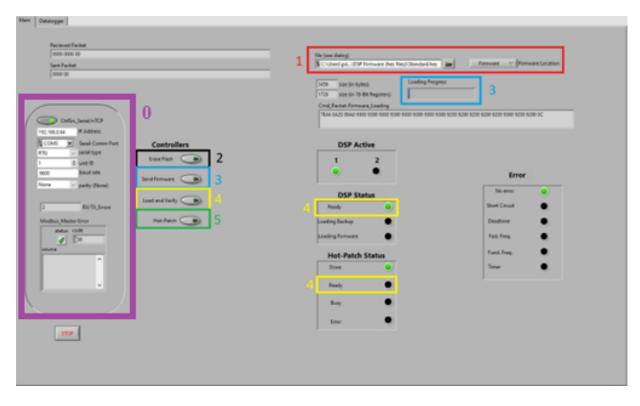

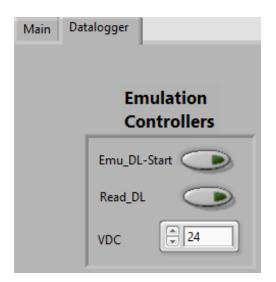

During the development of this work, the LabVIEW 2018 software was used as a Graphic User Interface (GUI) because it allowed the user to interface with the FPGA through Serial Communication Interface (SCI) to send and verify a new DSP firmware, check the DT signals and the active DSP (1 or 2), monitor the DSP status, and show the hot-patch status and possible errors, as presented in Fig. 25.

| Main Datalogger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                                                                                                                                                     |                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Recieved Packet           0000 0000 00           Sent Packet           0000 000           Control on Con |                            | File (use dialog)  I Cr.Users/pdUSP Firmware (hex Files)/Standard.hex  3456 size (in bytes)  1728 size (in bytes)  Cr.d. Packet-Firmware, Loading  7E44 0A20 00A0 9300 9300 9300 9300 9300 9300 930 |                           |

| 192,1680,64  P Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Controllers<br>Ersee Flash | DSP Active                                                                                                                                                                                          | Error<br>No error         |

| 2 RX/TX_Errors<br>Modbus_Master-Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Load and Verify            | DSP Status<br>Ready O<br>Loading Backup                                                                                                                                                             | Short Circuit<br>Deadtime |

| status code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ,                          | Loading Firmware Hot-Patch Status                                                                                                                                                                   | Fast. Freq.               |

| ^                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | Done                                                                                                                                                                                                | Timer                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | Ready                                                                                                                                                                                               |                           |

| STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            | Error                                                                                                                                                                                               |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                                                                                                                                                     |                           |

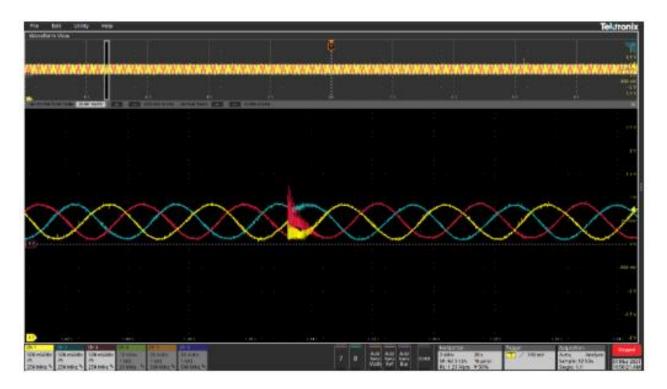

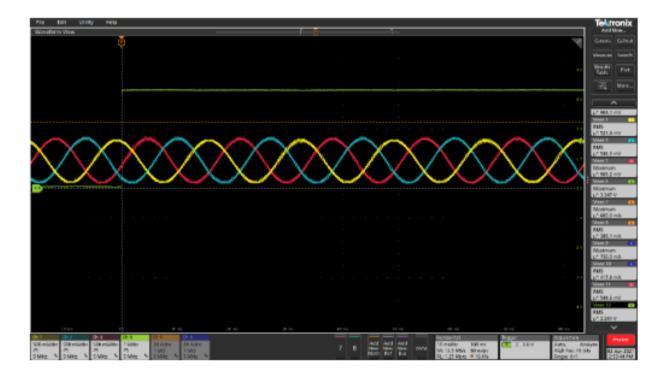

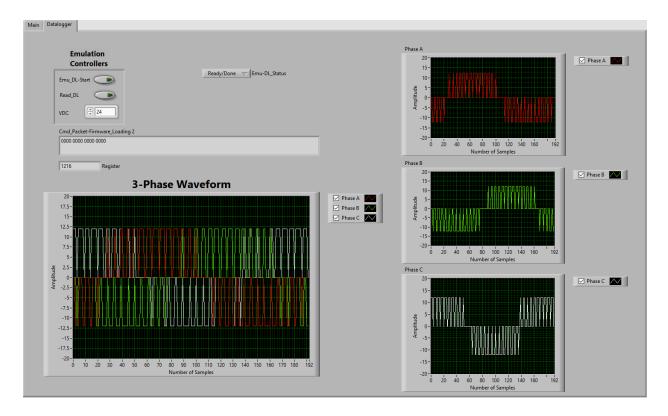

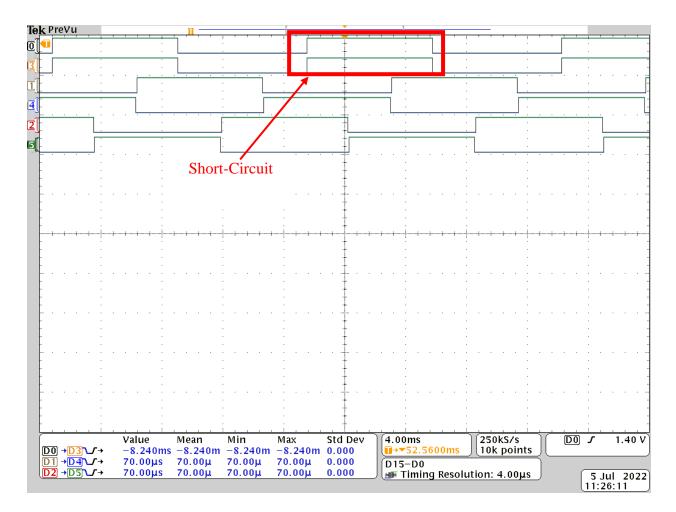

Fig. 25. LabVIEW interface