## University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2023

# Analysis of an Isolated Bidirectional Ćuk Converter

Yeny Hau Chen University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Electrical and Electronics Commons, and the Power and Energy Commons

#### Citation

Hau Chen, Y. (2023). Analysis of an Isolated Bidirectional Ćuk Converter. Graduate Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/5065

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, uarepos@uark.edu.

## Analysis of an Isolated Bidirectional Ćuk Converter

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Yeny Hau Chen University of Arkansas Bachelor of Science in Electrical Engineering, 2021

> May 2023 University of Arkansas

| This thesis is approved for recommendation to the Graduate Council. |                                       |  |  |

|---------------------------------------------------------------------|---------------------------------------|--|--|

|                                                                     |                                       |  |  |

| Juan Carlos Balda, Ph.D. Thesis Director                            |                                       |  |  |

| Yue Zhao, Ph.D. Committee Member                                    | Chris Farnell, Ph.D. Committee Member |  |  |

#### **ABSTRACT**

The objective of this thesis is to perform an analysis of the isolated bidirectional Ćuk dc-dc converter topology and demonstrate the advantages and operation of this configuration through simulations using MATLAB/Simulink<sup>TM</sup> and measurements collected from a 1.5-kW prototype tested at the Engineering Research Center (ENRC) laboratory of the University of Arkansas.

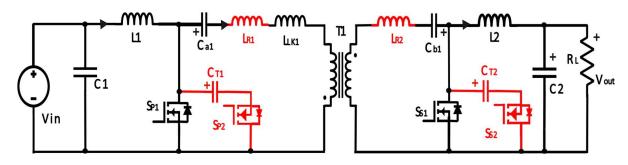

The idea of integrating an active-clamp snubber circuit on each side of the converter, proposed by Dr. Sudip Mazumder from the University of Illinois, Chicago, limits the additional voltage stresses on the components due to the energy from the transformer's leakage inductance. This is studied in this thesis to achieve zero voltage switching (ZVS) turn-ON functionality of all active devices, reducing the losses and size of passive components. In addition, this work evaluates three separate control parameters that are utilized for power transfer, ZVS region, and the circulating current of the converter. These three variables are the duty cycle of  $S_{P1}$ , namely  $d_1$ ; the duty cycle of  $S_{S1}$ , namely  $d_2$ ; and the phase-shift ratio, by the symbol  $\Delta_{\emptyset}$ .

The theoretical analysis is validated through simulations using MATLAB/Simulink<sup>TM</sup> and through a 1.5-kW prototype converter. In addition to the analysis of the results, conclusions and suggestions for future work are presented to enhance the system's quality.

#### ACKNOWLEDGMENTS

First and foremost, I am extremely grateful to my Ph.D. advisor Dr. Juan Carlos Balda for providing me with the opportunity to work on this project and for all his advice and assistance. I also want to extend my appreciation to my committee members Dr. Yue Zhao and Dr. Chris Farnell for agreeing to be part of the committee and their support. In addition, I would like to thank the collaboration of the Ph.D. student, David Porras, who directed me throughout this work with patience, guidance, and motivation.

Finally, I would also like to thank my family, close friends, and colleagues who made the writing process of this thesis easier and possible.

## TABLE OF CONTENTS

| CHAI | PTER  | 1                                                      | 1  |

|------|-------|--------------------------------------------------------|----|

| INTR | ODUC  | CTION                                                  | 1  |

| 1.1  | Mo    | otivations for this Research Work                      | 1  |

| 1.2  | Ob    | jectives and Organization of Thesis                    | 6  |

| 1.3  | Re    | ferences                                               | 7  |

| СНА  | TER   | 2                                                      | 8  |

| ISOL | ATED  | BIDIRECTIONAL ĆUK DC-DC CONVERTERS                     | 8  |

| 2.1  | Int   | roduction                                              | 8  |

| 2.2  | Ću    | k Converter Overview                                   | 8  |

| 2.3  | Iso   | lated Ćuk Converter Topology                           | 11 |

| 2.4  | Fu    | nctionality of the Isolated Ćuk Converter              | 14 |

| 2    | 4.1   | Modes of operation                                     | 16 |

| 2.5  | Sys   | stem Analysis                                          | 28 |

| 2    | 5.1   | Power transfer                                         | 29 |

| 2    | 5.2   | Circulating current                                    | 30 |

| 2    | 5.3   | ZVS operation                                          | 32 |

| 2.6  | Co    | ncluding Remarks                                       | 33 |

| 2.7  | Re    | ferences                                               | 33 |

| СНА  | TER   | 3                                                      | 35 |

| DESI | GN Al | ND SIMULATIONS OF ISOLATED BIDIRECTIONAL ĆUK CONVERTER | 35 |

| 3.1  | Int   | roduction                                              | 35 |

| 3.2  | De    | termining System Parameters                            | 35 |

| 3.2.1 Hardware design                                                  | 35 |

|------------------------------------------------------------------------|----|

| 3.2.2 Control parameters                                               | 37 |

| 3.3 Design Process of the Isolated Ćuk DC-DC Prototype                 | 40 |

| 3.4 MATLAB/Simulink <sup>TM</sup> Simulations                          | 42 |

| 3.4.1 Implementation of the circuit schematic                          | 42 |

| 3.4.2 Implementation of the system control algorithm                   | 43 |

| 3.4.3 Simulation Results                                               | 45 |

| 3.5 Concluding Remarks                                                 | 49 |

| 3.6 References                                                         | 50 |

| CHAPTER 4                                                              | 51 |

| EXPERIMENTAL RESULTS OF THE ISOLATED ĆUK DC-DC PROTOTYPE               | 51 |

| 4.1 Introduction                                                       | 51 |

| 4.2 Testing                                                            | 51 |

| 4.3 Prototype Implementation and Testing                               | 53 |

| 4.3.1 Controller subsystem                                             | 53 |

| 4.3.2 Testing plan                                                     | 56 |

| 4.4 Loss Analysis of Theoretical, Simulation, and Experimental Results | 64 |

| 4.4.1 Theoretical losses                                               | 64 |

| 4.4.1.1 Conduction losses                                              | 64 |

| 4.4.1.2 Switching losses                                               | 65 |

| 4.4.1.3 Magnetic losses                                                | 65 |

| 4.4.2 Performance analysis                                             | 67 |

| 4.5 Concluding Remarks                                                 | 68 |

| 4.6    | References                                  | 69 |

|--------|---------------------------------------------|----|

| СНАРТ  | TER 5                                       | 70 |

| CONCI  | LUSIONS AND RECOMMENDATIONS FOR FUTURE WORK | 70 |

| 5.1    | Conclusions                                 | 70 |

| 5.2    | Recommendations for Future Work             | 71 |

| 5.3    | References                                  | 71 |

| Append | lix A                                       | 72 |

| MATL   | AB Code                                     | 72 |

## LIST OF FIGURES

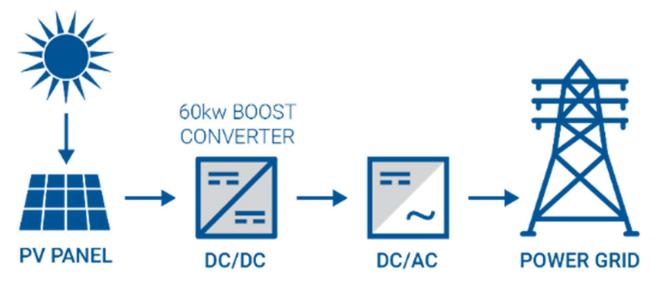

| Fig. 1.1: Solar DC/DC and DC/AC power conversion [3].                                                          | 2  |

|----------------------------------------------------------------------------------------------------------------|----|

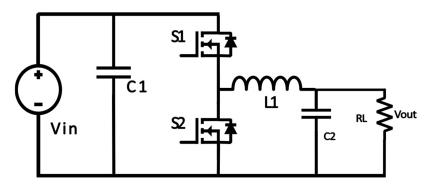

| Fig. 1.2: Non-isolated bidirectional dc-dc converter (half-bridge)                                             | 3  |

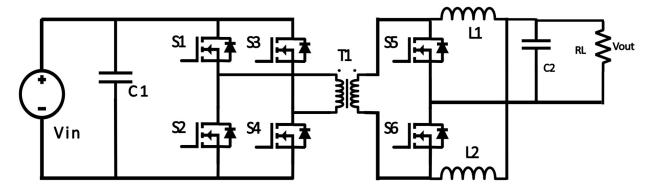

| Fig. 1.3: Isolated bidirectional dc-dc converter (full bridge on the input side)                               | 4  |

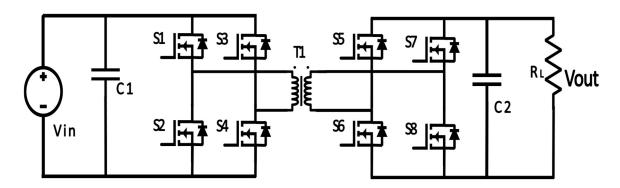

| Fig. 1.4: Dual active bridge dc-dc converter (two full bridges)                                                | 4  |

| Fig. 1.5: Conventional isolated bidirectional Ćuk dc-dc converter.                                             | 5  |

| Fig. 2.1: Non-isolated Ćuk converter.                                                                          | 9  |

| Fig. 2.2: Buck-boost converter                                                                                 | 9  |

| Fig. 2.3: Switch-ON interval.                                                                                  | 11 |

| Fig. 2.4: Switch-OFF interval.                                                                                 | 11 |

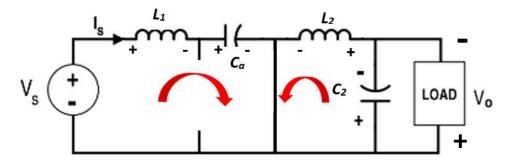

| Fig. 2.5: Steps to have dc isolation in the original Ćuk converter                                             | 12 |

| Fig. 2.6: Conventional isolated bidirectional Ćuk dc-dc converter.                                             | 13 |

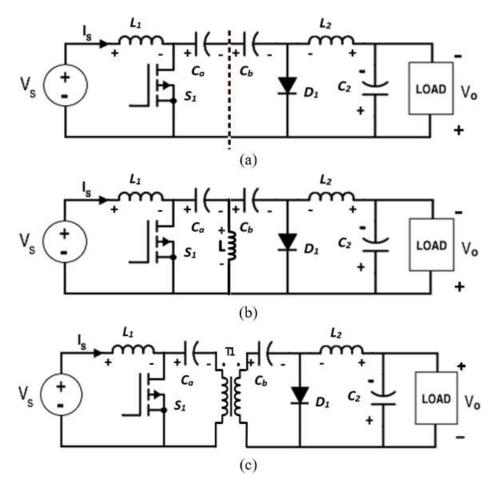

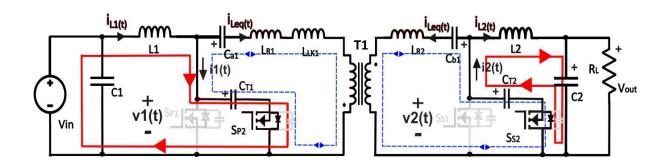

| Fig. 2.7: Proposed isolated bidirectional Ćuk converter with an active-clamp                                   | 14 |

| Fig. 2.8: Main operating mode 1 [t <sub>0</sub> -t <sub>1</sub> ]: M <sub>1</sub>                              | 18 |

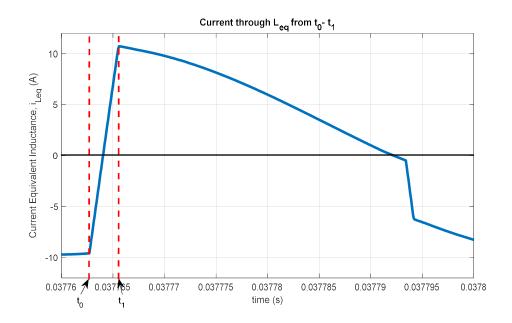

| Fig. 2.9: Current through the equivalent inductance <i>Leq</i> during interval t <sub>0</sub> -t <sub>1</sub>  | 19 |

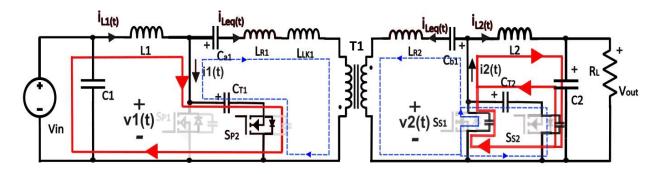

| Fig. 2.10: Transition mode 1 [t <sub>1</sub> -t <sub>2</sub> ]: T <sub>1</sub>                                 | 20 |

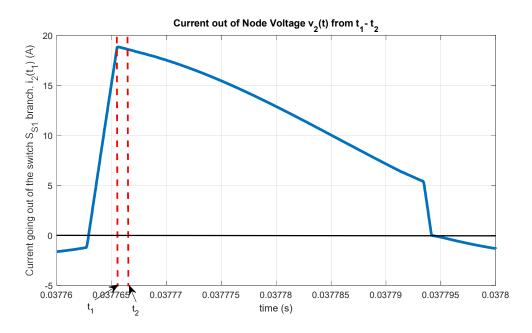

| Fig. 2.11: Current $i_2(t)$ flowing out of the node voltage $v_2(t)$ during interval $t_1$ - $t_2$             | 20 |

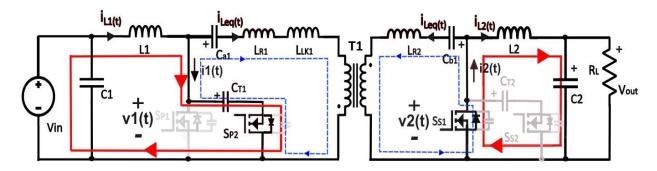

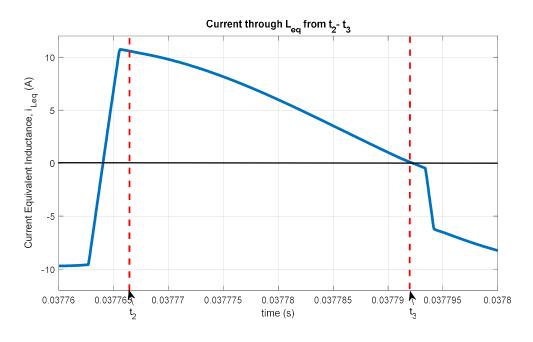

| Fig. 2.12: Main operating mode 2 [t <sub>2</sub> -t <sub>3</sub> ]: M <sub>2</sub>                             | 21 |

| Fig. 2.13: Current through the equivalent inductance <i>Leq</i> during interval t <sub>2</sub> -t <sub>3</sub> | 21 |

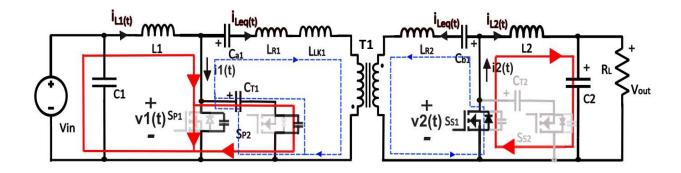

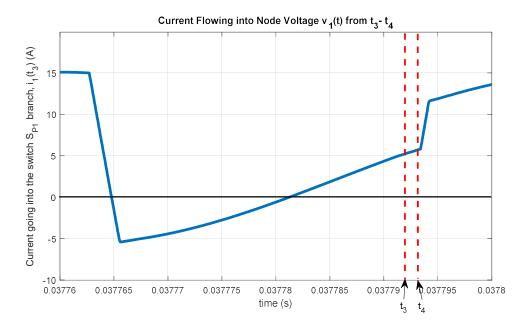

| Fig. 2.14: Transition mode 2 [t <sub>3</sub> -t <sub>4</sub> ]: T <sub>2</sub>                                 | 22 |

| Fig. 2.15: Current $i_1(t)$ flowing into the node voltage $v_1(t)$ during interval $t_3$ - $t_4$               | 23 |

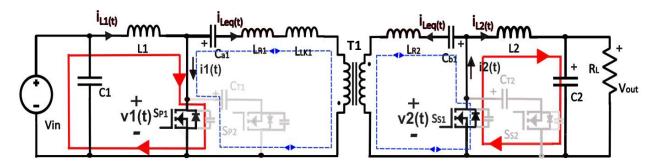

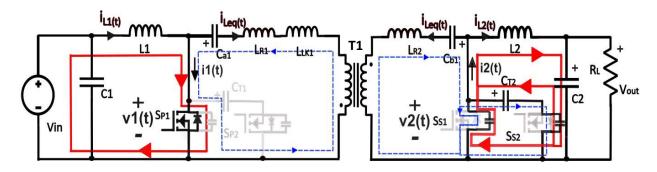

| Fig. 2.16: Main operating mode 3 [t <sub>4</sub> -t <sub>5</sub> ]: M <sub>3</sub>                             | 24 |

| Fig. 2.17: Current through the equivalent inductance <i>Leq</i> during interval t <sub>4</sub> -t <sub>5</sub> | 24 |

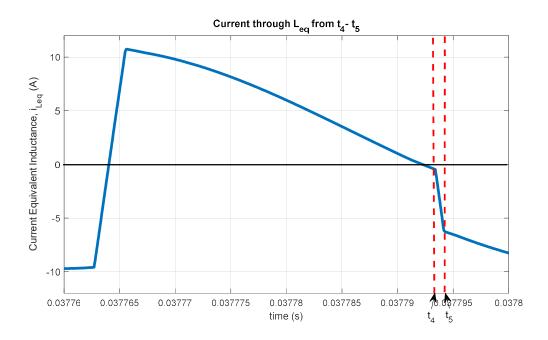

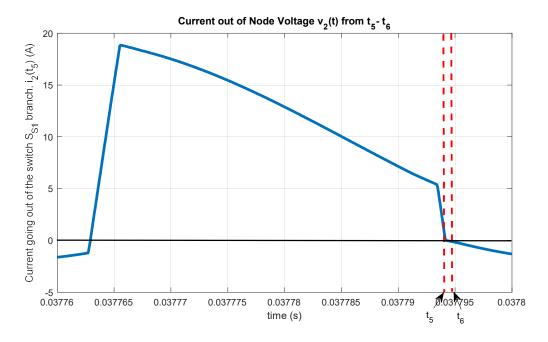

| Fig. 2.18: Transition mode 3 [t <sub>5</sub> -t <sub>6</sub> ]: T <sub>3</sub>                                 | 25 |

| Fig. 2.19: Current $i_2(t)$ flowing out of the node voltage $v_2(t)$ during interval $t_5$ - $t_6$             | 25 |

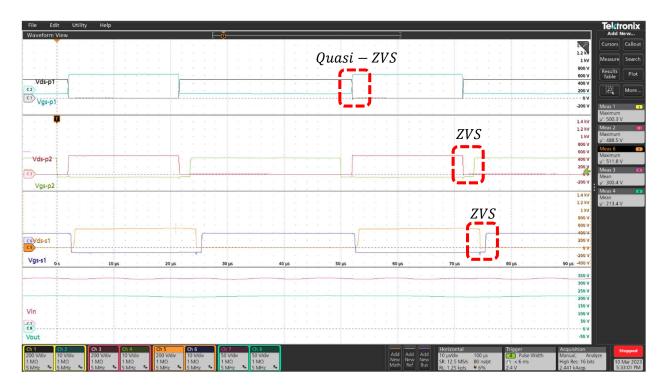

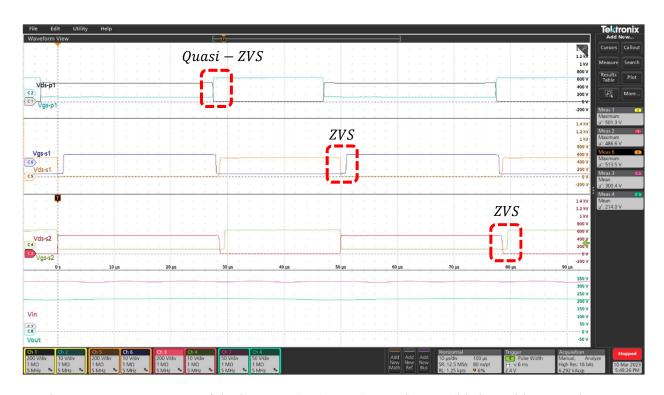

| Fig. 4.7: ZVS turn-ON of the main devices $S_{P1}$ (top), $S_{S1}$ (second), input voltage (third), output voltage (fourth), and output current (bottom) at $Vin = 300 \text{ V}$ and $G = 0.71$ |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

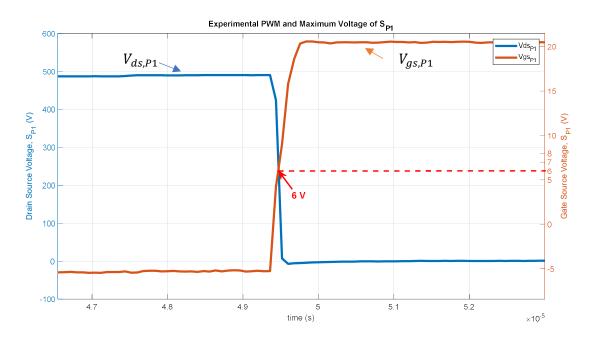

| Fig. 4.8: Zoomed-in view of the experimental voltages $V_{ds,P1}$ (left) and $V_{gs,P1}$ (right)                                                                                                 | . 59 |

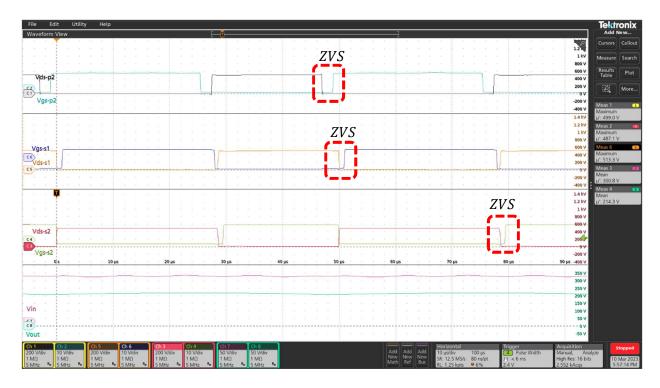

| Fig. 4.9: ZVS turn-ON of devices $S_{P1}$ (top), $S_{P2}$ (second), $S_{S1}$ (third), and input and output voltages (bottom) at rated power.                                                     | . 62 |

| Fig. 4.10: ZVS turn-ON of devices $S_{P1}$ (top), $S_{S1}$ (second), $S_{S2}$ (third), and input and output voltages (bottom) at rated power.                                                    | . 62 |

| Fig. 4.11: ZVS turn-ON of devices $S_{P2}$ (top), $S_{S1}$ (second), $S_{S2}$ (third), and input and output voltages (bottom) at rated power.                                                    | . 63 |

| Fig. 4.12: ZVS turn-ON of devices $S_{P1}$ (top), $S_{P2}$ (second), $S_{S2}$ (third), and input and output voltages (bottom) at rated power.                                                    | . 63 |

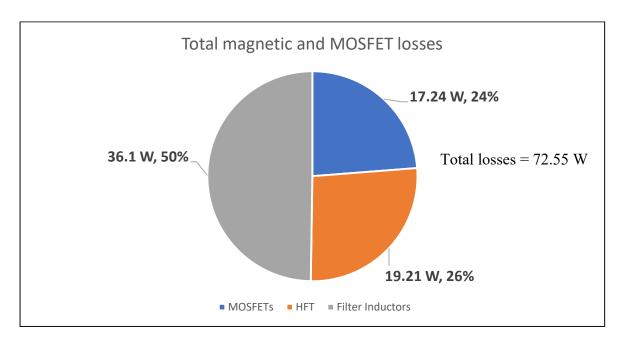

| Fig. 4.13: Theoretical losses of the system.                                                                                                                                                     | . 67 |

# LIST OF TABLES

| Table 1.1: Characteristics of the Different Type of Converters                            | . 6 |

|-------------------------------------------------------------------------------------------|-----|

| Table 2.1: Series Inductor Current for Each Main Operating Mode [6], [7]                  | 31  |

| Table 2.2: Conditions of $i_{Leq}(t)$ to Ensure ZVS Turn-ON                               | 32  |

| Table 3.1: Parameters of the Designed Prototype                                           | 41  |

| Table 3.2: Other Component Values for the Designed Prototype                              | 42  |

| Table 3.3: Signal statistics of the input and output currents and voltages                | 47  |

| Table 4.1: Test Equipment and Instrumentation                                             | 51  |

| Table 4.2: Operational conditions for $Pout = 672 \text{ W}$ and $Vin = 200 \text{ V}dc$  | 56  |

| Table 4.3: Operational conditions for $Pout = 1.5 \text{ kW}$ and $Vin = 300 \text{ V}dc$ | 58  |

| Table 4.4: Experimental Power Efficiency                                                  | 64  |

| Table 4.5: Comparison of Power Loss and Efficiency                                        | 67  |

#### **CHAPTER 1**

#### INTRODUCTION

## 1.1 Motivations for this Research Work

The sustainability of life on Earth is critically dependent on the environment. The current world faces difficulties to improve energy efficiency and reduce greenhouse effects, caused by the carbon dioxide emitted from typical internal combustion engines used in most vehicles, methane emitted from a variety of anthropogenic and natural resources such as agricultural activities, coal mining, and certain industrial processes, etc. [1]. Renewable energy is considered to be the most effective option for managing these environmental challenges because it can supply energy free of air pollution and greenhouse gas emissions by generating pretty much zero of these gases [2].

The spread of most renewable energy sources is partially dependent on the advancement of power electronic systems, which offer reliability, efficiency, and reduced cost. In the last few decades, typical bidirectional dc-dc converters such as the buck, boost, and dual active bridge (DAB) have become the focus of research in power electronics. A bidirectional dc-dc converter steps down or steps up dc voltage from one side to the other while being driven by a gate-signal generator and related controller. It is a key component in numerous modern applications, including those for servers, energy storage, automobiles, and renewable energy systems. For instance, Fig. 1.1 illustrates an example of a general topology of energy conversion from solar energy, which is a renewable energy source, consisting of series-connected 60-kW boost converter (DC/DC) and inverter (DC/AC) that will deliver the desired output voltage or current, which it will be in this case to the power grid. Several renewable energy sources provide electrical energy in the dc form, which is then transmitted in ac form for usage in domestic,

Fig. 1.1: Solar DC/DC and DC/AC power conversion [3].

commercial, and industrial applications. However, many applications and gadgets need dc power to function, so power conversion is once again more necessary.

With reference to Fig. 1.1, the dc-dc converter is an important subsystem in a renewable energy system. Converters must be developed in a compact manner, so the power electronic converter topology is very significant. The dc-dc converter topologies are designed to compensate for the mismatch in power supply availability and variations in current and voltage levels that the load demands. The dc-dc converter is used to alter the input dc voltage from one level to another.

The bidirectional dc-dc converter block in MATLAB/Simulink<sup>TM</sup> allows to model different topologies of converters, such as non-isolated converters with two switching devices, isolated converters with six switching devices, or DAB converters with eight switching devices [4]. In the next paragraphs, these topologies are explained and their configurations are presented. In particular, this thesis' work focuses on the analysis of the isolated bidirectional Ćuk dc-dc converter which will be expanded upon in more detail in the next chapter.

A non-isolated bidirectional dc-dc converter lacks an electrical isolation barrier provided by a transformer. This type of converter is the typical non-isolated half-bridge topology, as illustrated in Fig. 1.2 consisting of an inductor, two capacitors, and two switches that are of the same device type. This converter consists of a combination of a step-up and step-down converter connected in anti-parallel where the operation of the circuit can be explained by two modes. Switch  $S_1$  operates with the proper duty cycle during the forward step-down process, while switch  $S_2$  is always OFF while its anti-parallel diode is conducting. As an alternative,  $S_1$  is always OFF and  $S_2$  is in operation throughout the backward step-up process. If the switch in the OFF state is a MOSFET, synchronous rectification (SR) used to increase efficiency is possible [5].

An isolated bidirectional dc-dc converter does have an electrical isolation barrier provided by a transformer separating the input and output voltages. This converter has four additional switches, which makes a total of six switching devices that form a full bridge located on the input side of the converter and the other two switches are on the output side of the converter. Some passive components such as capacitors and inductors are also included in the system to eliminate switching noise and regulate the output voltage. The isolated bidirectional dc-dc converter's schematic circuit, which places the full bridge on the converter's input side, is displayed in Fig. 1.3.

Fig. 1.2: Non-isolated bidirectional dc-dc converter (half-bridge).

Fig. 1.3: Isolated bidirectional dc-dc converter (full bridge on the input side).

The DAB is a bidirectional, controllable, dc-dc converter suitable for medium and highpower applications comprised of eight semiconductor devices or two full bridges, a highfrequency transformer (HFT), and some passive components such as transfer inductors and dclink capacitors as shown in Fig. 1.4. It is also known as a full bridge with a controllable rectifier

due to its configuration. The isolated bidirectional DAB-based dc-dc converter has a number of

benefits over conventional ones, including electrical isolation, excellent reliability, and

bidirectional power transmission [6]. Nevertheless, because the DAB employs so many switches

and additional filtering components, a number of innovative converter topologies have been

invented to identify the best electrical connections for power processing elements, such as

switches, storage components, and transformers in order to achieve the highest efficiency and

best performance.

Fig. 1.4: Dual active bridge dc-dc converter (two full bridges).

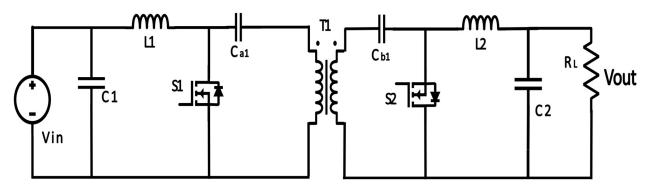

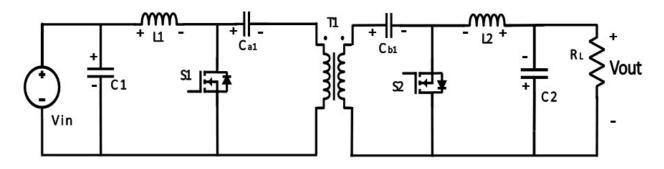

In contrast to the DAB, the isolated bidirectional Ćuk dc-dc converter can be implemented with just two active switches. Some passive components such as  $L_1$ ,  $C_{a1}$ ,  $C_{b1}$ , and  $L_2$  are also added to this topology. As illustrated in Fig. 1.5, this converter combines the functions of buck and boost converters so that the input side behaves like a boost and the output side like a buck in a disconnected inverting fashion.

Due to its wide operating range and special characteristic of continuous current flow at both terminals, the isolated bidirectional Ćuk dc-dc converter is a great solution for integrating renewable energy sources as a voltage regulator in hybrid solar-wind technology, where the input voltage depends on the sun irradiance and wind velocity. The Ćuk converter modifies the output voltage in response to inputs that vary with the strength of the sun and wind. In addition, the Ćuk converter can be utilized in battery management systems of electric vehicles. Overall, the Ćuk converter is used when an output voltage that is smaller or larger than the input voltage is required—mostly at high output voltage levels with negative polarity and low-standby currents.

Furthermore, the output voltage polarity can be freely chosen due to the transformer's isolation of the converter denoted by T1. Even with a 1:1 ac transformer, this output voltage can be greater or less than the input voltage. However, the turns ratio of the transformer can be adjusted to reduce device stress on the input side.

Fig. 1.5: Conventional isolated bidirectional Ćuk dc-dc converter.

Table 1.1: Characteristics of the Different Type of Converters

| Converter<br>Topology | Non-isolated<br>(Half-Bridge) | Isolated<br>(Full-bridge) | DAB | Isolated Ćuk |

|-----------------------|-------------------------------|---------------------------|-----|--------------|

| No. of Switches       | 2                             | 6                         | 8   | 2            |

| No. of Diodes         | 2                             | 6                         | 8   | 2            |

| No. of Capacitors     | 2                             | 2                         | 2   | 4            |

| No. of Inductors      | 1                             | 2                         | 0   | 2            |

| Isolation             | No                            | Yes                       | Yes | Yes          |

Table 1.1 summarizes the characteristics of the various dc-dc converter topologies that were previously presented. In a typical (non-isolated) dc-dc converter, current can flow directly from input to output, decreasing cost, size, and complexity. However, galvanic isolation or simply known as isolation is frequently needed in applications to electrically separate the input and output sides of the device. In this case, a transformer is utilized to transfer current and voltage across the gap between the input and output sides of an isolated dc-dc converter. Other advantages of isolation include separating noise-sensitive circuit components from the sources of that noise, meeting safety standards, etc. [7]. Due to the number of components and its several advantages, the Ćuk converter is selected as the topology to be studied in this thesis.

## 1.2 Objectives and Organization of Thesis

From an analysis of Table 1.1, the main objective of this thesis is to perform an analysis of the isolated bidirectional Ćuk converter topology and demonstrate experimentally the advantages of this configuration in a 1.5-kW rated power scaled-down prototype. Equipment available at the National Center for Reliable Electric Power Transmission (NCREPT) and the Engineering Research Center (ENRC) laboratory at the University of Arkansas will be used to test this prototype.

The structure of this thesis is as follows: Chapter 2 addresses the theoretical aspects of

the isolated bidirectional Ćuk converter topology providing the necessary insights to understand its functioning. Chapter 3 provides the design equations that determine the system parameters and simulations based on MATLAB/Simulink<sup>TM</sup> to enable the development of control algorithms. The experimental results of the scaled-down prototype and comparison analysis of the calculation, simulation, and experimental results are given in Chapter 4. Finally, conclusions and recommendations for future work are identified in Chapter 5.

#### 1.3 References

- [1] "Global Methane Initiative," EPA. Available: https://www.epa.gov/gmi/importance-methane#:~:text=Methane%20(CH4)%20is%20a,%2Dinfluenced)%20and%20natural%2 0sources. (Accessed: Oct. 05, 2022).

- [2] N.L. Panwara, S.C. Kaushik, S. Kothari. "Role of renewable energy sources in environmental protection: A review," Renew Sustain Energy Rev, 15 (2011), pp. 1513-1524.

- [3] M. D. P. Emilio and G. Moxey, "Enabling Solar and Renewable Energy Power Conversion with SiC," Power Electronics News, Feb. 15, 2021. Available: https://www.powerelectronicsnews.com/enabling-solar-and-renewable-energy-power-conversion-with-sic/. (Accessed: Oct. 05, 2022).

- [4] "Controller-driven bidirectional DC-DC step-up and step-down voltage regulator MATLAB," www.mathworks.com. Available: https://www.mathworks.com/help/sps/ref/bidirectionaldcdcconverter.html. (Accessed: Oct. 12, 2022).

- [5] R. Selders, "Synchronous rectification in high-performance power converter design," Texas Instruments Inc., Sept. 2016. Available: https://www.ti.com/lit/wp/snva595a/snva595a.pdf (Accessed: Oct. 27, 2022).

- [6] R. W. De Doncker, M. H. Kheraluwala, and D. M. Divan, "Power conversion apparatus for DC-DC conversion using dual active bridges," U.S. Patent 5027264, Jun. 25, 1991.

- [7] S. Keeping, "Use Isolated DC-DC Converters with Embedded Transformers to Ease Assembly," Digi-key Electronics. Available: https://www.digikey.com/en/articles/use-isolated-dc-dc-converters-with-embedded-transformers-to-ease-assembly. (Accessed: Oct. 27, 2022).

#### **CHAPTER 2**

## ISOLATED BIDIRECTIONAL ĆUK DC-DC CONVERTERS

#### 2.1 Introduction

This chapter overviews the basic topologies of the conventional non-isolated and isolated bidirectional Ćuk converters and their principles of operation. In particular, the functionality and modes of operation of the isolated bidirectional Ćuk converter with an active-clamp topology are explained. Chapter 2 also addresses the theoretical analysis of the converter, which is the first stage of any design.

The structure of this chapter is organized as follows: Section 2.2 addresses an overview of the conventional non-isolated bidirectional Ćuk converter. Section 2.3 presents the topology of the conventional isolated bidirectional Ćuk converter as well as the isolated bidirectional Ćuk converter with an active-clamp to accomplish soft-switching turn-ON. Section 2.4 discusses the functionality and modes of operation of this converter. Section 2.5 analyzes the system through three characteristics that are relevant to the control parameters; namely the power transfer, circulating current, and ZVS operation. Section 2.6 provides a summary of the accomplishments of this entire chapter and describes the goals for the following chapter.

#### 2.2 Ćuk Converter Overview

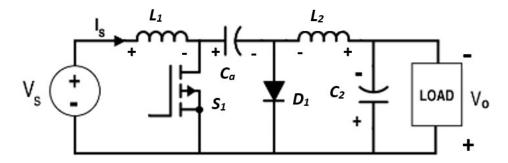

In 1977, Prof. Slobodan Ćuk developed the switching dc-dc converter called the Ćuk switched-mode dc-dc voltage converter [1], [2]. This configuration, illustrated in Fig. 2.1, makes use of the fewest possible inductive and capacitive storage and switching components in order to completely imitate the ideal dc-dc converter with theoretically pure input and output dc currents. Two inductors, two capacitors, one diode, and one switching transistor comprise the non-isolated Ćuk converter. Replacing the diode with another transistor makes the converter bidirectional,

while also adding a transformer and replacing the series capacitor with two series capacitors makes the converter an isolated bidirectional Ćuk converter, as previously presented in Fig. 1.5.

The original non-isolated Ćuk converter was designed to overcome the main disadvantages of the buck-boost converter illustrated in Fig. 2.2, such as significant ripple in the output current and Electromagnetic Interference (EMI) issues caused by the discontinuous input current and the charging current of the output capacitor. The Ćuk converter is also capable of both stepping up and stepping down the output voltage and, therefore, the current. Hence, the output voltage can be either higher or lower than the input voltage depending on the application and operating conditions controlled by the duty ratio of the switching transistor. The Ćuk converter has other advantages, such as having reduced voltage ripple on the input and output sides due to the usage of two inductors, and having higher efficiency, reduced EMI, smaller size and weight, etc. [3].

Fig. 2.1: Non-isolated Ćuk converter.

Fig. 2.2: Buck-boost converter.

Similar to the basic buck-boost converter, the Ćuk converter also results in a negative output voltage, meaning the output voltage with respect to the same input ground has a negative value. The energy flows from the input to the output through the coupling capacitor  $C_a$ , which is another variation in how this converter works. Comparatively to other dc-dc converters, the Ćuk converter demands a more complex controller in terms of control design.

Due to complexity and the lack of a rational strategy for achieving the appropriate magnetics design that provides "zero-ripple" terminal currents, only a small percentage of users are able to quickly adapt the Ćuk converter and its variants to their applications [4].

Before a detailed analysis of the isolated topology, which has more components added to the conventional non-isolated bidirectional Ćuk converter, it is significantly important to understand first the basic topology and its operation. The variations of the topology of the original Ćuk converter are covered in detail through this chapter. During the analysis of Fig. 2.1, the blocking capacitor  $C_a$  must be large enough so that its voltage can be assumed constant under steady-state conditions. The presence of the inductors  $L_1$  and  $L_2$  in series with the input and output ports (source and load), respectively, ensures the currents in both input and output are non-pulsating currents, which implies the input current should be smooth and the output capacitor  $C_2$  is small. Assuming that the components or  $L_1$ ,  $C_a$ ,  $C_2$ , and  $L_2$  do not hold any charge, there are two cases under steady-state conditions of the equivalent circuit of a Ćuk converter that can be analyzed:

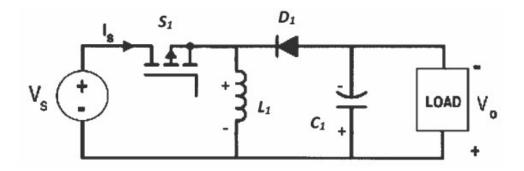

a) Switch-ON interval: When the switch  $S_1$  is turned ON, the diode  $D_1$  is reverse-biased by the voltage across the capacitor  $C_a$ . The inductor  $L_1$  rises flowing through the switch and back to the source. At the same time, the stored energy in the capacitor  $C_a$  from the previous cycle is fed to the load and increases the energy stored in  $L_2$ . The key point is

that this current also flows through the switch. Fig. 2.3 displays how the circuit behaves when the switch  $S_1$  is closed.

b) Switch-OFF interval: During this OFF interval, the current through the inductor  $L_2$  and  $L_1$  flows through the diode (that is forward biased). In the process, current  $i_{L1}$  charges capacitor  $C_a$  and current  $i_{L2}$  charges the output capacitor  $C_2$  and supplies the load. Fig. 2.4 shows the equivalent circuit when the switch is turned OFF.

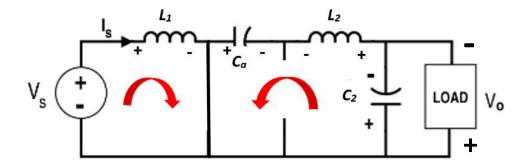

## 2.3 Isolated Ćuk Converter Topology

Following three essential procedures, the crucial electrical isolation feature, frequently required in practice, can be introduced easily and optimally [2]. First, the coupling capacitor  $C_a$  is separated into two series or blocking capacitors  $C_a$  and  $C_b$ , each one being a mirror image of the other, as shown in Fig. 2.5(a). Next, there is an unknown dc voltage at the connection point

Fig. 2.3: Switch-ON interval.

Fig. 2.4: Switch-OFF interval.

between these two capacitors. By adding an inductor between this point and ground, this uncertain voltage can then be set to zero, as seen in Fig. 2.5(b). Finally, in order to achieve the needed electrical isolation between input and output, the additional inductance is simply divided into two equal transformer windings, and the transformer is denoted by T1 as illustrated in Fig. 2.5(c). The transformer turns ratio is arbitrarily assumed unity.

When compared to other widely-used isolated switching architectures, the electrical isolation obtained in this manner not only has some exceptional qualities but also entirely preserves the general characteristics of the basic converter. The two inductors of the basic Ćuk converter can be integrated into a single magnetic circuit with two windings, primary and secondary, respectively; this approach is the so-called "integrated magnetics" [2].

Fig. 2.5: Steps to have dc isolation in the original Ćuk converter.

The inductor coupling adds a concurrent inductive energy transfer to the initial capacitive energy transfer that existed between the input and output ports. Therefore, it may naturally be assumed that using this coupling mechanism results in less ripple currents at both the input and output; this is actually, the case.

Now, the conventional isolated bidirectional Ćuk dc-dc converter circuit shown in Fig. 1.5, which is also presented in this chapter as Fig. 2.6, can be analyzed. The left switch  $S_1$  is controlled by a pulse width modulation (PWM) signal, just like in the original Ćuk converter in the forward mode, whereas the right switch  $S_2$  is OFF, making it function like a standard diode. In contrast,  $S_2$  is controlled by the PWM signal in the reverse mode, while  $S_1$  is turned OFF to function as a diode [5]. The output voltage polarity can be chosen freely since the converter is isolated by the transformer. This output voltage can have a higher or lower magnitude than the input voltage even with a 1:1 transformer, with the turns ratio of this transformer can be determined to lessen device stresses on the input side [2].

Just two active switches are required in an isolated bidirectional Ćuk dc-dc converter; however, these switches are hard-switched resulting in larger losses. This sort of converters typically uses a lossy snubber circuit to reduce the drain-to-source voltage across the devices by dissipating the energy stored in the leakage inductance of a common high-frequency transformer

Fig. 2.6: Conventional isolated bidirectional Ćuk dc-dc converter.

(HFT). As a result, the converter suffers additional losses which minimize its application, so a lossless snubber solution should be implemented [6], [7]. To achieve this, however, a number of passive components are required, but it is well known that they increase the system's losses and reduce efficiency.

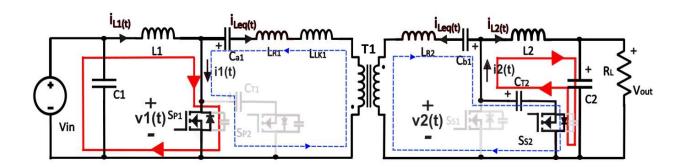

Dr. Sudip Mazumder and his doctoral student, Shantanu Gupta from the University of Illinois at Chicago, proposed the idea of incorporating an active-clamp snubber circuit in each side of the converter, consisting of a capacitor, a series resonant inductor, and an auxiliary switch to limit the voltage stresses on the components and transfer energy from the leakage inductance of the transformer to the clamp capacitor [6], [7]. Potentially, the efficiency increases could be around 8 % by eliminating turn-on losses. The active-clamp circuit helps the switching devices to operate at higher switching frequencies and enables zero voltage switching (ZVS) turn-ON of the main switches, reducing the losses and sizes of passive components. Fig. 2.7 illustrates the proposed topology for the isolated bidirectional Ćuk dc-dc converter which will be analyzed throughout this work.

## 2.4 Functionality of the Isolated Ćuk Converter

With reference to Fig. 2.7, the primary-side circuit consists of the input source represented by voltage  $V_{in}$ , input capacitor  $C_1$ , input inductor  $L_1$ , primary series resonant inductor  $L_{R1}$ , primary soft-switching or auxiliary capacitor  $C_{T1}$ , main primary switch  $S_{P1}$ ,

Fig. 2.7: Proposed isolated bidirectional Ćuk converter with an active-clamp.

auxiliary primary switch  $S_{P2}$ , primary blocking capacitor  $C_{a1}$ , and leakage inductance referred to the primary side,  $L_{LK1}$ . The secondary blocking capacitor  $C_{b1}$ , secondary series resonant inductor  $L_{R2}$ , secondary soft-switching or auxiliary capacitor  $C_{T2}$ , main secondary switch  $S_{S1}$ , auxiliary secondary switch  $S_{S2}$ , output inductor  $L_2$ , output capacitor  $C_2$ , and resistive load  $R_L$  form the secondary-side circuit. The middle part of the system that connects both sides is the isolating transformer T1 and the two active-clamp circuits in this topology are needed for bidirectional operation. The power flow is defined as positive (forward mode) when power is transferred from  $V_{in}$  to  $V_{out}$ , and  $S_{S1}$  operates in synchronous rectification (SR) mode, whereas the power flow is defined as reverse power flow (backward mode) when power is transferred from  $V_{out}$  to  $V_{in}$ , and  $S_{P1}$  operates in SR mode. The switches' conduction losses are decreased under SR operation.

The converter's ZVS functioning is dependent on the transformer's magnetizing inductance, even though the active-clamp circuit serves as a snubber circuit to decrease the impact of the transformer leakage inductance. The lower the leakage inductance, the higher the auxiliary and blocking capacitors are required to avoid resonance between them. Therefore, a high-switching frequency operation is critical for achieving ZVS [6], [7].

The modulation techniques of this converter will be based on three control parameters: the duty cycle of  $S_{P1}$ ,  $d_1$ ; duty cycle of  $S_{S1}$ ,  $d_2$ ; and the phase-shift ratio  $\Delta_{\emptyset}$ . The phase-shift ratio is the ratio between the time periods when both main switches are inactive in the switching interval, that is:

$$\Delta_{\emptyset} = \frac{t_{SP1,OFF}}{t_{SS1,OFF}}.\tag{2.1}$$

This produces a broad ZVS range and increased efficiency for a wide voltage gain. The duty cycles of the two main switches  $S_{P1}$  and  $S_{S1}$  work in a complementary mode in the conventional modulation. However, the modulation proposed in [6] and [7] suggests that the

duty cycles of these switches and the phase-shift ratio are independently controlled, allowing other degrees of freedom. A variety of optimization strategies are presented to lower the circulating current for a given output power when maintaining ZVS operation to lower conduction losses. The authors of [6] and [7] proposed that  $d_1$  and  $d_2$  should be optimized to accomplish the minimal circulating current while keeping a constant  $\Delta_{\emptyset}$  [6], [7].

## 2.4.1 Modes of operation

Using the active-clamp circuits and the equivalent series inductor  $L_{eq}$ , which is the sum of the series resonant inductors  $L_{R1}$  and  $L_{R2}$  as well as the leakage inductances of the transformer  $L_{LK1}$  and  $L_{LK2}$ , the proposed Ćuk converter provides ZVS turn-ON of all switches. The main MOSFET switch's body diode turns ON before the gate goes high due to the active-clamp circuit's producing a negative drain-to-source current,  $i_{ds}$ , through the main switch which enables ZVS turn-ON, whereas the constant voltages from the auxiliary and blocking capacitors over a switching cycle are applied to the equivalent series inductor  $L_{eq}$ , causing circulating current and power transfer. The inductor current  $i_{Leq}$  must be linear throughout the main modes in order for the converter to operate linearly; this is made possible by eliminating LC resonances.

Only the forward power flow of the converter topology, from the turn-OFF of  $S_{P1}$  to the turn-ON of  $S_{S1}$ , is considered in this thesis [6], [7].

In switch-mode power conversion circuits, the "volt-seconds balance" refers to the fact that the integral of the voltage waveforms applied to  $L_1$ ,  $L_2$ , and  $L_{eq}$  must be zero over one complete switching cycle under steady-state conditions. The following average voltage equations can then be obtained:

$$V_{CT1} = \frac{V_{in}}{d'_{1}} \tag{2.2}$$

$$V_{CT2} = \frac{V_{out}}{d'_2} \tag{2.3}$$

$$V_{Ca1} + V_{Cb1} = V_{in} + V_{out} (2.4)$$

where  $V_{CT1}$  and  $V_{CT2}$  are the steady-state average voltages across the capacitors  $C_{T1}$  and  $C_{T2}$ ;  $V_{in}$  and  $V_{out}$  are steady-state average input and output voltages, respectively;  $d'_1$  and  $d'_2$  are the duty cycles of the primary-side auxiliary switch  $(S_{P2})$  and secondary-side auxiliary switch  $(S_{S2})$ . These duty cycles  $d'_1 = 1 - d_1$  and  $d'_2 = 1 - d_2$  are complementary of the main switches. The  $V_{Ca1}$  and  $V_{Cb}$  are respectively steady-state average voltages across capacitors  $C_{a1}$  and  $C_{b1}$  over a switching period.

The duration of the phase-shift between the primary and secondary gate signals is  $\Delta_{\emptyset} T_{sw}$ .

Per Fig. 2.8 to Fig. 2.23, the current flowing into the switch  $S_{P1}$  branch is defined as  $i_1(t)$  and the one flowing through switch  $S_{S1}$  branch is defined as  $i_2(t)$ . These currents can be determined per KCL with reference to Fig. 2.8 as follows:

$$i_1(t) = i_{L1}(t) - i_{Leq}(t)$$

(2.5)

$$i_2(t) = i_{L2}(t) + i_{Leq}(t).$$

(2.6)

where  $i_{L1}(t)$  and  $i_{L2}(t)$  are the instantaneous currents through the input and output inductors, respectively, and  $i_{Leq}(t)$  is the instantaneous current through the equivalent inductor  $L_{eq}$ . Furthermore,  $v_1(t)$  and  $v_2(t)$  are the voltages across the main switches  $S_{P1}$  and  $S_{S1}$ .

Eight (8) forward modes describe the operation of the converter: four (4) main operating modes (M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>, and M<sub>4</sub>) and four (4) transition modes (T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, and T<sub>4</sub>) as depicted in Fig. 2.8 to Fig. 2.23 [6], [7]. Each mode for forward operation of the proposed Ćuk converter is analyzed below [6], [7].

## Main operating mode M<sub>1</sub>

At time  $t_0$ , main switch  $S_{P1}$  is OFF (see transition mode  $T_4$ ) and current  $i_1(t)$  is flowing through the body diode of the auxiliary switch  $S_{P2}$  because  $i_{P2}(t)$  is negative, and auxiliary switch  $S_{S2}$  is already conducting. Switch  $S_{P2}$  is turning ON at ZVS before current  $i_1(t)$  becomes positive. The drain-to-source current of  $S_{P2}$ ,  $i_{P2}(t)$  is equal to  $-i_1(t)$ . Fig. 2.8 illustrates the current paths of the main operating mode  $M_1$  through the interval  $t_0 < t < t_1$ . The voltage across the inductor  $L_{eq}$  is given by  $[V_{CT} + V_{CT} - V_{Ca1} - V_{Cb1}]$  since the switches  $S_{P2}$  and  $S_{S2}$  are active. The current  $i_{Leq}(t)$  increasing linearly is then defined as follows:

$$i_{Leq}(t) = \frac{V_{CT1} + V_{CT2} - V_{Ca1} - V_{Cb1}}{Leq} (t - t_0) + i_{Leq}(t_0).$$

(2.7)

At time  $t_1$ , main operating mode  $M_1$  ends by turning OFF auxiliary switch  $S_{S2}$ . This mode's duration,  $T_{M1}$ , is calculated as follows [6]:

$$T_{M1} = t_1 - t_0 = \Delta_{\emptyset} T_{sw} - (T_{T1} + T_{T4})/2 \tag{2.8}$$

where  $T_{T1}$  and  $T_{T4}$  are the durations of the transition modes  $T_1$  and  $T_4$ , respectively. Fig. 2.9 presents the current  $i_{Leq}(t)$  during this main operating mode  $M_1$ .

Fig. 2.8: Main operating mode 1 [ $t_0$  - $t_1$ ]:  $M_1$ .

Fig. 2.9: Current through the equivalent inductance  $L_{eq}$  during interval  $t_0$  - $t_1$ .

## *Transition mode T*<sub>1</sub>

This transition mode shown in Fig. 2.10 lasts during interval  $t_1 < t < t_2$ . At time  $t_1$ , auxiliary switch  $S_{S2}$  is turned OFF, so current  $i_2(t)$  is transferred from  $S_{S2}$  to main switch  $S_{S1}$ . As a result, the output capacitance of  $S_{S1}$  ( $C_{oss,S1}$ ) discharges and the output capacitance of  $S_{S2}$  ( $C_{oss,S2}$ ) charges. In order for ZVS turn-ON of  $S_{S1}$ ,  $C_{oss,S1}$  must be completely discharged prior to applying its gate voltage. The end of this mode is signaled by the clamping of  $v_2(t)$  by the body diode of  $S_{S1}$  as a result of the current  $i_2(t)$ . The duration of this transition mode  $T_1$  is given by:

$$T_{T1} = t_2 - t_1 = \frac{\left(C_{oss,S1} + C_{oss,S2}\right)V_{CT2}}{i_2(t_1)}$$

(2.9)

$$i_2(t_1) = (I_{L2} + \Delta I_{L2}) + i_{Leq}(t_1)$$

(2.10)

where  $i_{Leq}(t_1)$  is given by (2.7). Fig. 2.11 displays the current  $i_2(t_1)$  during this transition mode  $T_1$ .

Fig. 2.10: Transition mode 1  $[t_1 - t_2]$ :  $T_1$ .

Fig. 2.11: Current  $i_2(t)$  flowing out of the node voltage  $v_2(t)$  during interval  $t_1$  - $t_2$ .

## Main operating mode M<sub>2</sub>

At time  $t_2$ , main switch  $S_{S1}$  is turning ON at ZVS when current flowing through its body diode of  $S_{S1}$  becomes positive  $(i_{S1}(t) = -i_2(t))$  and auxiliary switch  $S_{P2}$  is already conducting. Fig. 2.12 illustrates the current paths of the main operating mode  $M_2$  during interval  $t_2 < t < t_3$ . The voltage across the inductor  $L_{eq}$  is now  $[V_{CT1} - V_{Ca1} - V_{Cb1}]$ , which depending on the value of  $V_{CT1}$ , might be positive or negative, as auxiliary switch  $S_{P2}$  is also active. The current  $i_{Leq}(t)$  is defined by [6]:

$$i_{Leq}(t) = \frac{V_{CT1} - V_{Ca1} - V_{Cb1}}{Leq} (t - t_2) + i_{Leq}(t_2).$$

(2.11)

At time  $t_3$ , main operating mode  $M_2$  ends by turning OFF auxiliary switch  $S_{P2}$ . This mode's duration,  $T_{M2}$ , is calculated as follows [6]:

$$T_{M2} = t_3 - t_2 = (d'_1 - \Delta_{\emptyset}) T_{sw} - (T_{T2} + T_{T1})/2$$

(2.12)

where  $T_{T2}$  and  $T_{T1}$  are the lengths of the transition modes  $T_2$  and  $T_1$ , respectively. Fig. 2.13 presents the current  $i_{Leq}(t)$  during this main operating mode  $M_2$ .

Fig. 2.12: Main operating mode 2 [ $t_2$ - $t_3$ ]:  $M_2$ .

Fig. 2.13: Current through the equivalent inductance  $L_{eq}$  during interval  $t_2$ - $t_3$ .

## *Transition mode T2*

This transition mode shown in Fig. 2.14 lasts during the interval  $t_3 < t < t_4$ . At time  $t_3$ , auxiliary switch  $S_{P2}$  is turned OFF, so current  $i_1(t)$  is transferred from  $S_{P2}$  to main switch  $S_{P1}$ . As a result, the output capacitance of  $S_{P1}$  ( $C_{oss,P1}$ ) and the output capacitance of  $S_{P2}$  ( $C_{oss,P2}$ ) are discharged and charged, respectively. In order for ZVS turn-ON of  $S_{P1}$ ,  $C_{oss,P1}$  must be completely discharged prior to applying its gate voltage. The end of this mode is signaled by the clamping of  $v_1(t)$  by the body diode of  $S_{P1}$  as a result of the current  $i_1(t)$ . The duration of this transition mode  $T_2$ , and the current  $i_1(t_3)$  are given by:

$$T_{T2} = t_4 - t_3 = \frac{\left(C_{oss,P1} + C_{oss,P2}\right)V_{CT1}}{i_1(t_3)}$$

(2.13)

$$i_1(t_3) = (I_{L1} + \Delta I_{L1}) - i_{Leq}(t_3)$$

(2.14)

where  $i_{Leq}(t_3)$  is given by (2.11). Fig. 2.15 displays the current  $i_1(t_3)$  during this transition mode  $T_2$ .

Fig. 2.14: Transition mode 2  $[t_3 - t_4]$ :  $T_2$ .

Fig. 2.15: Current  $i_1(t)$  flowing into the node voltage  $v_1(t)$  during interval  $t_3$  - $t_4$ .

## Main operating mode M<sub>3</sub>

At time  $t_4$ , main switch  $S_{P1}$  is turning ON at ZVS when current flowing through its body diode of  $S_{P1}$  becomes positive  $(i_{P1}(t) = i_1(t))$ , and main switch  $S_{S1}$  is already conducting. Fig. 2.16 illustrates the current paths of this main operating mode  $M_3$  during interval  $t_4 < t < t_5$ . The voltage across the inductor  $L_{eq}$  is equal to  $[-V_{Ca1} - V_{Cb1}]$ , as switches  $S_{P1}$  and  $S_{S1}$  are ON. The current  $i_{Leq}(t)$  decreasing linearly is defined by:

$$i_{Leq}(t) = \frac{-V_{Ca1} - V_{Cb1}}{Leq} (t - t_4) + i_{Leq}(t_4).$$

(2.15)

At time  $t_5$ , mode M<sub>3</sub> ends by turning OFF  $S_{S1}$ . This mode's duration, T<sub>M3</sub>, is obtained as follows [6]:

$$T_{M3} = t_5 - t_4 = (d_1 - d'_2 + \Delta_{\emptyset}) T_{SW} - (T_{T3} + T_{T2})/2$$

(2.16)

where  $T_{T3}$  and  $T_{T2}$  are the lengths of the transition modes  $T_3$  and  $T_2$ , respectively. Fig. 2.17 presents the current  $i_{Leq}(t)$  during this main operating mode M<sub>3</sub>.

Fig. 2.16: Main operating mode 3 [t<sub>4</sub>-t<sub>5</sub>]: M<sub>3</sub>.

Fig. 2.17: Current through the equivalent inductance  $L_{eq}$  during interval  $t_4$  - $t_5$ .

## Transition mode T<sub>3</sub>

This transition mode shown in Fig. 2.18 lasts during interval  $t_5 < t < t_6$ . At time  $t_5$ , main switch  $S_{S1}$  is turned OFF, so current  $i_{Leq}(t)$  forces the current  $i_2(t)$  to become negative. As a result, the output capacitance of  $S_{S1}$  discharges ( $C_{oss,S1}$ ) and the output capacitance of auxiliary switch  $S_{S2}$  ( $C_{oss,S2}$ ) charges. In order for ZVS turn-ON of  $S_{S2}$ ,  $C_{oss,S2}$  must be completely discharged prior to applying its gate voltage. The end of this mode is signaled by the clamping of voltage  $v_2(t)$  by the body diode of

$S_{52}$  as a result of the current  $i_2(t)$ . The duration of this transition mode  $T_3$ , and the current  $i_2(t_5)$  are calculated by (2.17) and (2.18):

$$T_{T3} = t_6 - t_5 = \frac{\left(C_{oss,S1} + C_{oss,S2}\right)V_{CT2}}{-i_2(t_5)}$$

(2.17)

$$i_2(t_5) = (I_{L2} + \Delta I_{L2}) - i_{Leq}(t_5)$$

(2.18)

where  $i_{Leq}(t_5)$  is given by (2.15). Fig. 2.19 displays the current  $i_2(t_5)$  during this transition mode  $T_3$ .

Fig. 2.18: Transition mode 3 [t<sub>5</sub>-t<sub>6</sub>]: T<sub>3</sub>.

Fig. 2.19: Current  $i_2(t)$  flowing out of the node voltage  $v_2(t)$  during interval  $t_5$  - $t_6$ .

# Main operating mode M<sub>4</sub>

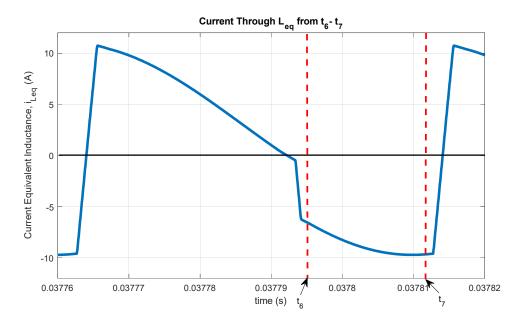

At time  $t_6$ , auxiliary switch  $S_{S2}$  is turning ON at ZVS when current flowing through its body diode of  $S_{S2}$  becomes positive ( $i_{S2}(t) = i_2(t)$ ), and main switch  $S_{P1}$  is already conducting. Fig. 2.20 illustrates the current paths of this main operating mode M<sub>4</sub> during the interval  $t_6 < t < t_7$ . The voltage across the inductor  $L_{eq}$  is equal to  $[V_{CT2} - V_{Ca1} - V_{Cb1}]$  since the switches  $S_{P1}$  and  $S_{S2}$  are active. The current  $i_{Leq}(t)$  is then given by:

$$i_{Leq}(t) = \frac{V_{CT2} - V_{Ca1} - V_{Cb1}}{Leq} (t - t_6) + i_{Leq}(t_6).$$

(2.19)

At time  $t_7$ , mode M<sub>4</sub> ends by turning OFF main switch  $S_{P1}$ . This mode's duration,  $T_{M4}$ , is calculated as follows:

$$T_{M4} = t_7 - t_6 = (d'_2 - \Delta_0) T_{sw} - (T_{T4} + T_{T3})/2$$

(2.20)

where  $T_{T4}$  and  $T_{T3}$  are the durations of the transition modes  $T_4$  and  $T_3$ , respectively. Fig. 2.21 presents the current  $i_{Leq}(t)$  during this main operating mode M<sub>4</sub>.

Fig. 2.20: Main operating mode 4 [ $t_6$  - $t_7$ ]:  $M_4$ .

Fig. 2.21: Current through the equivalent inductance  $L_{eq}$  during interval  $t_6$  - $t_7$ .

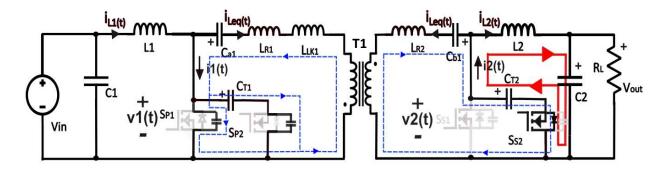

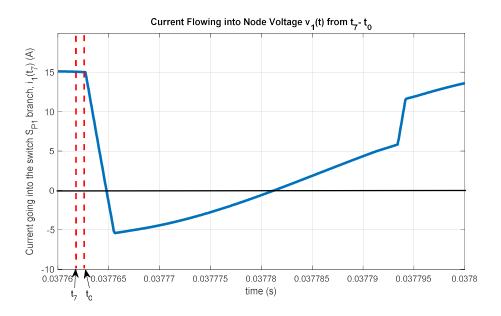

# *Transition mode T*<sub>4</sub>

This transition mode shown in Fig. 2.22 occurs within the interval  $t_7 < t < t_0 + T_{sw}$ . At time  $t_7$ , main switch  $S_{P1}$  is turned OFF, so current  $i_1(t)$  is transferred from  $S_{P1}$  to auxiliary switch  $S_{P2}$ . As a result, the output capacitance of  $S_{P2}$  ( $C_{oss,P2}$ ) and the output capacitance of  $S_{P1}$  ( $C_{oss,P1}$ ) are discharged and charged, respectively. In order for ZVS turn-ON of  $S_{P2}$ ,  $C_{oss,P2}$  must be completely discharged prior to applying its gate voltage. The end of this mode is signaled by the clamping of  $v_1(t)$  by  $S_{P2}$ 's body diode as a result of the current  $i_1(t)$ . The duration of this transition mode  $T_4$  and the current  $i_1(t_7)$  are given by:

$$T_{T4} = t_0 + T_{sw} - t_7 = \frac{\left(C_{oss,P1} + C_{oss,P2}\right)V_{CT1}}{-i_1(t_7)}$$

(2.21)

$$i_1(t_7) = (I_{L1} + \Delta I_{L1}) - i_{Leq}(t_7)$$

(2.22)

where  $i_{Leq}(t_7)$  is given by (2.19). Fig. 2.23 displays the current  $i_1(t_7)$  during this transition mode  $T_4$ .

Fig. 2.22: Transition mode 4 [t<sub>7</sub> -t<sub>0</sub>]: T<sub>4</sub>.

Fig. 2.23: Current  $i_1(t)$  flowing into the node voltage  $v_1(t)$  during interval  $t_7$ - $t_0$ .

# 2.5 System Analysis

A simplified model of the Ćuk converter as a primary referred circuit is considered to carry out a simple analysis of the power transfer, circulating current, and ZVS due to the need for series inductor current states. This model is depicted in Fig. 2.24.

The transition modes (T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, and T<sub>4</sub>) are active for very brief periods of time when compared to the main operating modes (M<sub>1</sub>, M<sub>2</sub>, M<sub>3</sub>, and M<sub>4</sub>). Therefore, the transition modes can be disregarded in power flow and circulating current analyses, which are crucial aspects of this topology.

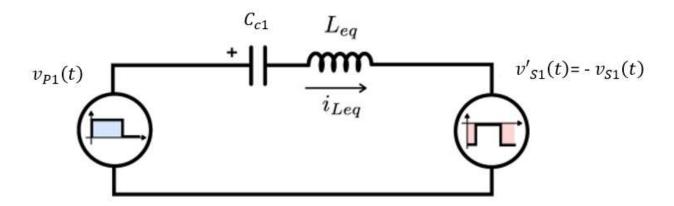

Fig. 2.24: Simplified primary-referred circuit of the isolated Ćuk converter [6], [7].

The node voltage  $v_{S1}(t)$  referred to the primary side is represented by  $v'_{S1}(t)$ . The capacitor  $C_{c1}$  is the equivalent of  $C_{a1}$  and  $C_{b1}$  that are connected in series. The magnetizing inductance  $L_m$  is disregarded in the circuit because  $L_m >> L_{eq}$  [6], [7]. Components  $L_{eq}$  and  $C_{c1}$  are subjected to node voltages  $v_{P1}(t)$  and  $v'_{S1}(t)$ . Volatges  $V_{in}$  and  $-V_{out}$ , the corresponding DC components of  $v_{P1}(t)$  and  $v'_{S1}(t)$ , respectively, are blocked by  $C_{c1}$ .

## 2.5.1 Power transfer

The output power of this simplified converter is given by:

$$P_{out} = \frac{1}{T_{sw}} \int_0^{T_{sw}} v'_{S1,ac}(t) i_{Leq}(t) dt$$

(2.23)

where  $v'_{S1,ac}(t)$  is the ac equivalent of the dc node voltage  $v'_{S1}(t)$  and  $i_{Leq}(t)$  is the current through the equivalent inductor. The powers transferred within each main mode are obtained from (2.23) and given as follows [6], [7]:

$$P_{1} = \frac{V_{CT1}V_{CT2}d_{1}d_{2}T_{sw}}{2L_{eq}}\Delta_{\emptyset}(d'_{1} - \Delta_{\emptyset})$$

(2.24)

$$P_{2} = \frac{V_{CT_{1}}V_{CT_{2}}d_{1}d'_{2}T_{sw}}{2L_{eq}}\Delta_{\emptyset}(d'_{1} - \Delta_{\emptyset})$$

(2.25)

$$P_{3} = \frac{V_{CT1}V_{CT2}d'_{1}d'_{2}T_{sw}}{2L_{eq}}(d'_{2} - \Delta_{\emptyset})(d_{2} - d_{1} + \Delta_{\emptyset})$$

(2.26)

$$P_4 = \frac{V_{CT1}V_{CT2}d'_1d_2T_{sw}}{2L_{eq}}(d'_2 - \Delta_{\emptyset})(d_2 - d_1 + \Delta_{\emptyset}). \tag{2.27}$$

Calculating the total power transferred under steady state over a switching cycle involves replacing the capacitor voltages from (2.2) and (2.3) into the power equations given above and yielding:

$$P_{out} = \frac{V_{in}V_{out}T_{sw}}{2L_{eq}} \left(2\Delta_{\emptyset} + (d_1 + d_2 - 1) - \frac{\Delta^2_{\emptyset}}{d'_1d'_2}\right). \tag{2.28}$$

Equation (2.28) demonstrates that the power transferred depends on the three control parameters on which this converter's modulation techniques are based.

### 2.5.2 Circulating current

As previously mentioned, the ZVS turn-ON of all switches requires a circulating current through  $L_{eq}$ . To ensure ZVS, the circulating current should be limited to decrease conduction losses, so one may quantify this current by taking the mean square of  $i_{Leq}(t)$  over a switching cycle. In addition, conduction losses are proportional to  $I^2_{L,RMS}$  and also present due to the parasitic resistive components in  $i_{Leq}(t)$ . This mean square of  $i_{Leq}(t)$  can be computed in each main operating mode as follows [6], [7]:

$$I^{2}_{L,RMS} = \frac{1}{T_{sw}} \sum_{i=1}^{4} \int_{t_{i-1}}^{t_{i}} i^{2}_{Leq}(t) dt$$

(2.29)

and

$$i_{Leq}(t) = m_i(t - t_{i-1}) + i_{Leq}(t_{i-1})$$

(2.30)

where i is the index of the main operating modes,  $m_i$  is the slope of the current, and  $i_{Leq}(t_{i-1})$  is the initial condition of the current at the start of the ith mode [6], [7]. Table 2.1 summarizes the calculations of the slopes and initial conditions of the current.

The total mean square current over a switching cycle is given by:

$$I^{2}_{L,RMS} = \left(\frac{T_{sw}}{L_{eq}}\right)^{2} \left\{ \begin{aligned} &\frac{V_{out}(12V_{in}\Delta^{2}_{\emptyset} + V_{out})}{12} + \frac{V_{in}d_{1}^{2}(V_{in} + 4V_{out})}{12} \\ &+ \frac{V_{in}d'_{2}^{2}(4V_{in} + V_{out})}{12} - \frac{V_{out}d'_{2}(V_{out} + 6V_{in}\Delta_{\emptyset})}{6} \\ &- \frac{V_{in}V_{out}\Delta_{\emptyset}^{3})}{3d'_{2} - 3d_{1}d'_{2}} - \frac{V_{in}V_{out}d_{1}(3d'_{2} - 6\Delta_{\emptyset} + 1)}{6} \end{aligned} \right\}. \tag{2.31}$$

Table 2.1: Series Inductor Current for Each Main Operating Mode [6], [7]

| Main           | Slope of $i_{Leq}(t)$ for the <i>i</i> th | Initial current at the start of the <i>i</i> th mode                 |

|----------------|-------------------------------------------|----------------------------------------------------------------------|

| Mode           | mode                                      |                                                                      |

| $M_1$          | $m_1 = (V_{CT1}d_1 + V_{CT2}d_2)/L_{eq}$  | $i_{Leq}(t_0) = (-0.5d_1d'_1V_{CT1} - 0.5d_2d'_2V_{CT2})$            |

|                |                                           | $+ (d'_2 - \Delta_{\emptyset})d_2V_{CT2})T_{sw}/L_{eq}$              |

| M <sub>2</sub> | $m_2 = (V_{CT1}d_1 - V_{CT2}d'_2)/L_{eq}$ | $i_{Leq}(t_1) = (-0.5d_1d'_1V_{CT1} + \Delta_{\emptyset}d_1V_{CT1})$ |

|                |                                           | $+ 0.5 d_2 d'_2 V_{CT2}) T_{sw} / L_{eq}$                            |

| M <sub>3</sub> | $m_3 = (-V_{CT1}d'_1)$                    | $i_{Leq}(t_2) = (0.5d_1d'_1V_{CT1} + 0.5d_2d'_2V_{CT2} - (d'_1))$    |

|                | $-V_{CT2}d'_2)/L_{eq}$                    | $-\Delta_{\emptyset})d'_{2}V_{CT2})T_{sw}/L_{eq}$                    |

| M <sub>4</sub> | $m_4 = (-V_{CT1}d'_1)$                    | $i_{Leq}(t_3) = (0.5d_1d'_1V_{CT1} - (d_1 - d'_2))$                  |

|                | $+V_{CT2}d_2)/L_{eq}$                     | $+ \Delta_{\emptyset}) d'_{1} V_{CT}$                                |

|                |                                           | $-0.5d_2d'_2V_{CT2})T_{sw}/L_{eq}$                                   |

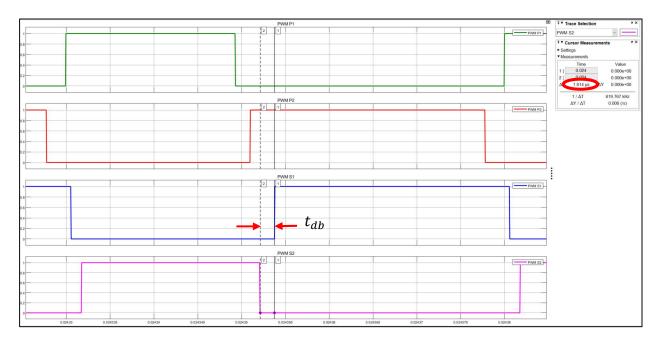

### 2.5.3 ZVS operation

The output capacitance ( $C_{oss}$ ) of the ZVS turn-ON switch must be fully discharged and the  $C_{oss}$  of the ZVS turn-OFF switch must be fully charged within the deadband  $t_{db}$  [8], [9]. The  $C_{oss}$  and  $t_{db}$  between the gates of the complementary switches are considered constants. To gain complete ZVS turn-ON of the switches, the deadband  $t_{db}$  between the complementary switches needs to be longer than the switching transition duration. The switch's minimum allowable threshold current,  $i_{ZVS,min}$ , which allows the switches to charge and discharge their output capacitances within  $t_{db}$ , is calculated as follows [6], [7]:

$$i_{ZVS,min} = \frac{2C_{oss}V_{DS}}{t_{dh}} \tag{2.32}$$

where  $V_{DS}$  represents the voltage across the switch that is turning OFF.

In Table 2.2, where  $i_{Leq}(t_i)$  at the time of transition is taken from Table 2.1, the criteria on the current  $i_{Leq}(t)$  that must be met to ensure that there is sufficient current flowing through the switches at the point of transition for ZVS to turn ON are provided.

From an analysis of Table 2.2, the ZVS turn-ON of  $S_{P1}$  and  $S_{S2}$  switches requires proper selection of the control parameters  $d_1$ ,  $d_2$ , and  $\Delta_{\emptyset}$ , whereas the conditions for the other two

Table 2.2: Conditions of  $i_{Leq}(t)$  to Ensure ZVS Turn-ON

| ZVS on the switches | Conditions of $i_{Leq}(t)$                                            |

|---------------------|-----------------------------------------------------------------------|

| ZVS on $S_{P1}$     | $i_{Leq}(t_2) > (I_{in} - \Delta I_{in}) + 2C_{oss}V_{CT1}/t_{db}$    |

| ZVS on $S_{P2}$     | $i_{Leq}(t_0) < (I_{in} + \Delta I_{in}) - 2C_{oss}V_{CT1}/t_{db}$    |

| ZVS on $S_{S1}$     | $i_{Leq}(t_1) > -(I_{out} + \Delta I_{out}) + 2C_{oss}V_{CT2}/t_{db}$ |

| ZVS on $S_{S2}$     | $i_{Leq}(t_3) < -(I_{out} - \Delta I_{out}) - 2C_{oss}V_{CT2}/t_{db}$ |

switches are generally easily satisfied. Equations (2.33) and (2.34) provide the conditions for ZVS turn-ON of  $S_{P1}$  and  $S_{S2}$  switches, respectively [6], [7]:

$$d_{1,ZVS(P1)} > \frac{\left(\frac{G}{L_{eq}}\left(1 - \frac{\Delta^{2}_{\emptyset}}{d'_{1}d'_{2}}\right)\right) + \frac{4C_{oss}}{d'_{1}t_{db}T_{sw}}}{\left(\frac{G+1}{L_{eq}} + \frac{1}{L_{1}}\right)}$$

(2.33)

$$d_{2,ZVS(S2)} > \frac{\left(\frac{1}{L_{eq}} \left(1 - \frac{\Delta^2_{\phi}}{d'_1 d'_2}\right)\right) + \frac{4C_{oss}}{d'_2 t_{db} T_{sw}}}{\left(\frac{G+1}{L_{eq}} + \frac{G}{L_2}\right)}$$

(2.34)

where G is the converter gain  $V_{out}/V_{in}$ . The ZVS boundary conditions of (2.33) decreases while (2.34) increases when G increases.

# 2.6 Concluding Remarks

In Chapter 2, the theoretical aspects of the isolated bidirectional Ćuk dc-dc converter topology are explored, providing readers the knowledge needed to comprehend the converter's forward mode of operation. The reader can thus better understand simulation and experimental results through the various modes of operation.

Chapter 3 intends to assist readers in beginning their own designs by guiding them to establish the system parameters and run simulations using MATLAB/Simulink<sup>TM</sup>. In this chapter, a quantitative analysis is performed to interpret the operation of the converter by collecting and evaluating measurable and verifiable data through simulations.

### 2.7 References

[1] Technology, E. (2022). What is a CUK converter and how it works? Circuit & Operation, *ELECTRICAL TECHNOLOGY*. Available: https://www.electricaltechnology.org/2021/09/cuk-converter.html. (Accessed: Nov. 10, 2022).

- [2] S. Ćuk, "A New Zero-Ripple Switching DC-to-DC Converter and Integrated Magnetics," *IEEE Trans. Magn.*, vol. 19, no. 2, pp. 57-75, 1983, doi: 10.1109/TMAG.1983.1062238.

- [3] S. Ćuk and R. D. Middlebrook, "A new optimum topology switching DC-to-DC converter," *1977 IEEE Power Electronics Specialists Conference*, 1977, pp. 160-179, doi: 10.1109/PESC.1977.7070814.

- [4] A. Ramanath, "Design, Implementation, Control and Performance Analysis of Coupled Inductor Ćuk Converter," M.S. thesis, The Univ. of Minnesota, Minnesota, US, Apr. 2020. [Online]. Available: https://conservancy.umn.edu/bitstream/handle/11299/220575/Ramanath\_umn\_0130M\_21 185.pdf?sequence=1

- [5] I. I. Rahman, D. C. Riawan and M. Ashari, "Design and Implementation of DC-DC Bidirectional Ćuk Converter with Average Current Mode Control for Lead Acid Battery Testing," 2019 International Seminar on Intelligent Technology and Its Applications (ISITIA), 2019, pp. 183-188, doi: 10.1109/ISITIA.2019.8937200.

- [6] S. Gupta and S. K. Mazumder, "A Novel Modulation Scheme for Isolated PWM Active-Clamp Ćuk DC/DC Converter," *IEEE Trans. Power Electron.*, vol. 37, no. 12, pp. 14966-14980, Dec. 2022, doi: 10.1109/TPEL.2022.3189672.

- [7] S. Gupta and S. K. Mazumder, "Analysis of Resonant PWM Active-clamp Ćuk DC/DC Converter," *Applied Power Electronics Conference*, APEC 2023, doi: 978-1-6654-7539-6/23/\$31.00.

- [8] M. Kasper, R. M. Burkart, G. Deboy, and J. W. Kolar, "ZVS of power MOSFETs revisited," IEEE Trans. Power Electron., vol. 31, no. 12, pp. 8063–8067, Dec. 2016, doi: 10.1109/TPEL.2016.2574998.

- [9] S. Gupta and S. K. Mazumder, "Hysteresis based triangular current mode control for bridgeless totem pole converter," *Proc. IEEE 12th Int. Symp. Power Electron. Distrib. Gener. Syst.*, Jun. 2021, pp. 1–7, doi: 10.1109/PEDG51384.2021.9494197.

#### **CHAPTER 3**

# DESIGN AND SIMULATIONS OF ISOLATED BIDIRECTIONAL ĆUK CONVERTER

## 3.1 Introduction

The previous chapter presented the theoretical analysis of the isolated bidirectional Ćuk dc-dc converter topology. Chapter 3 focuses on the design and simulations of the Ćuk dc-dc converter utilizing MATLAB/Simulink<sup>TM</sup>. The main objective of this chapter is to explain the process for designing and developing the circuit model to run simulations validating the knowledge gained in Chapter 2. The main specifications of this converter are an input voltage of 300 V, output voltage of 213 V, rated output power of 1.5 kW, and switching frequency of 20 kHz.

The structure of this chapter is organized as follows: Section 3.2 addresses an overview of the selection of the hardware components and control parameters. Section 3.3 presents the procedure used for designing the Ćuk-based dc-dc prototype. Section 3.4 discusses the components used in the circuit and the implementation of the control algorithm in MATLAB/Simulink<sup>TM</sup>. Moreover, a quantitative analysis is carried out to verify the proper function of the converter by gathering and evaluating measurable data using the simulation results. Then, Section 3.5 provides a summary of the accomplishments of this entire chapter and describes the goals of the following chapter.

# 3.2 Determining System Parameters

## 3.2.1 Hardware design

It is evident that active and passive components are necessary for power transfer, minimizing circulating current, and achieving ZVS conditions. Thus, proper selection of the

active and passive components depending on the control parameter range is important. In particular:

MOSFET selection: The maximum voltage across the auxiliary capacitors  $C_{T1}$  and  $C_{T2}$  determines the voltage ratings of the main and auxiliary switches on the primary and secondary sides since these are clamped by these auxiliary capacitors. Equations (2.2) and (2.3) determine the value of the maximum voltage across the primary and secondary main and auxiliary switches of the converter, respectively. Ideally, the maximum voltage across the switch is given by the sum of the input and output voltages. From the turn-OFF currents through the switches  $S_{P1}$ ,  $S_{P2}$ ,  $S_{S1}$ , and  $S_{S2}$  at the end of the main operating modes  $M_1$  and  $M_2$ , the absolute peak currents through these switches can be determined as follows:

$$I_{P1,max} = I_{P2,max} = \left| (I_{in} + \Delta I_{in}) - i_{Leq,max}(t_0) \right|$$

(3.1)

$$I_{S1,max} = I_{S2,max} = |(I_{out} + \Delta I_{out}) + i_{Leq,max}(t_1)|.$$

(3.2)

where  $I_{in}$  and  $I_{out}$  are the mean input and output current values, respectively;  $\Delta I_{in}$  and  $\Delta I_{out}$  are neglected because the input and output inductors are coupled in an Integrated Magnetic (IM) structure to achieve zero inductor current ripple; and  $i_{Leq,max}(t_0)$  and  $i_{Leq,max}(t_1)$  are calculated using KCL in the circuit.

Equivalent series inductance,  $L_{eq}$ : Due to the fact that both power transfer and circulating current are inversely proportional to  $L_{eq}$ , this inductance is crucial for the ZVS turn-ON of the switches, where (2.28) and (2.31) play a crucial role. For ZVS under turn-ON conditions, the designer must choose an inductance that can handle the smallest amount of load required. According to [1] and [2], increasing  $L_{eq}$  decreases the output power and mean square circulating current per Watt. Equation (3.3) represents the minimum condition for  $L_{eq}$  and is obtained as:

$$L_{eq} > \frac{V_{in}V_{out}T_{sw}}{2P_{min}} \left(2\Delta_{\emptyset} + d_{1,ZVS} + d_{2,ZVS} - 1 - \frac{\Delta^{2}_{\emptyset}}{d'_{1,ZVS}d'_{2,ZVS}}\right)$$

(3.3)

where  $P_{min}$  is the minimum required output load and  $d_{1,ZVS}$  and  $d_{2,ZVS}$  are the expressions for the ZVS boundary turn-ON of  $S_{P1}$  and  $S_{S2}$  switches given in (2.33) and (2.34) for a constant phase-shift  $\Delta_{\emptyset}$ .

Input and output inductors,  $L_1$  and  $L_2$ : The ripple requirements are considered while selecting these inductors when designing a typical Ćuk converter. ZVS boundary limitations, however, show that larger inductor current ripple over the inductors is preferable to help with ZVS operation [1], [2]. However, for our purpose, the input and output inductors are connected in an Integrated magnetics (IM) structure to accomplish zero inductor current ripple.

Auxiliary capacitors,  $C_{T1}$  and  $C_{T2}$ : Both capacitors are selected to ensure that the circuit formed by the auxiliary and blocking capacitors and  $L_{eq}$  has a resonance period significantly longer than the main operating modes  $M_2$  and  $M_4$ , respectively. The following conditions can be applied to choose the value of the auxiliary capacitors  $C_{T1}$  and  $C_{T2}$ :

$$(1 - d_{1,max} - \Delta_{\emptyset}) T_{sw} \ll 2\pi \sqrt{L_{eq} (C_{T1} || C_{a1} || C_{b1})}$$

(3.4)

$$(1 - d_{2,max} - \Delta_{\emptyset}) T_{sw} \ll 2\pi \sqrt{L_{eq} (C_{T2} || C_{a1} || C_{b1})}$$

(3.5)

where  $d_{1,max}$  and  $d_{2,max}$  are the maximum duty cycles limited by the capacitor and switch voltage ratings [1], [2].

## 3.2.2 Control parameters

As mentioned in Chapter 2, the modulation techniques of the analyzed Cuk converter are based on three control parameters:  $d_1$ ,  $d_2$ , and  $\Delta_{\emptyset}$ . Depending on the required purpose, one can

choose the parameters for a certain operation. The objective of this study is to lower the circulating current by optimizing the duty cycles  $d_1$  and  $d_2$  for a constant phase-shift ratio [1], [2].

<u>Phase-shift ratio</u>,  $\Delta_{\phi}$ : The circulating current is caused by the phase difference produced by the two duty cycles, which helps in achieving ZVS turn-ON of the switches. Following the ideas in [1] and [2], a small fixed phase-shift ratio of 0.09 is selected.

<u>Duty cycles</u>,  $d_1$  and  $d_2$ : The minimum duty cycles are limited by the ZVS boundary given in (2.33) and (2.34) while the maximum duty cycles are restrained by the voltage rating of the switches and the auxiliary capacitors given by (2.2) and (2.3).

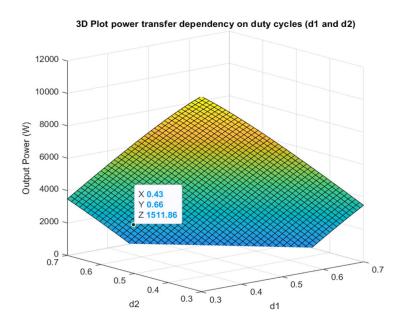

Assuming a constant  $\Delta_{\emptyset}$  of 0.09 [6], Fig. 3.1 presents a 3-D plot of power transferred to the output as a function of the control parameters (d<sub>1</sub> and d<sub>2</sub>). The data point on Fig. 3.1 represents the values of  $x = d_1$  and  $y = d_2$  for an output power of z = 1511.86 W used for the design carried out in this thesis.

Fig. 3.1: Three-dimensional plot showing power transfer dependency on duty cycles ( $d_1$  and  $d_2$ ) for  $V_{in}$ = 300 V,  $V_{out}$ = 213 V,  $L_{eq}$ = 69  $\mu$ H and  $\Delta_{\emptyset}$ = 0.09.

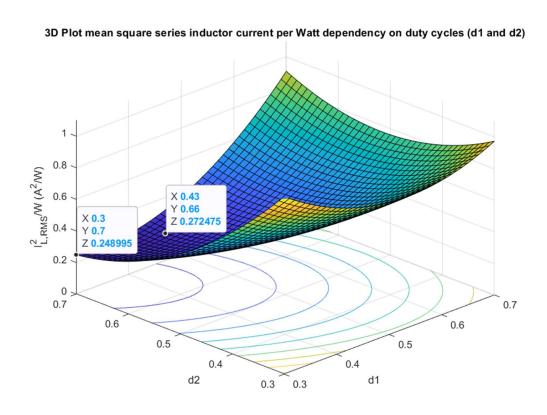

To further grasp the connection between the circulating current and the control parameters, Fig. 3.2 shows the mean square current of the series inductor normalized by power transferred and dependency on the duty cycle of main switch  $S_{P1}$ ,  $d_1$  and duty cycle of main switch  $S_{S1}$ ,  $d_2$  for a constant phase-shift ratio  $\Delta_{\emptyset}$  of 0.09. By optimizing the three control parameters, it is possible to determine the minimum current for the required output power from the convex shape of the plot. The data point on Fig. 3.2 represents the approximation values of  $x = d_1 = 0.43$ ,  $y = d_2 = 0.66$  and z = 0.2725 A<sup>2</sup>/W used to get an idea of the conduction losses for the design. The value of z is very close to its minimum value of 0.249 A<sup>2</sup>/W corresponding to  $d_1 = 0.3$  and  $d_2 = 0.7$ .

Fig. 3.2: Three-dimensional plot of the mean square series inductor current per Watt dependency on duty cycles ( $d_1$  and  $d_2$ ) for  $V_{in}$ = 300 V,  $V_{out}$ = 213 V,  $L_{eq}$ = 69  $\mu$ H and  $\Delta_{\emptyset}$ = 0.09.

# 3.3 Design Process of the Isolated Ćuk DC-DC Prototype

The specifications of the design considered in this thesis are:

$$V_{in} = 300 V$$

$V_{out} = 213 V$

$P_{rated} = 1.5 kW$

$T_{sw} = 50 \mu s$

$n = 1$

The following equations are used to determine the design parameters of the isolated Ćuk dc-dc converter:

$$D = \frac{V_{out}/n}{V_{in} + V_{out}/n} \cong 0.43 = d_1 \tag{3.6}$$

$$R_L = \frac{V_{out}^2}{P_{rated}} = \frac{213^2}{1500} \cong 30 \,\Omega$$

(3.7)

Typical values of  $\Delta v_{ripple}$  are 1%, 2%, 5%, 10%, etc. The application determines the specific ripple values. Selecting  $\Delta v_{Ca1} = 5$  % and  $\Delta v_{Cb1} = 5$  % yield:

$$C_{a1} = \frac{V_{out} n DT_{sw}}{2 R_L \Delta v_{Ca1}} = 15.265 \,\mu F \tag{3.8}$$

$$C_{b1} = \frac{V_{out} DT_{sw}}{2 R_L \Delta v_{Cb1}} = 15.265 \,\mu F \tag{3.9}$$

Selecting  $\Delta v_{C2} = 1$  % and having  $L_2 = 620 \,\mu H$ , yields:

$$C_2 = \frac{V_{out} (1 - D) T_{sw}^2}{8 L_2 R_L \Delta v_{C2}} = 3 \mu F$$

(3.10)

Common discrete values for capacitors such as those in [3] lead the designer to select the closest values available in the market to the calculated ones considering voltage and current

handling capacities. As a result, capacitors  $C_{a1}$ ,  $C_{b1}$ , and  $C_2$  are selected to be 15  $\mu F$ , 15  $\mu F$ , and 3  $\mu F$ , respectively.

One can theoretically achieve zero current ripple in both the input and output currents of the dc-dc Ćuk converter by using the IM topology presented in [4], which integrates the transformer, input, and output inductors into a single magnetic structure. The transformer for this prototype was designed by doctoral student David Porras and built by myself for a related project.

Table 3.1 shows the specified and calculated data of the system at rated conditions of 1.5-kW,  $300 \ V_{dc}$  at the input and  $213 \ V_{dc}$  at the output.

Table 3.1: Parameters of the Designed Prototype

| Parameters                                                                           | Value | Unit |

|--------------------------------------------------------------------------------------|-------|------|

| Input voltage (Vin)*                                                                 | 300   | V    |

| Output voltage ( <i>Vout</i> )*                                                      | 213   | V    |

| Output power ( <i>Pout</i> )*                                                        | 1.5   | kW   |

| Switching frequency $(f_{sw})^*$                                                     | 20    | kHz  |

| Voltage ripple across $C_{a1}$ and $C_{b1}$ ( $\Delta v_{Ca1}$ , $\Delta v_{Cb1}$ )* | 5     | %    |

| Voltage ripple across $C_2$ ( $\Delta v_{C2}$ )*                                     | 1     | %    |

| Turns ratio (1:n)*                                                                   | 1     |      |

| Input and output inductors $(L_1 \text{ and } L_2)^*$                                | 620   | μΗ   |

| Load resistance $(R_L)^{\#}$                                                         | 30    | Ω    |

| Duty cycle $(D = d_1)^{\#}$                                                          | 0.43  |      |

| Series capacitors $(C_{a1} \text{ and } C_{b1})^{\#}$                                | 15    | μF   |

| Output Capacitor $(C_2)^{\#}$                                                        | 3     | μF   |

<sup>\*</sup> Input Data, # Calculated Data

Table 3.2 presents the remaining component values used in the converter. SiC MOSFET devices with lower rated voltage could have been used, but these ones were selected for a related project having higher voltage ratings. The gain *G* is calculated as follows:

$$G = \frac{V_{out,rated}}{V_{in,rated}} = 0.71 \tag{3.11}$$

Table 3.2: Other Component Values for the Designed Prototype

| Component Specifications                            | Value       | Unit   |

|-----------------------------------------------------|-------------|--------|

| Input Capacitor $(C_1)$                             | 3           | μF     |

| Primary auxiliary capacitor $(C_{T1})$              | 7.5         | μF     |

| Secondary auxiliary capacitor ( $C_{T2}$ )          | 2.2         | μF     |

| Series resonant inductors ( $L_{R1}$ and $L_{R2}$ ) | 31          | μΗ     |

| Leakage inductors ( $L_{LK1}$ and $L_{LK2}$ )       | 3.6         | μΗ     |

| Equivalent series inductor $(L_{eq})$               | 69          | μΗ     |

| MOSFETs $(S_{P1}, S_{P2}, S_{S1}, S_{S2})$          | C2M0045170D | 1.7 kV |

| Hitachi CC cores for $L_{R1}$ and $L_{R2}$          | F3CC0010    |        |

| Hitachi CC cores for IM                             | AMCC-320    |        |

| Gain (G)                                            | 0.71        |        |

| $\Delta_{\emptyset}$                                | 0.09        |        |

This application could have used 900 V or 1200 V SiC MOSFETs since the theoretical peak voltage across the switches when OFF is 513 V (300 V + 213 V). However, the author of this thesis is leveraging a prototype built for a related project.

# 3.4 MATLAB/Simulink<sup>TM</sup> Simulations

### 3.4.1 Implementation of the circuit schematic

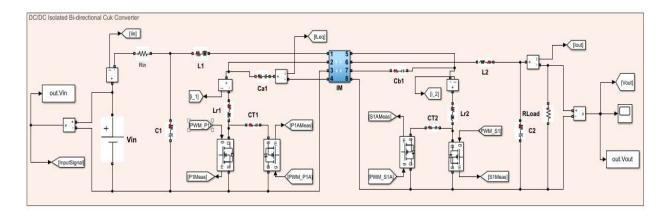

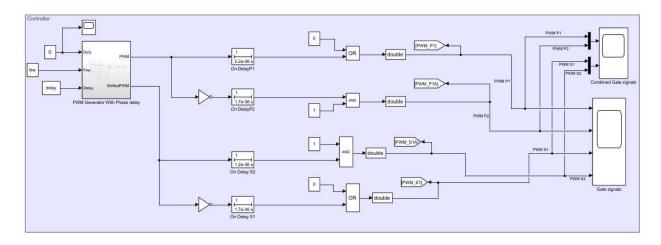

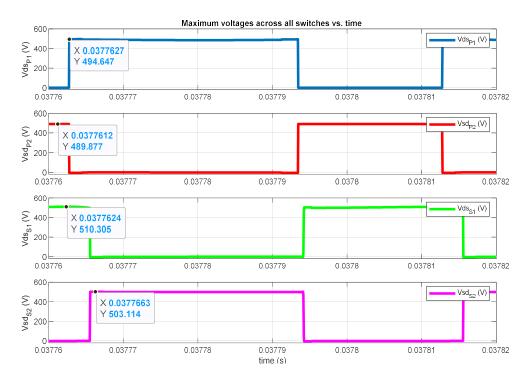

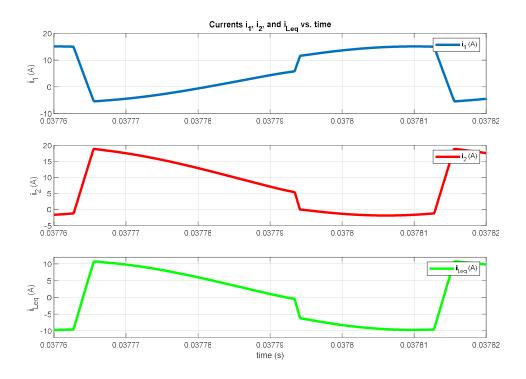

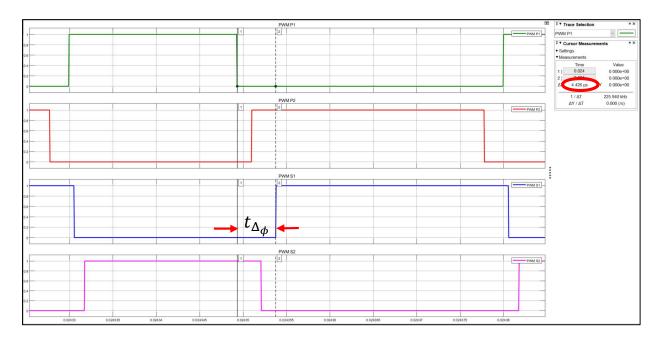

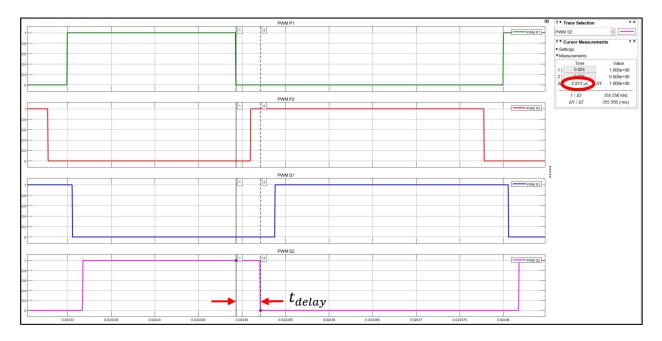

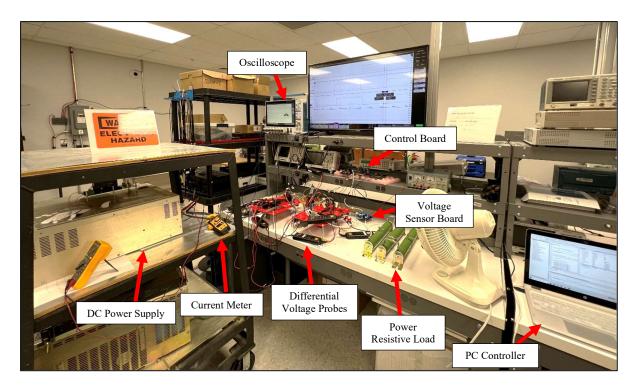

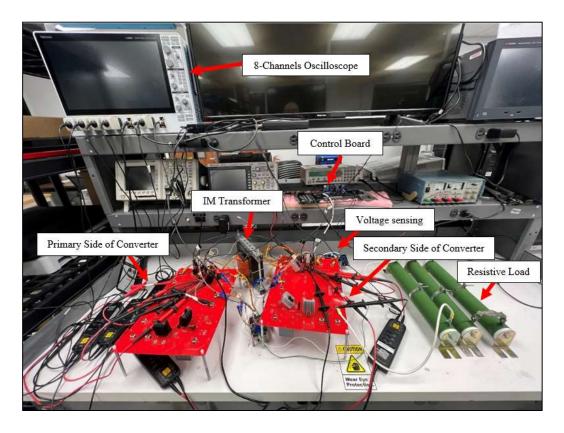

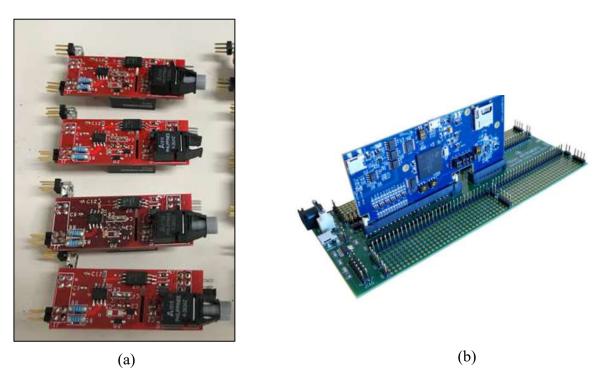

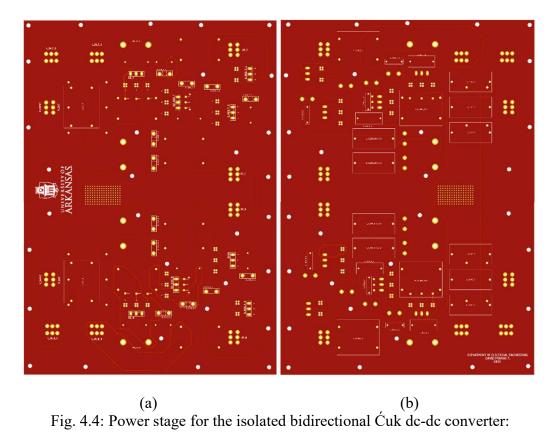

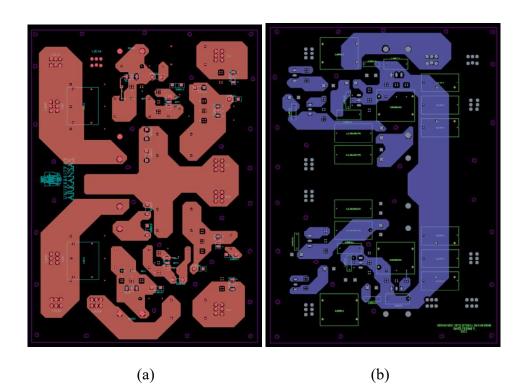

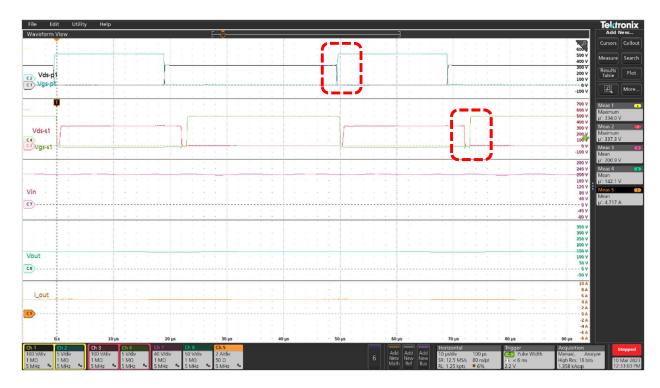

Simulations are performed using the circuit model presented in Fig. 2.7 with all the parameters listed in Tables 3.1 and 3.2.